这篇文章解读一下开发板的第一个demo,这个demo是个点灯demo,通过这个demo可以让小白了解高云开发的基本过程,所以也是非常重要的,如果之前完全没用过高云的产品,通过学习这篇文章可以快速的上手。

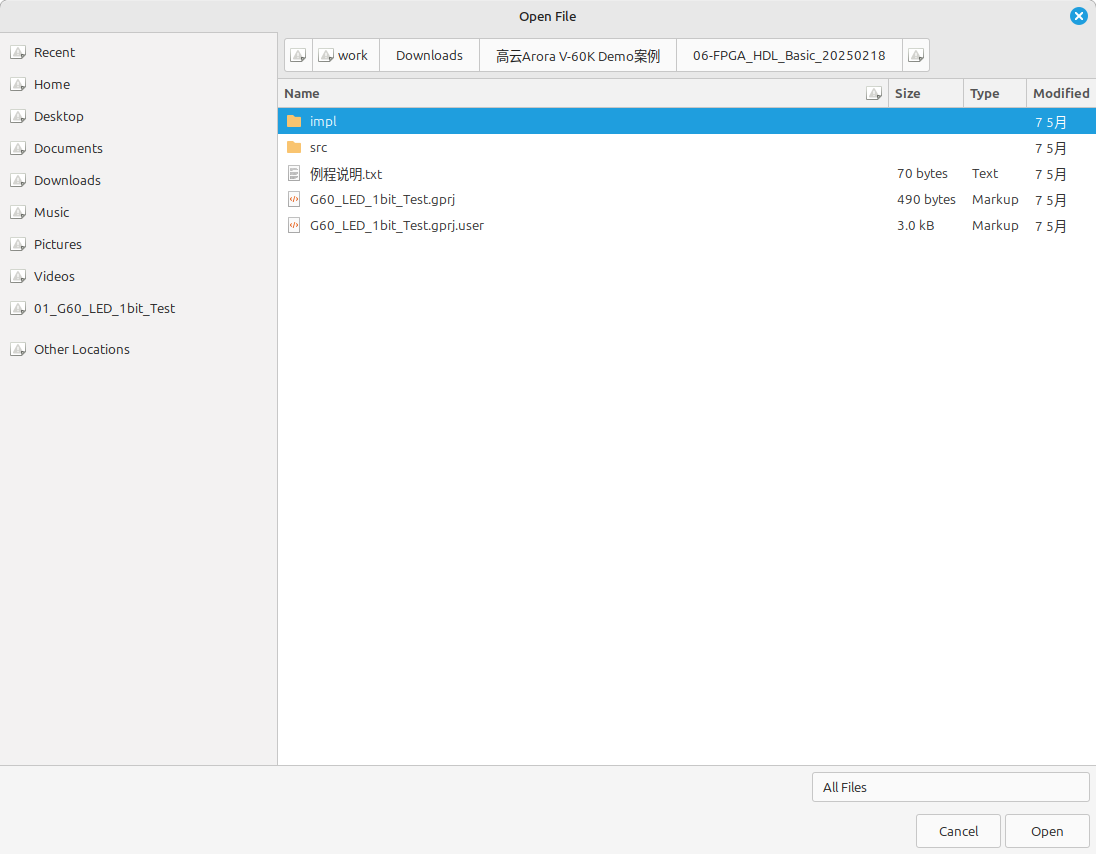

首先咱们打开这个例子的工程。

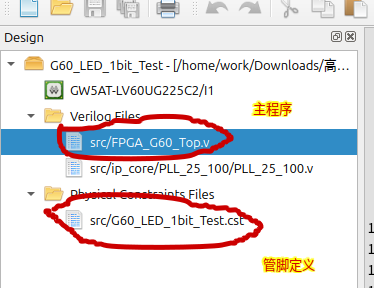

然后我们看左边的代码文件列表,一般有top字样的文件都是程序的入口,大家也应该养好这个习惯。这个工程只有一个文件,所以不会混淆,如果程序文件多了就不知道哪个是入口了。

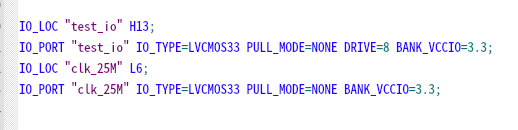

下面那个是管脚定义的文件。有时候我们下载官方的参考范例,或者是从其他型号芯片移植代码过来,最重要的就是修改这个文件。所以第一步我们需要学会看这个文件。

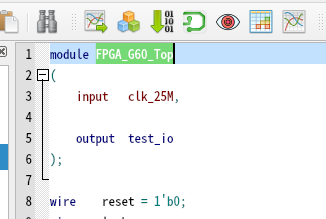

打开主程序文件可以看到这个顶层模块的定义,就两个管脚,一个是输入,一个是输出,看名字我们就知道,输入的是25M的外部时钟信号,另一个管脚应该是接到led灯上的,下面我们通过文档和原理图来确认一下。

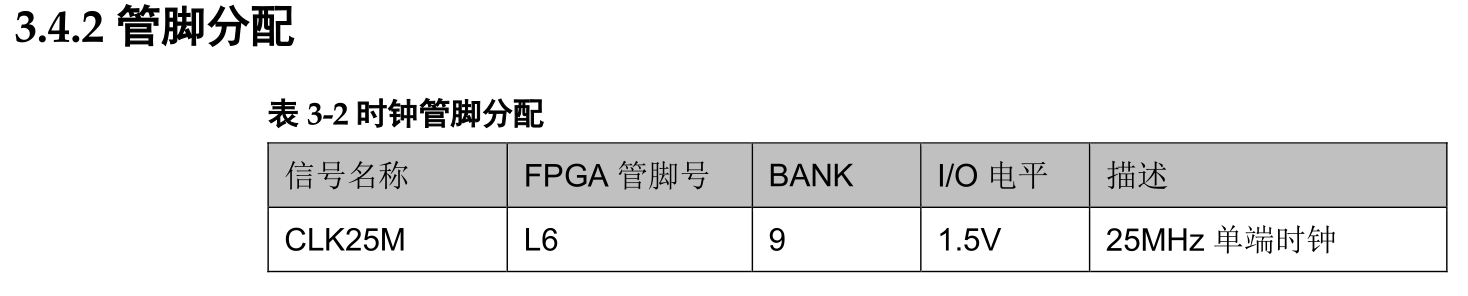

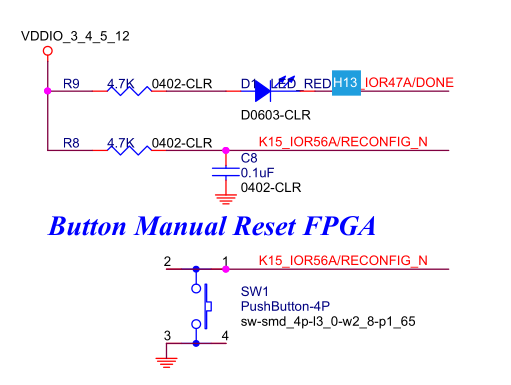

开发板的用户手册里面有介绍外部时钟是接到FPGA的L6管脚上的。

然后打开原理图可以看到H13管脚接到led灯的负极上,当管脚低电平的时候led灯亮,高电平的时候led灯不亮。

然后我们打开管脚定义文件,可以看到跟模块定义那边一样的名字,这两个管脚被定义在管脚定义文件中,这里有指明它们分别是FPGA的H13号管脚和L6号管脚,还有就是它们的IO类型,驱动能力,它们所属的bank的电压。这块如果是硬件工程师就比较好理解,因为这些都是有规范的,也就是可以百度到,所以高云官网的文档其实没有细说,每个FPGA厂家也是通用的。如有迷糊的大家可以在百度上补充一下相关的知识,反正不要被吓到就好。

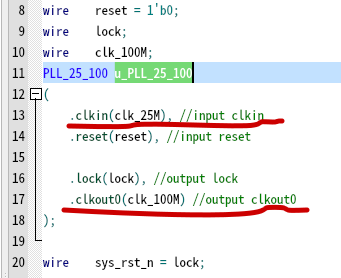

接着我们继续看主程序的代码,这里有个锁相环的使用,大概是把25M的时钟倍频为100M。其实它这个点灯的例子没必要倍频的,可能只是为了让大家多学点东西,故意这么写的。我们可以想象在单片机开发里面经常会通过计数器来把一个高频率的时钟变成低频率的,但是反过来,把低频率的时钟变高就需要锁相环了。在FPGA里锁相环也是一种资源,个数是有限的,所以尽量在一个锁相环里面多输出几个波形。关于锁相环的设置细节可以参考高云的文档,这块他们说得很清楚的。反正我们最后知道后面会针对这个100m的型号继续处理。

这里还有一个细节是锁相环的lock,这个代码的作者应该也是个大神,他喜欢用这个lock来做复位信号。所以我们萌新可以学习一下。后面我们看多了代码会发现复位信号是非常重要的,有些代码跑步起来可能是复位的问题。

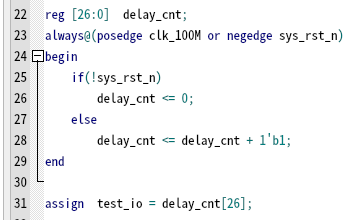

继续往下看代码,随便理解一下刚刚说的复位信号。这里用到Verilog语言里面的always语法,这个大家也不用慌,其实即使没有学过Verilog这里也看得懂,因为点灯这个逻辑大家也应该猜得到,就是把100m的信号通过计数的方式,数到大概一秒钟左右的节拍,这样我们人眼就能看到灯闪烁了。

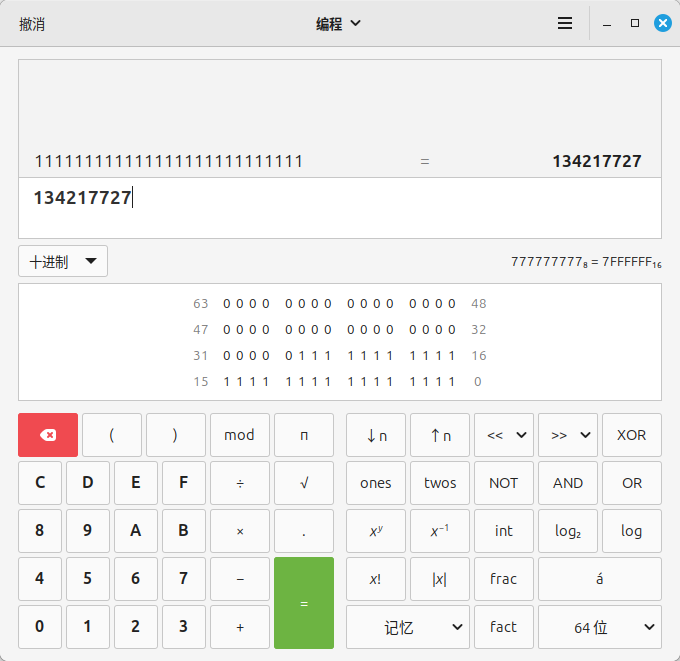

打开计算器我们用二进制点27个1,然后转成10进制,大概是134M这样的数字,也就是说delay_cnt定义的这个27个bit的寄存器数完一轮是134M个波形,一秒有100M个波形,所以它的最高位,也就是26位的那个bit在一秒多一点这样的时间内会翻转一次。也就是我们可以用它来让灯亮灭的闪烁。

最后解释一下复位信号,我们看到代码里面是有个if语句做判断,看这大概可以猜到,是在复位信号有效的时候对计数器清理的操作。上面我们说过复位信号非常重要,在这个例子里即使不复位,也就是代码不走到初始化那块,也不会有什么影响。但是有些比较大的工程,复位这块逻辑是非常重要的,如果不执行,整个程序就不对了。

要理解这点,就是看懂always语言的意义,这里大家可以这么记忆。就是复位信号有效的时候走if语言上面的代码,这个代码的意思是把计数器锁存全零,既然是锁存,那就需要至少100M这个时钟来至少一个clk;当复位信号无效的时候走其他逻辑。

所以结论是复位信号在上电以后必须保持一个clk的有效时间,再变得无效,这样整个程序才能跑正常。有些电路可能会把复位信号接到一个引脚上,然后串上一个电阻和电容跟VCC相连,其实就是保证这个复位逻辑。因为电容在充电时,这个脚是低电平,后面在变高电平。