你好@ mauererm

您是否在设计中正确连接了IP?

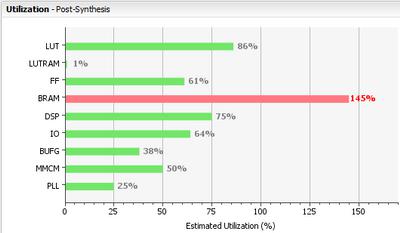

看起来实现工具正在修剪BRAM实例。

请打开已实现的设计,然后转到编辑 - >查找并搜索设计中是否有BRAM类型的单元格。

如果结果为空,则打开合成设计并检查BRAM输入和输出是否在原理图中正确连接。

谢谢,迪皮卡.----------------------------------------------

---------------------------------------------- Google之前的问题

张贴。

如果某人的帖子回答了您的问题,请将帖子标记为“接受为解决方案”。

如果你看到一个特别好的和信息丰富的帖子,考虑给它Kudos(左边的明星)

以上来自于谷歌翻译

以下为原文

Hi @mauererm

Did you connect the IP properly in the design? It looks like implementation tool is trimming the BRAM instances.

Please open implemented design and go to Edit -->find and search if there are any cells of type BRAM in the design. If the results are empty then open synthesized design and check if the BRAM inputs and outputs are connected properly or not in schematic.

Thanks,

Deepika.

--------------------------------------------------------------------------------------------

Google your question before posting. If someone's post answers your question, mark the post as answer with "Accept as solution". If you see a particularly good and informative post, consider giving it Kudos (the star on the left)

你好@ mauererm

您是否在设计中正确连接了IP?

看起来实现工具正在修剪BRAM实例。

请打开已实现的设计,然后转到编辑 - >查找并搜索设计中是否有BRAM类型的单元格。

如果结果为空,则打开合成设计并检查BRAM输入和输出是否在原理图中正确连接。

谢谢,迪皮卡.----------------------------------------------

---------------------------------------------- Google之前的问题

张贴。

如果某人的帖子回答了您的问题,请将帖子标记为“接受为解决方案”。

如果你看到一个特别好的和信息丰富的帖子,考虑给它Kudos(左边的明星)

以上来自于谷歌翻译

以下为原文

Hi @mauererm

Did you connect the IP properly in the design? It looks like implementation tool is trimming the BRAM instances.

Please open implemented design and go to Edit -->find and search if there are any cells of type BRAM in the design. If the results are empty then open synthesized design and check if the BRAM inputs and outputs are connected properly or not in schematic.

Thanks,

Deepika.

--------------------------------------------------------------------------------------------

Google your question before posting. If someone's post answers your question, mark the post as answer with "Accept as solution". If you see a particularly good and informative post, consider giving it Kudos (the star on the left)

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报