开发环境:

IDE:MounRiver Studio

MCU:CH585

1 I2C工作原理

1.1 I2C串行总线概述

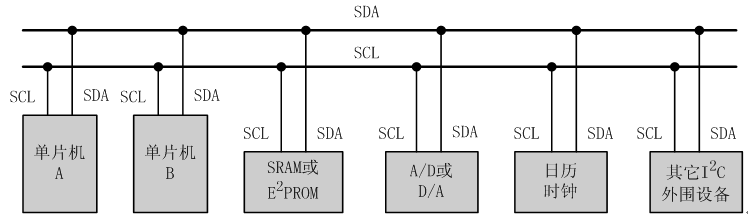

I2C总线是PHLIPS公司推出的一种双线式半双工串行总线,是具备多主机系统所需的总线裁决和高低速器件同步功能的高性能串行总线。用于连接微控器及外围设备。I2C总线只有两根双向信号线。一根是数据线SDA,另一根是时钟线SCL。

1)它只使用两条总线线路 :一条双向串行数据线(SDA),一条串行时钟线(SCL)。见图 1。

2)每个连接到总线的设备都有一个独立的地址,主机可以利用这个地址进行不同设备之间的访问。

3)多主机同时使用总线时,为了防止数据冲突,会利用仲裁方式决定由哪个设备占用总线。

4)具有三种传输模式 :标准模式的传输速率为 100 Kbit/s ,快速模式为 400 Kbit/s ,高速模式下可达 3.4 Mbit/s,但目前大多12C设备尚不支持高速模式。

5)片上的滤波器可以滤去总线数据线上的毛刺波以保证数据完整。

6)连接到相同总线的 IC 数量受到总线的最大电容 400 pF 限制

Figure 1‑1 I2C总线

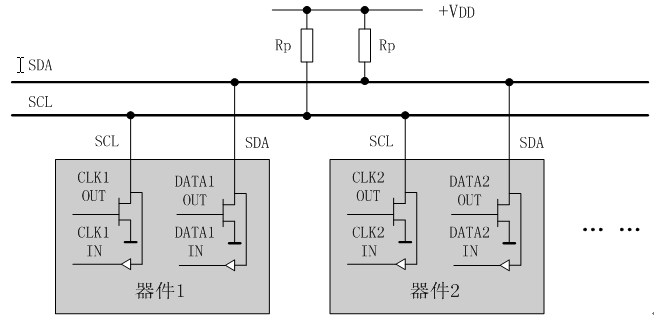

I2C总线通过上拉电阻接正电源。当总线空闲时,两根线均为高电平。连到总线上的任一器件输出的低电平,都将使总线的信号变低,即各器件的SDA及SCL都是线“与”关系。

Figure 1‑2 I2C总线架构

每个接到I2C总线上的器件都有唯一的地址。主机与其它器件间的数据传送可以是由主机发送数据到其它器件,这时主机即为发送器。由总线上接收数据的器件则为接收器。

在多主机系统中,可能同时有几个主机企图启动总线传送数据。为了避免混乱, I2C总线要通过总线仲裁,以决定由哪一台主机控制总线。

I2C的协议包括起始和停止条件、数据有效性、响应、仲裁、时钟同步和地址广播等环节,由于我们使用的是 CH585集成的硬件I2C接口,并不需要用软件去模拟 SDA 和SCL 线的时序。

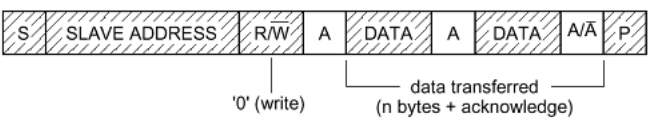

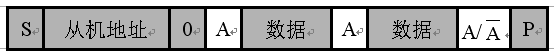

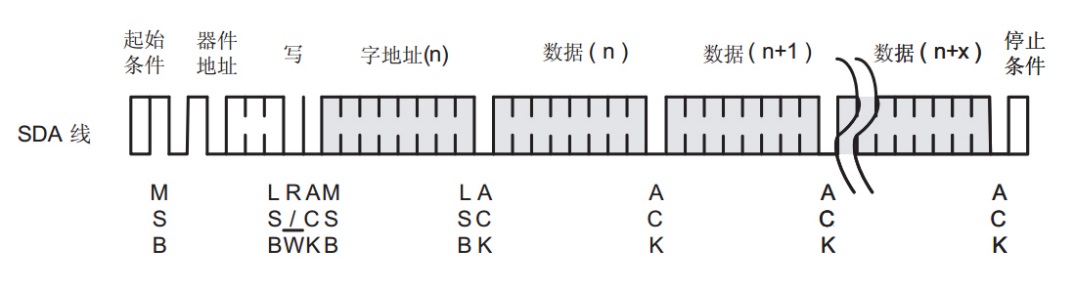

Figure 1‑3 主机写数据到从机

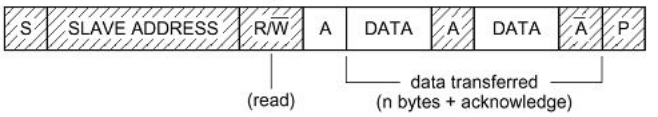

Figure 1‑4 主机由从机中读数据

图例:

数据由主机传输至从机

数据由主机传输至从机  数据由从机传输至主机

数据由从机传输至主机

这两幅图表示的是主机和从机通信时 SDA 线的数据包序列。

其中 S 表示由主机的I2C接口产生的传输起始信号(S),这时连接到I2C总线上的所有从机都会接收到这个信号。

起始信号产生后,所有从机就开始等待主机紧接下来广播的从机地址信号(SLAVE_ADDRESS),在I2C总线上,每个设备的地址都是唯一的。当主机广播的地址与某个设备地址相同时,这个设备就被选中了,没被选中的设备将会忽略之后的数据信号。根据I2C协议,这个从机地址可以是 7 位或 10 位。

在地址位之后,是传输方向的选择位,该位为 0 时,表示后面的数据传输方向是由主机传输至从机。该位为 1 时,则相反。

从机接收到匹配的地址后,主机或从机会返回一个应答(A)或非应答信号,只有接收到应答信号后,主机才能继续发送或接收数据。

若配置的方向传输位为写数据,广播完地址,接收到应答信号后,主机开始正式向从机传输数据(DATA),数据包的大小为 8 位。主机每发送完一个数据,都要等待从机的应答信号(A),重复这个过程,可以向从机传输 N 个数据,这个 N 没有大小限制。当数据传输结束时,主机向从机发送一个停止传输信号(P),表示不再传输数据。

若配置的方向传输位为读数据,广播完地址,接收到应答信号后,从机开始向主机返回数据(DATA),数据包大小也为 8 位。从机每发送完一个数据,都会等待主机的应答信号(A),重复这个过程,可以返回 N 个数据,这个 N 也没有大小限制。当主机希望停止接收数据时,就向从机返回一个非应答信号,则从机自动停止数据传输。

1)支持主机模式(Master)和从机模式(Slave),支持多主多从

2)支持两种速度模式:100KHz 和 400KHz,兼容 I2C 两线串行总线规范

3)支持 7 位或 10 位地址

4)从设备支持双 7 位地址

5)支持总线广播

6)支持总线仲裁、错误检测、PEC 校验、延长时钟

7)兼容 SMBus

1.2 I2C总线的数据传送

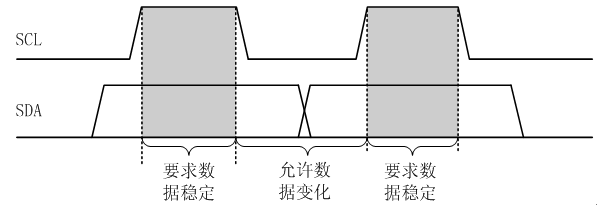

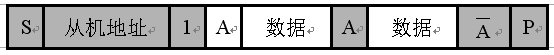

I2C总线进行数据传送时,时钟信号为高电平期间,数据线上的数据必须保持稳定,只有在时钟线上的信号为低电平期间,数据线上的高电平或低电平状态才允许变化。

Figure 1‑6 数据位的有效性规定

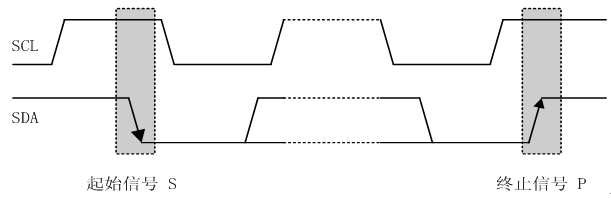

SCL线为高电平期间,SDA线由高电平向低电平的变化表示起始信号;SCL线为高电平期间,SDA线由低电平向高电平的变化表示终止信号。

Figure 1‑7 I2C起始和终止信号

起始和终止信号都是由主机发出的,在起始信号产生后,总线就处于被占用的状态;在终止信号产生后,总线就处于空闲状态。连接到I2C总线上的器件,若具有I2C总线的硬件接口,则很容易检测到起始和终止信号。每当发送器件传输完一个字节的数据后,后面必须紧跟一个校验位,这个校验位是接收端通过控制SDA(数据线)来实现的,以提醒发送端数据我这边已经接收完成,数据传送可以继续进行。

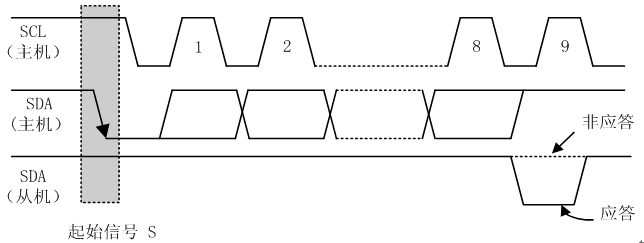

每一个字节必须保证是8位长度。数据传送时,先传送最高位(MSB),每一个被传送的字节后面都必须跟随一位应答位(即一帧共有9位)。

Figure 1‑8 I2C字节传送与应答

由于某种原因从机不对主机寻址信号应答时(如从机正在进行实时性的处理工作而无法接收总线上的数据),它必须将数据线置于高电平,而由主机产生一个终止信号以结束总线的数据传送。

如果从机对主机进行了应答,但在数据传送一段时间后无法继续接收更多的数据时,从机可以通过对无法接收的第一个数据字节的“非应答”通知主机,主机则应发出终止信号以结束数据的继续传送。

当主机接收数据时,它收到最后一个数据字节后,必须向从机发出一个结束传送的信号。这个信号是由对从机的“非应答”来实现的。然后,从机释放SDA线,以允许主机产生终止信号。

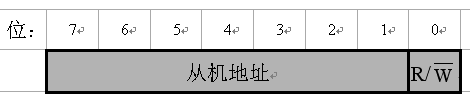

I2C总线协议有明确的规定:采用7位的寻址字节(寻址字节是起始信号后的第一个字节)。

Figure 1‑9 I2C总线寻址

D7~D1位组成从机的地址。D0位是数据传送方向位,为“0”时表示主机向从机写数据,为“1”时表示主机由从机读数据。

主机发送地址时,总线上的每个从机都将这7位地址码与自己的地址进行比较,如果相同,则认为自己正被主机寻址,根据R/T位将自己确定为发送器或接收器。

从机的地址由固定部分和可编程部分组成。在一个系统中可能希望接入多个相同的从机,从机地址中可编程部分决定了可接入总线该类器件的最大数目。如一个从机的7位寻址位有4位是固定位,3位是可编程位,这时仅能寻址8个同样的器件,即可以有8个同样的器件接入到该I2C总线系统中。

I2C总线上传送的数据信号是广义的,既包括地址信号,又包括真正的数据信号。

在起始信号后必须传送一个从机的地址(7位),第8位是数据的传送方向位(R/T),用“0”表示主机发送数据(T),“1”表示主机接收数据(R)。每次数据传送总是由主机产生的终止信号结束。但是,若主机希望继续占用总线进行新的数据传送,则可以不产生终止信号,马上再次发出起始信号对另一从机进行寻址。

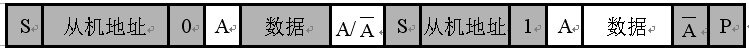

在总线的一次数据传送过程中,可以有以下几种组合方式:

A)主机向从机发送数据,数据传送方向在整个过程中不变;

Figure 1‑10 主机向从机发送数据

注:有阴影部分表示数据由主机向从机传送,无阴影部分则表示数据由从机向主机传送。A表示应答, A表示非应答(高电平)。S表示起始信号,P表示终止信号。

B)主机在第一个字节后,立即从从机读数据。

Figure 1‑11 从机向主机发送数据

C)在传送过程中,当需要改变传送方向时,起始信号和从机地址都被重复产生一次,但两次读/写方向位正好反相。

Figure 1‑12 I2C数据传输方向变换

Figure 1‑13 I2C协议关键信号

要想了解对I2C的主从模式详细了解,参看CH585STM32F10xxx参考手册的I2C接口章节。

2 AT24Cxx存储器原理

2.1 AT24Cxx概述

AT24C01/02/04/08/16是一个1K/2K/4K/8K/16K位串行CMOS,EEPROM内部含有128/256/512/1024/2048个8位字节CATALYST公司的先进CMOS技术实质上减少了器件的功耗,AT24C01/02有一个8字节页写缓冲器AT24C04/08/16有一个16字节页写缓冲器,该器件通过I2C总线接口进行操作有一个专门的写保护功能。AT24C01/02每页有8个字节,分别为16/32页;AT24C04/08/16每页有16个字节,分别为32/64/128页。

工作特点

- 与400KHz I2C总线兼容

- 1.8到6.0伏工作电压范围

- 低功耗CMOS技术

- 写保护功能当WP为高电平时进入写保护状态

- 页写缓冲器

- 自定时擦写周期

- 100万次编程/擦除周期

- 可保存数据100年

- 8脚DIP SOIC或TSSOP封装

- 温度范围商业级和工业级

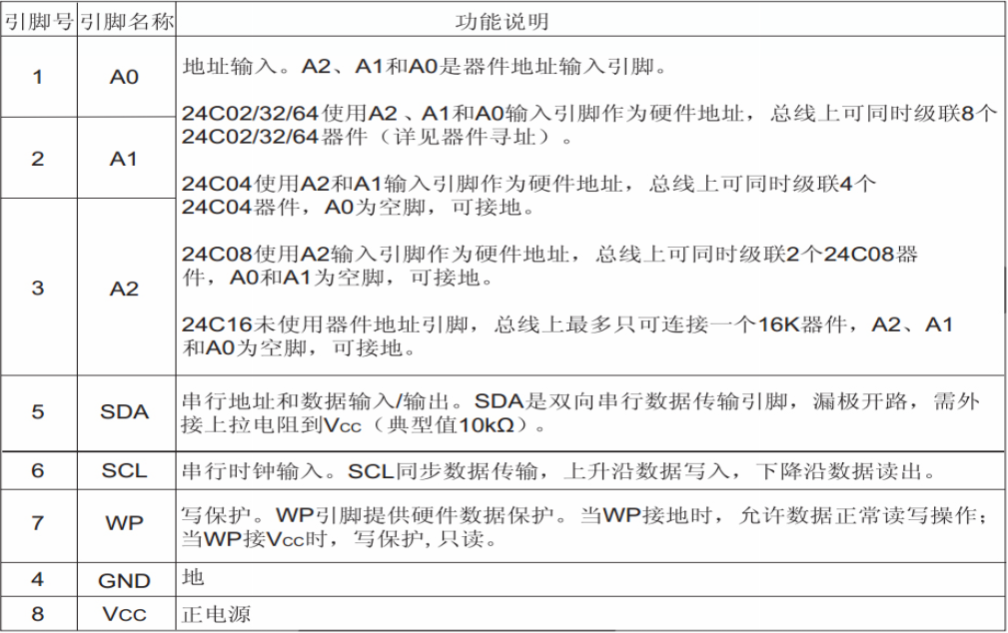

AT24Cxx的引脚定义如下:

Figure 2‑1 AT24Cxx的引脚定义

Note: For use of 5-lead SOT23, the software A2, A1, and A0 bits in the device address word must be set to zero toproperly communicate.

Table 2‑1 AT24Cxx的引脚说明

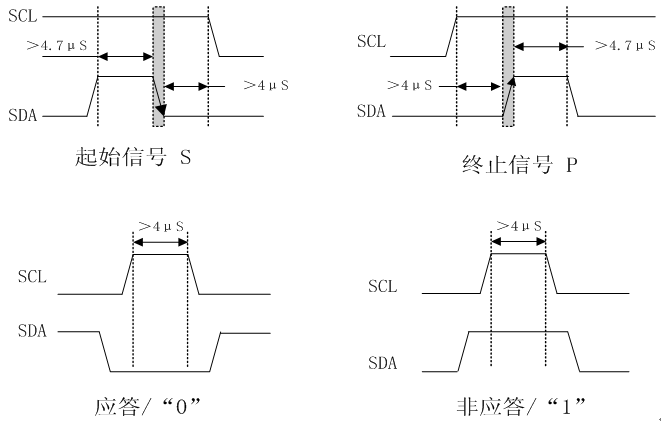

2.2 总线时序

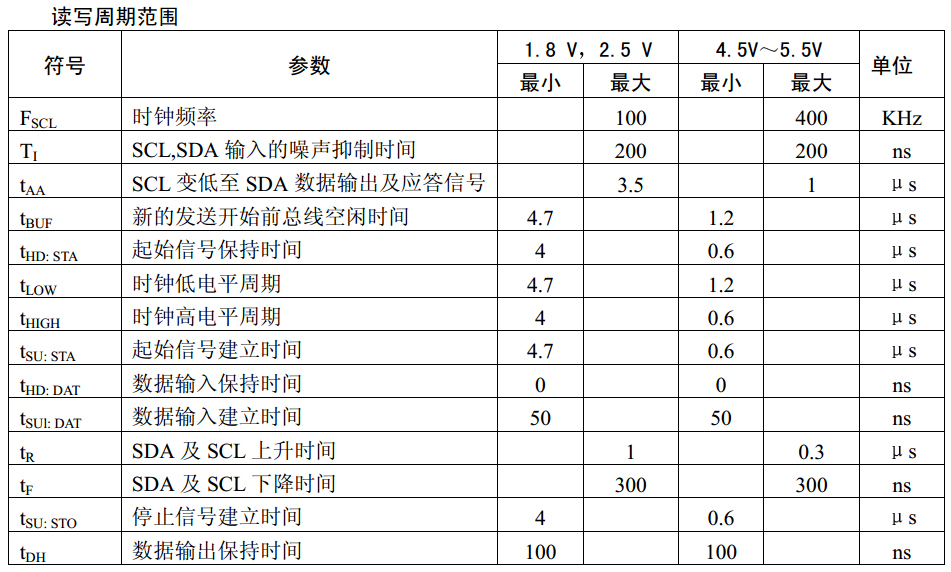

I2C总线时序如下:

Figure 2‑2 I2C总线时序

其读写周期的的电压范围如下:

Table 2‑2 读写周期范围

写周期时间是指从一个写时序的有效停止信号到内部编程/擦除周期结束的这一段时间。在写周期期间,总线接口电路禁能,SDA保持为高电平,器件不响应外部操作。

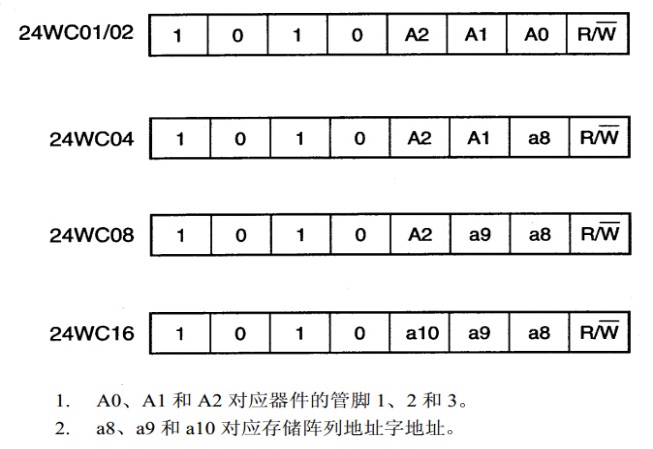

2.3 器件寻址

主器件通过发送一个起始信号启动发送过程,然后发送它所要寻址的从器件的地址。8位从器件地址的高4位固定为(1010)。接下来的3位(A2、A1、A0)为器件的地址位,用来定义哪个器件以及器件的哪个部分被主器件访问,上述8个AT24C01/02,4个AT24C04,2个AT24C08,1个AT24C16可单独被系统寻址。从器件8位地址的最低位,作为读写控制位。“1”表示对从器件进行读操作,“0”表示对从器件进行写操作。在主器件发送起始信号和从器件地址字节后,AT24C01/02/04/08/16监视总线并当其地址与发送的从地址相符时响应一个应答信号(通过SDA线)。AT24C01/02/04/08/16再根据读写控制位(R/W)的状态进行读或写操作。

Figure 2‑3 I2C器件寻址

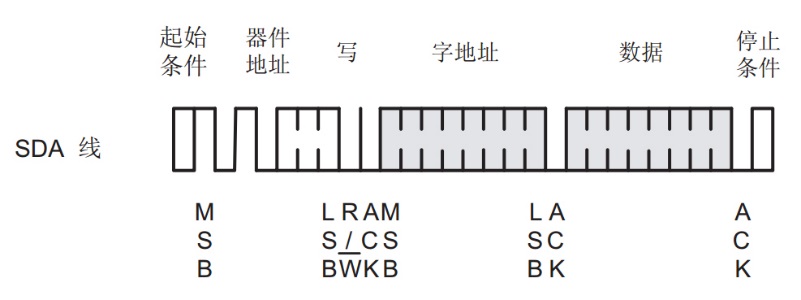

在字节写模式下,主器件发送起始命令和从器件地址信息(R/W)位置发给从器件,在从器件产生应答信号后,主器件发送AT24Cxx的字节地址,主器件在收到从器件的另一个应答信号后,再发送数据到被寻址的存储单元。AT24Cxx再次应答,并在主器件产生停止信号后开始内部数据的擦写,在内部擦写过程中,AT24Cxx不再应答主器件的任何请求。

Figure 2‑4 字节写时序

用页写,AT24C01/02可一次写入8 个字节数据,AT24C04/08/16可以一次写入16个字节的数据。__页写操作的启动和字节写一样,不同在于传送了一字节数据后并不产生停止信号。__主器件被允许发送P(AT24C01:P=7;AT24C02/04/08/16:P=15)个额外的字节。每发送一个字节数据后AT24Cxx产生一个应答位并将字节地址低位加1,高位保持不变。

如果在发送停止信号之前主器件发送超过P+1个字节,地址计数器将自动翻转,先前写入的数据被覆盖。

接收到P+1字节数据和主器件发送的停止信号后,AT24Cxx启动内部写周期将数据写到数据区。所有接收的数据在一个写周期内写入AT24Cxx。

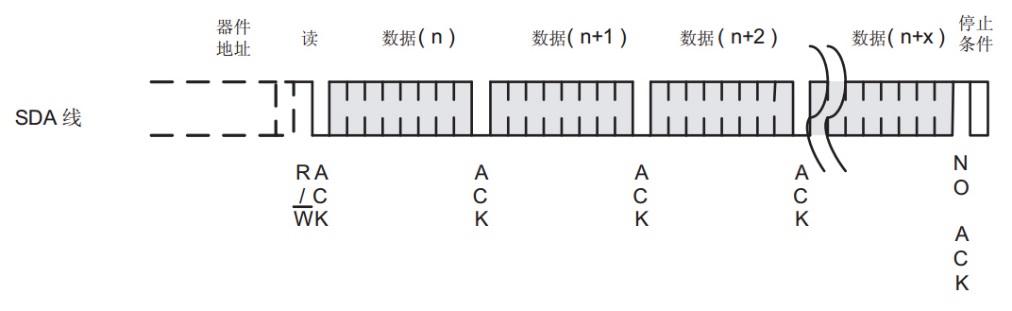

Figure 2‑5 页写时序

读操作允许主器件对寄存器的任意字节进行读操作,主器件首先通过发送起始信号、从器件地址和它想读取的字节数据的地址执行一个写操作。在AT24Cxx应答之后,主器件重新发送起始信号和从器件地址,此时R/W位置1,AT24Cxx响应并发送应答信号,然后输出所要求的一个8位字节数据,主器件不发送应答信号但产生一个停止信号。

Figure 2‑6 读字节

在AT24Cxx发送完一个8位字节数据后,主器件产生一个应答信号来响应,告知AT24Cxx主器件要求更多的数据,对应每个主机产生的应答信号AT24Cxx将发送一个8位数据字节。当主器件不发送应答信号而发送停止位时结束此操作。

从AT24Cxx输出的数据按顺序由N到N+1输出。读操作时地址计数器在AT24Cxx整个地址内增加,这样整个寄存器区域可在一个读操作内全部读出,当读取的字节超过E(对于24WC01,E=127;对24C02,E=255;对24C04,E=511;对24C08,E=1023;对24C16,E=2047)计数器将翻转到零并继续输出数据字节。

Figure 2‑7 顺序读时序

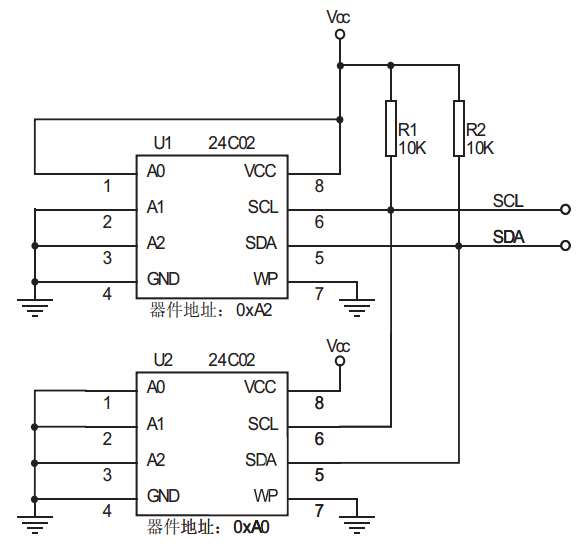

AT24C02的典型电路如下:

Figure 2‑8 AT24C02典型电路

根据AT24C02的芯片资料,我们会发现AT24C02有三个地址A0,A1,A2。同时,我们会在资料的Device Address介绍发现I2C器件一共有七位地址码,还有一位是读/写(R/W)操作位,而在AT24C02的前四位已经固定为1010。R/W为1则为 读操作,为0则为写操作。R/W位我们要设置为0(写操作)。

规则为:1010(A0)(A1)(A2)(R/W)

例子1:

那么对应的A0,A1,A2都是接的VCC,所以为A0=1,A1=1,A2=1;可以知道AT24C02的从设备写地址为10101110(0xae),读设备地址为10101111(0xaf)。

例子2:

那么对应的A0,A1,A2都是接的GND,所以为A0=0,A1=0,A2=0;可以知道AT24C02的从设备写地址为10100000(0xa0),读设备地址为10100001(0xa1)。

3 硬件设计及连接

本文是使用I2C协议对EEPROM进行读写操作,具体的硬件连接如下。

Figure 3‑1 硬件电路

从硬件链接可以得到AT24C02的地址是0xA0。