一、实验要求

生成 DDR3 IP 官方例程,实现 DDR3 的读写控制,了解其工作原理和用户接口。

二、DDR3 控制器简介

PGL50H 为用户提供一套完整的 DDR memory 控制器解决方案,配置方式比较灵活,采用软核实现 DDR memory 的控制,有如下特点:

➢支持 DDR3

➢支持 x8、x16 Memory Device

➢最大位宽支持 32 bit

➢支持裁剪的 AXI4 总线协议

➢一个 AXI4 256 bit Host Port

➢支持 Self_refresh,Power down

➢支持 Bypass DDRC

➢支持 DDR3 Write Leveling 和 DQS Gate Training

➢DDR3 最快速率达 800 Mbps

三、实验设计

a. 安装 DDR3 IP 核

PDS 安装后,需手动添加 DDR3 IP,请按以下步骤完成:

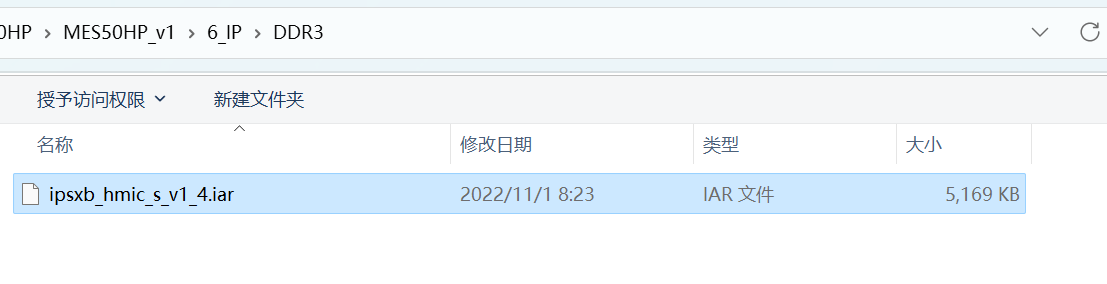

(1)DDR3 IP 文件:6_IP_setup_packet\DDR3\ipsxb_hmic_s_v1_4

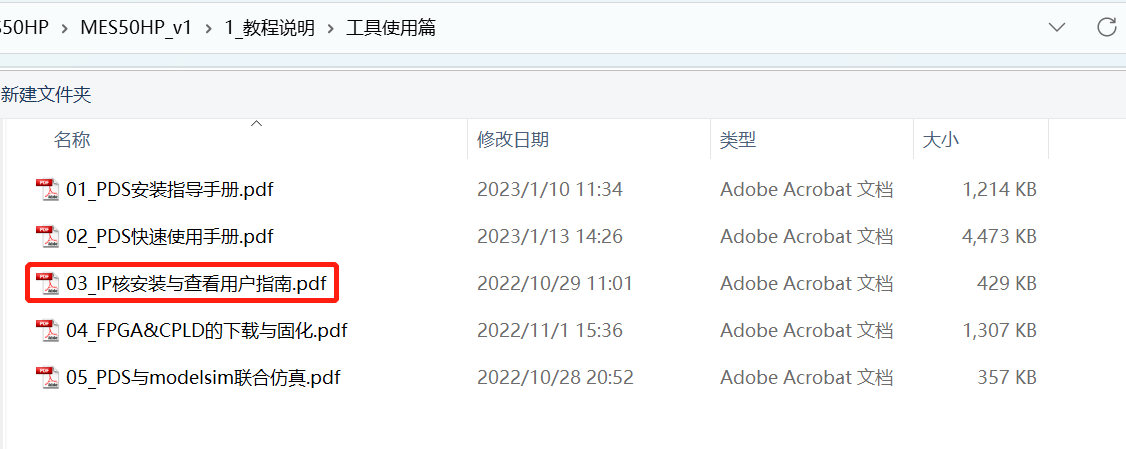

(2)IP 安装步骤:1_Demo_document\工具使用篇\03_IP 核安装与查看用户指南

b. DDR3 读写 Example 工程

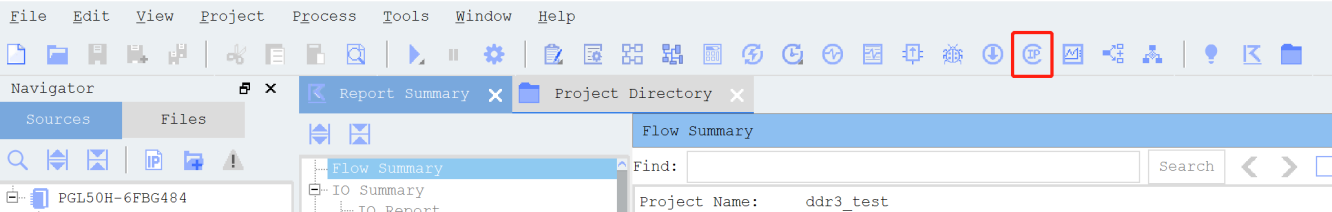

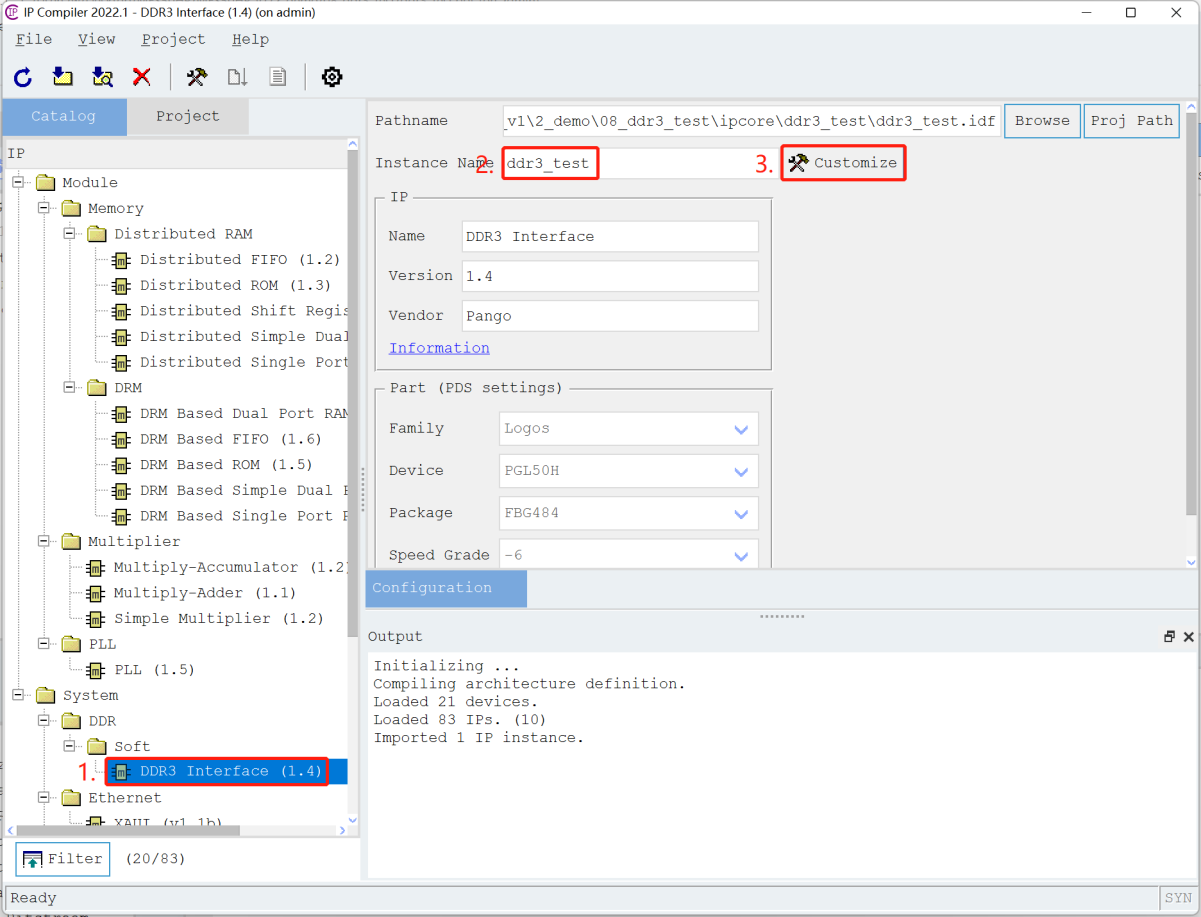

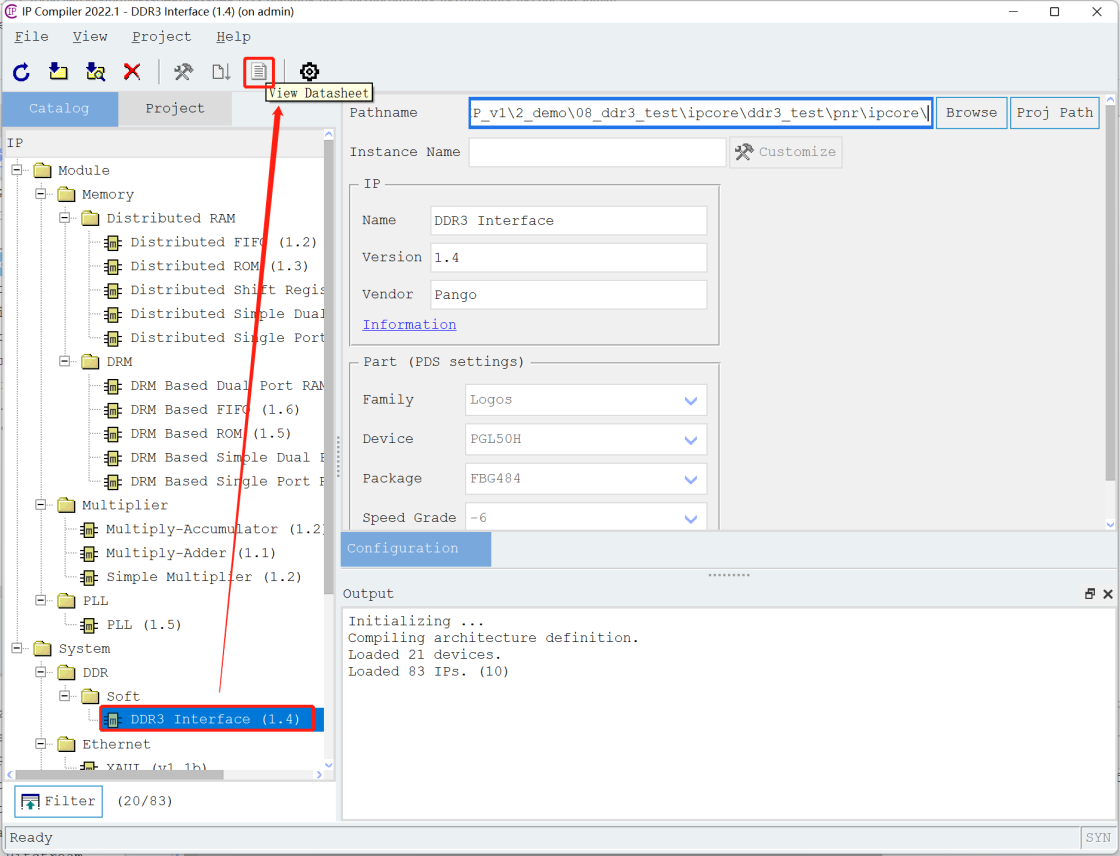

1.打开 PDS 软件,新建工程 ddr3_test,点开如下图标,打开 IP Compiler;

2.选择 DDR3 IP,取名,然后点击 Customize;

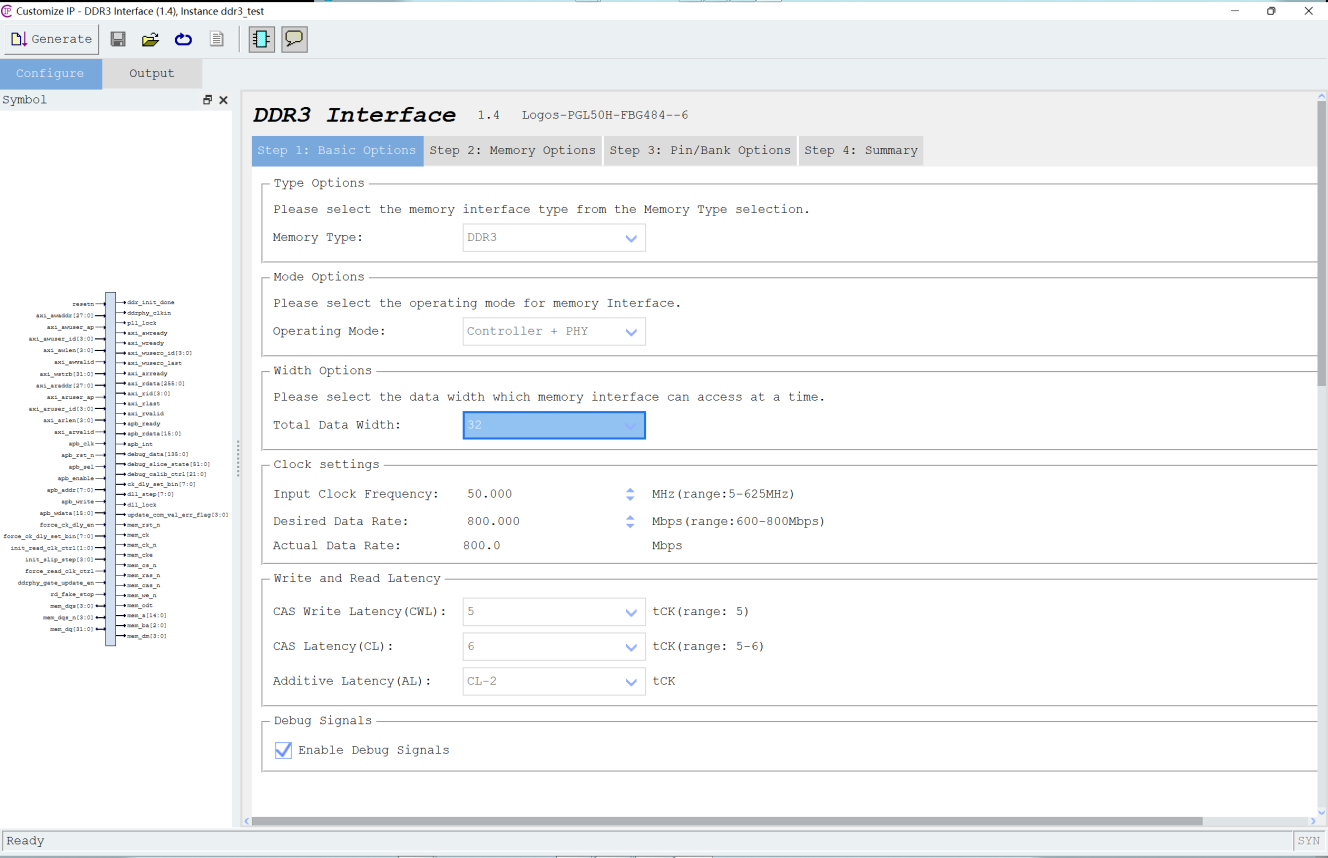

3.在 DDR3 设置界面中 Step1 按照如下设置:

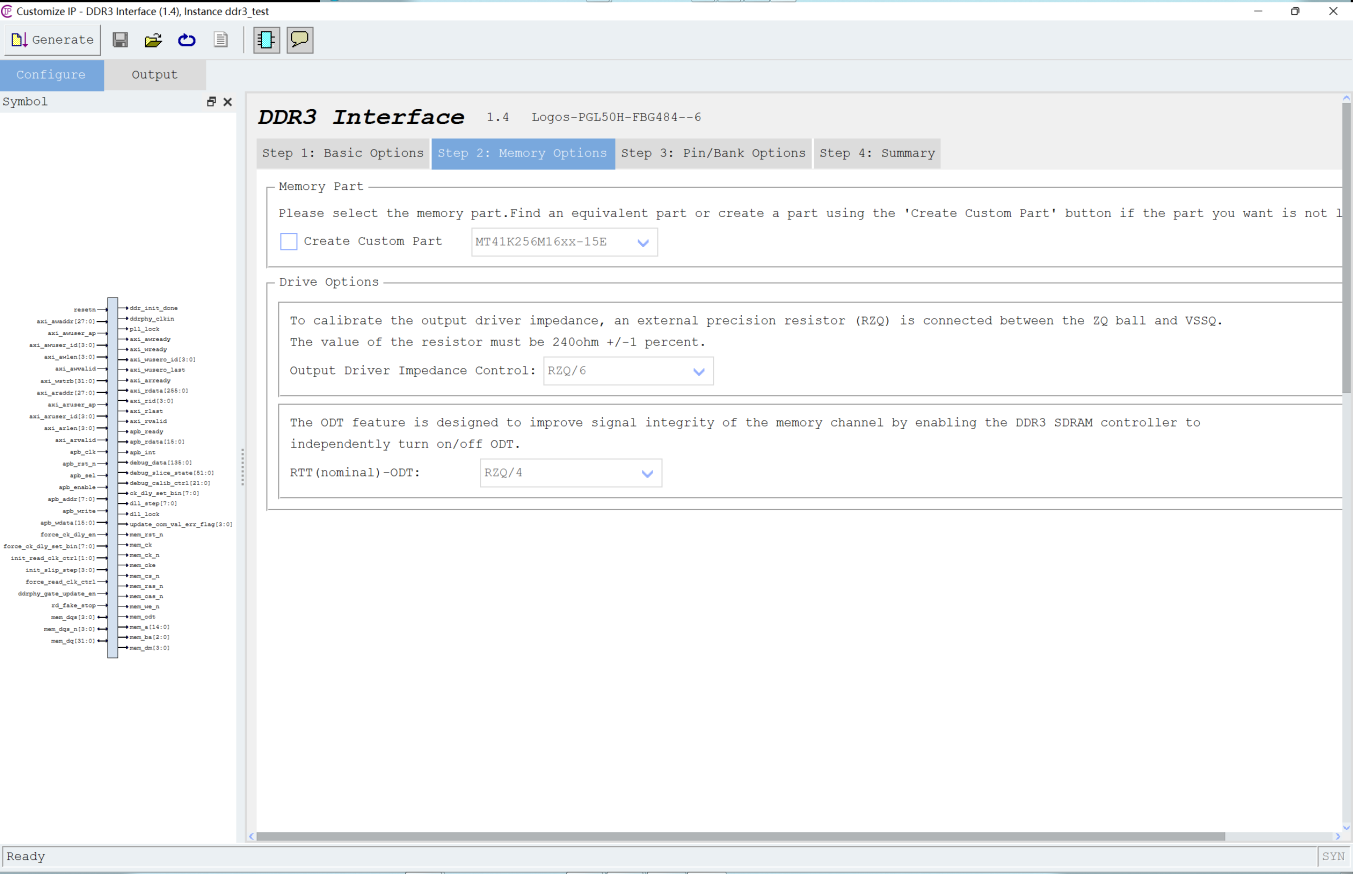

- Step2 按照如下设置:

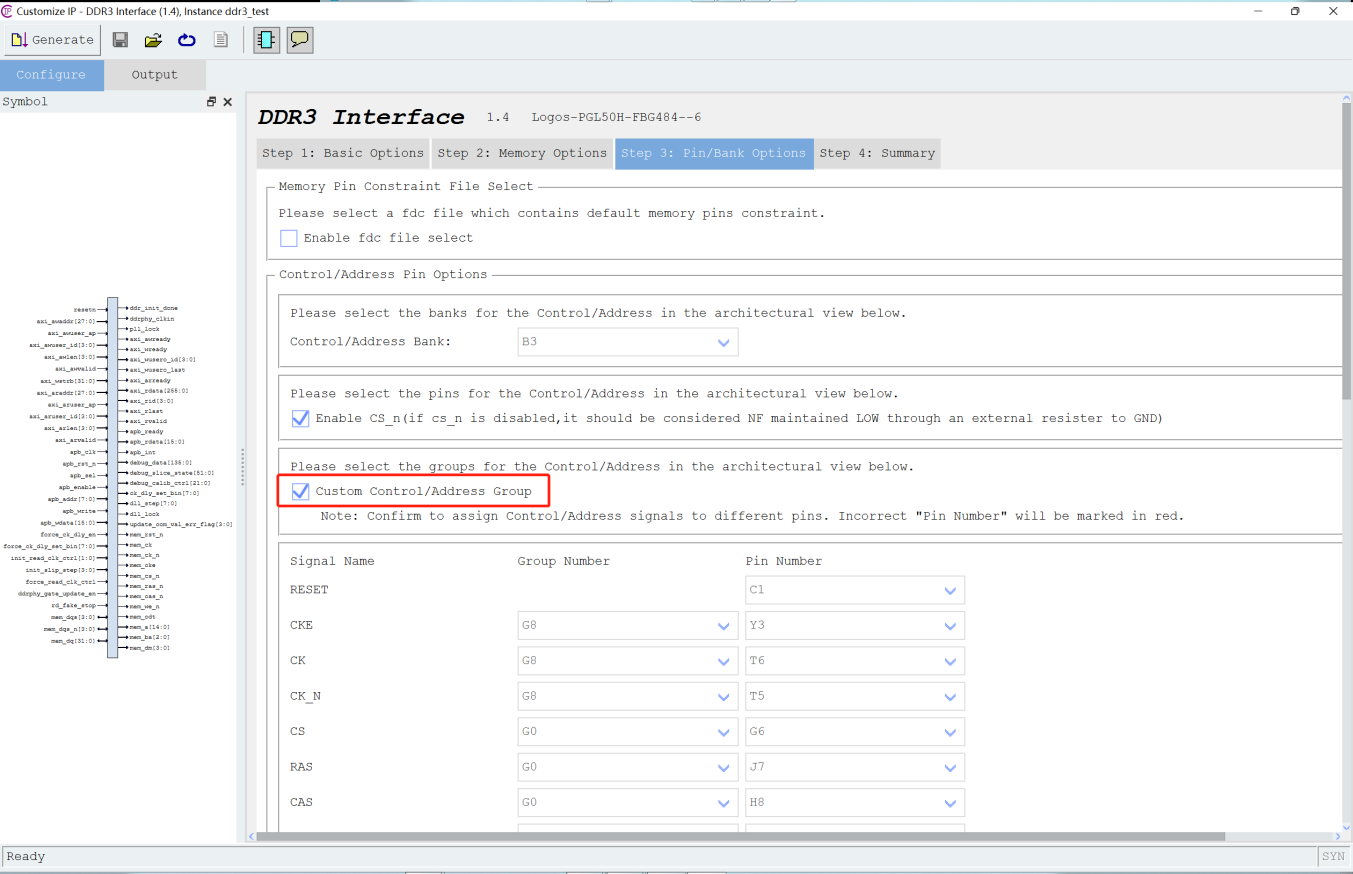

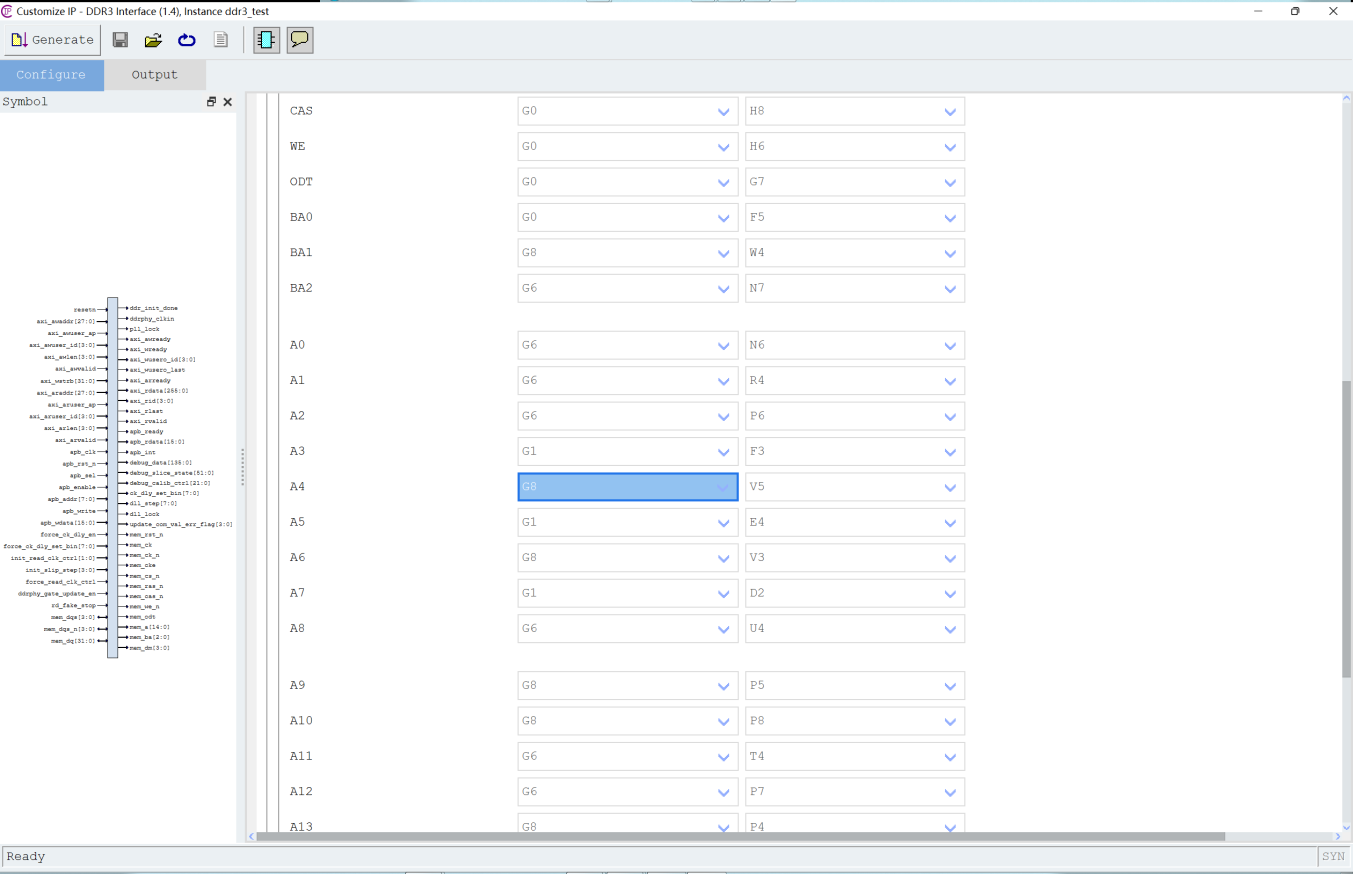

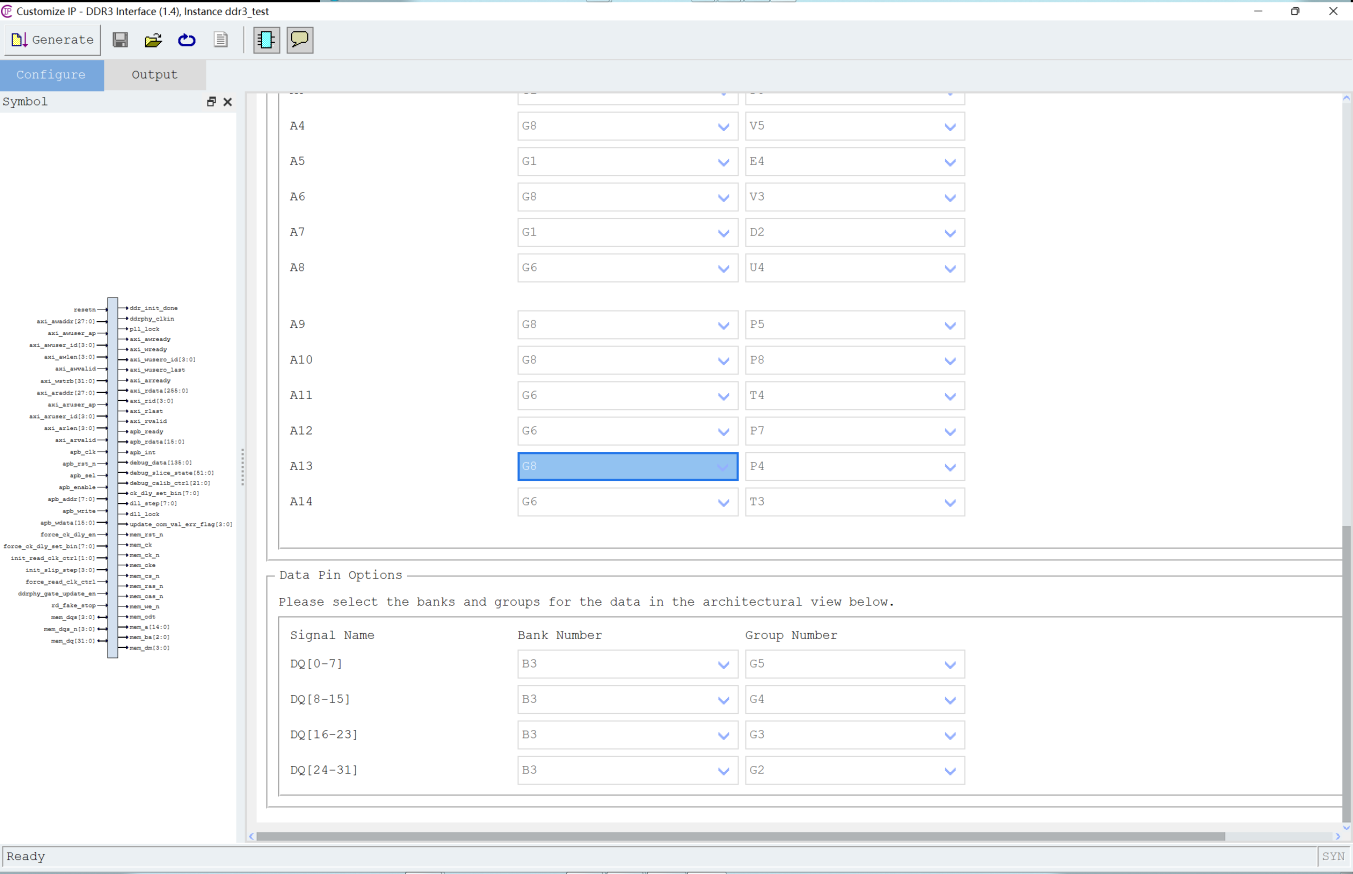

5.Step3 按照如下设置,勾选 Custom Control/Address Group,管脚约束参考原理图:

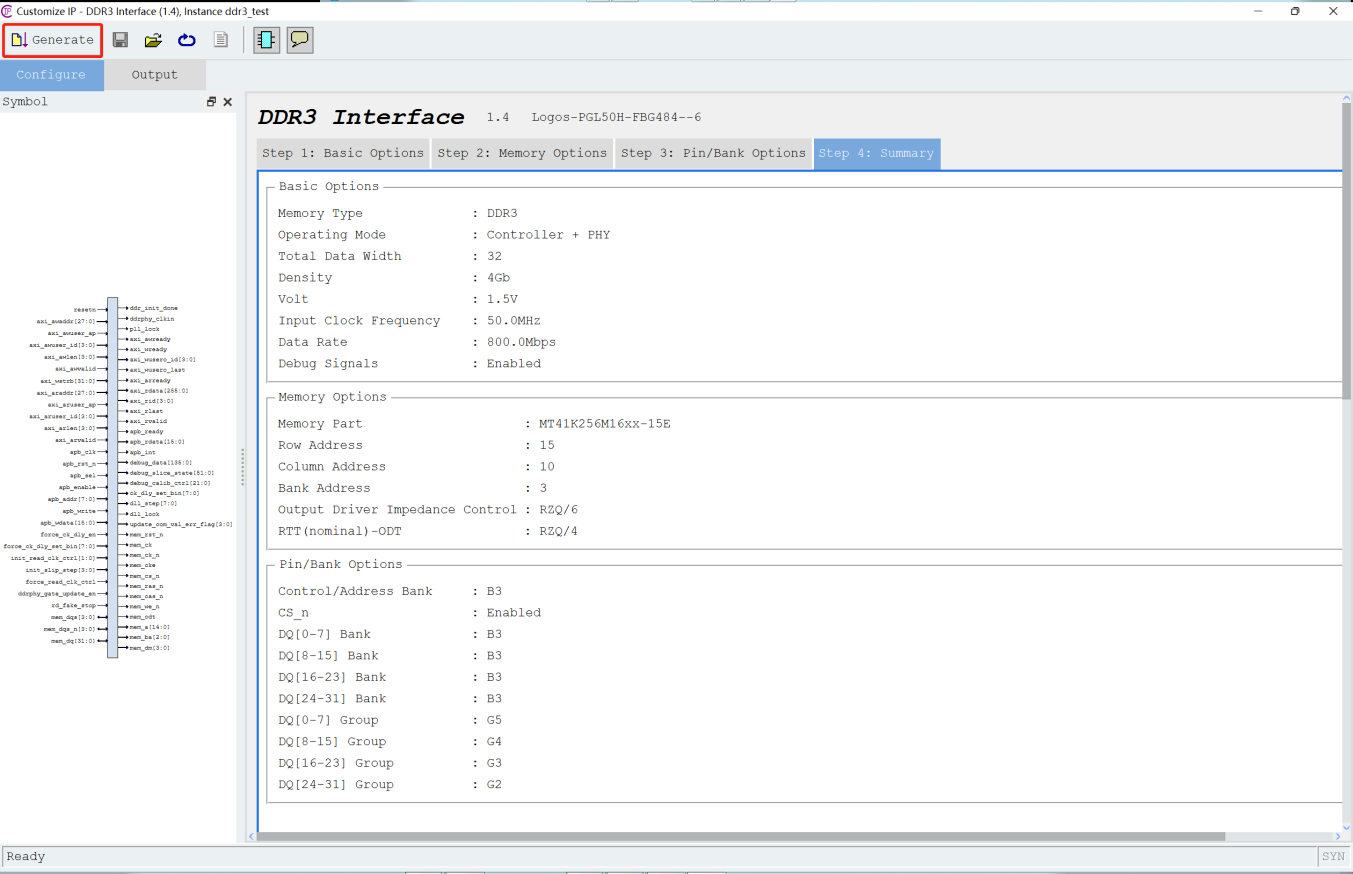

6.Step4 为概要,点击 Generate 可生成 DDR3 IP;

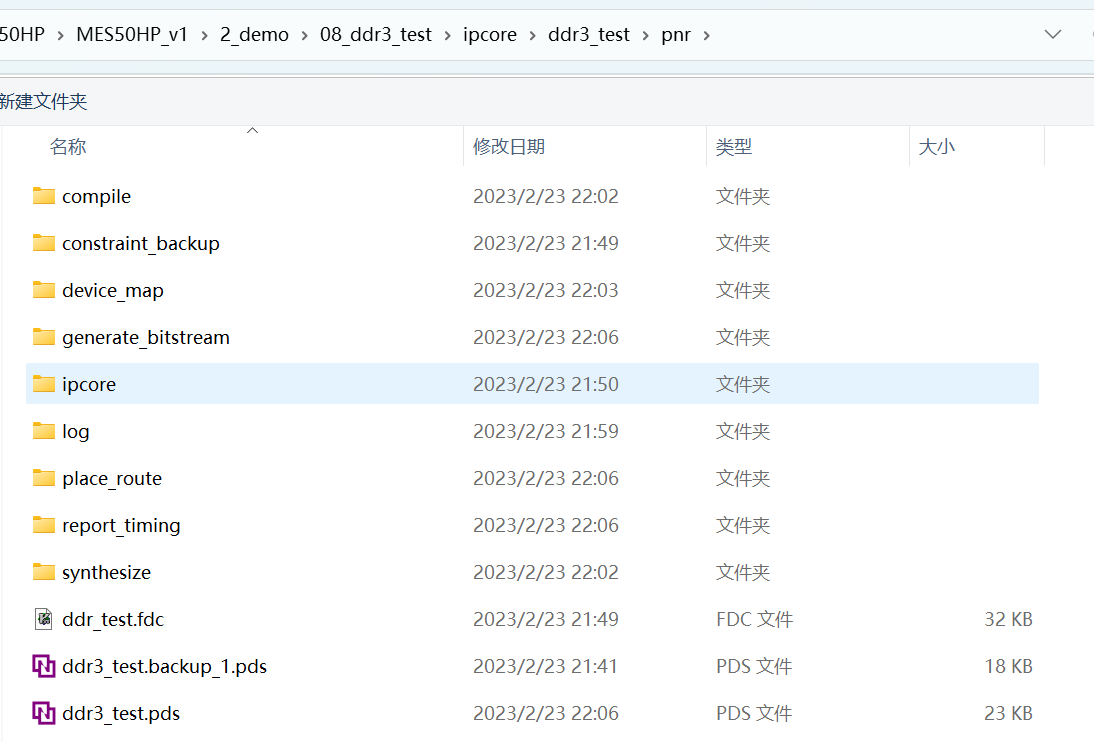

7.关闭本工程,按此路径打开 Example 工程:

2_Demo\08_ddr3_test\ipcore\ddr3_test\pnr

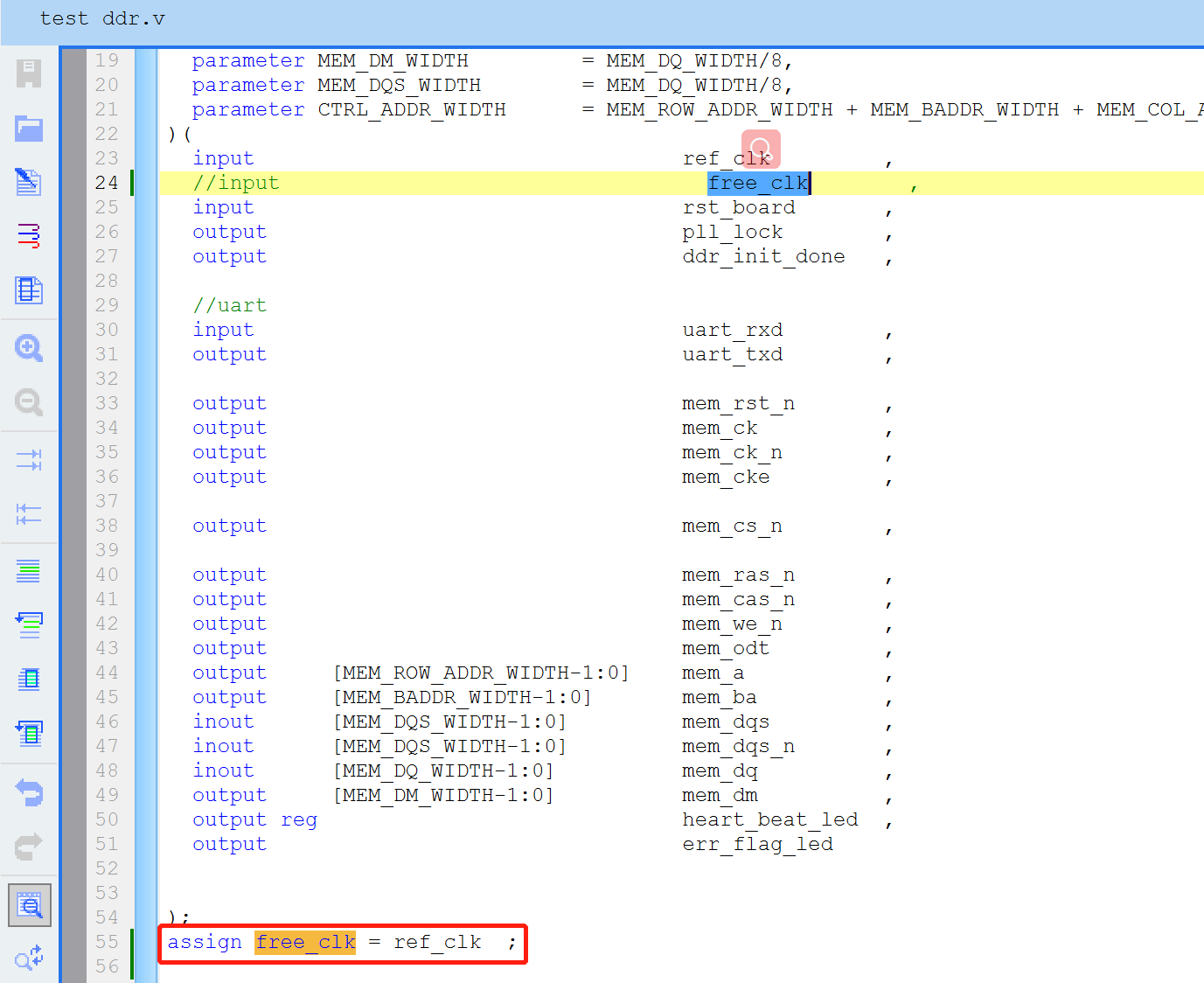

8.打开顶层文件 free_clk、ref_clk 可使用同一时钟源:

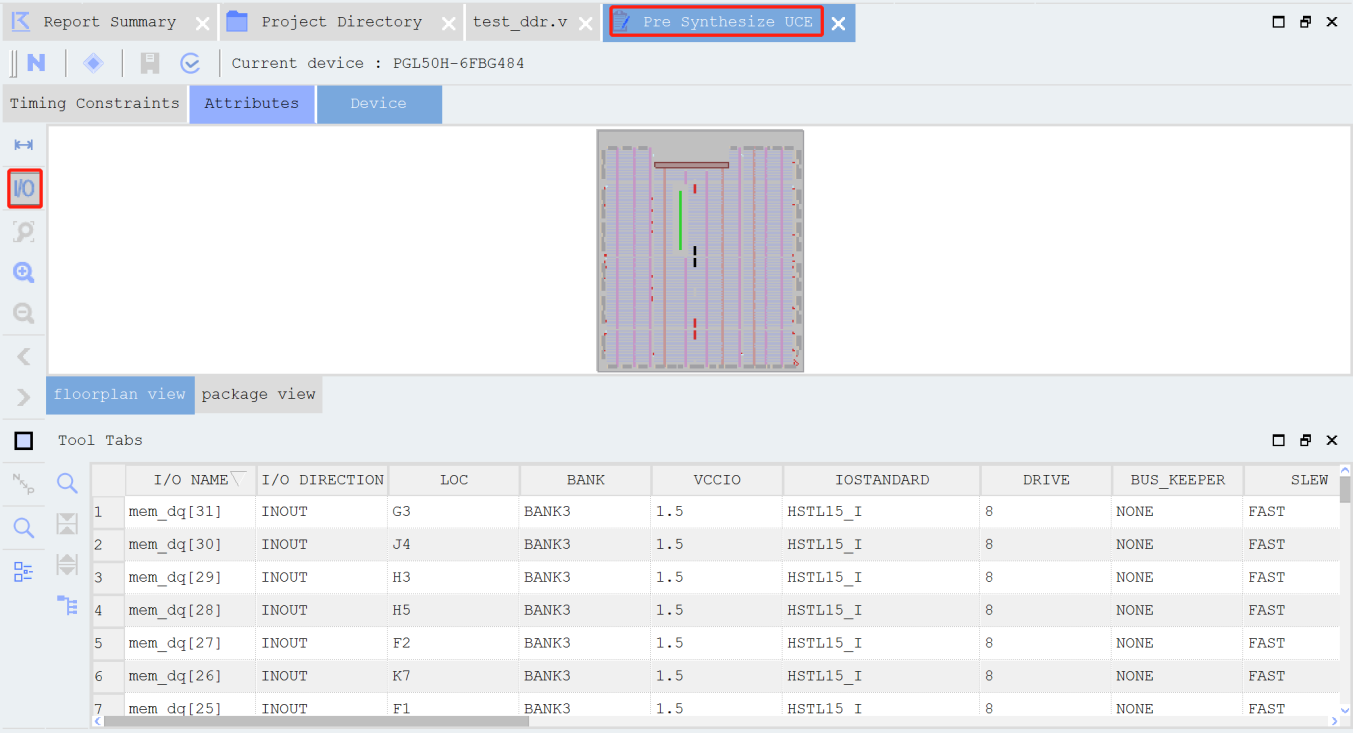

9.对“Step3 已做管脚约束”外的其他管脚,对照原理图使用 UCE 工具进行修改:

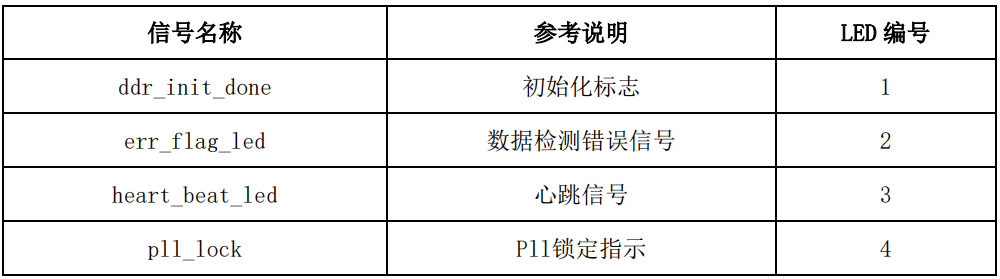

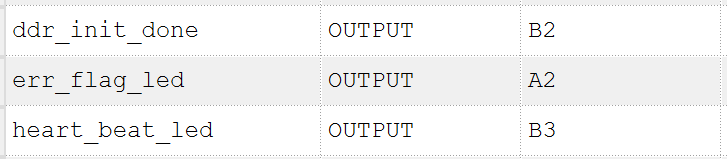

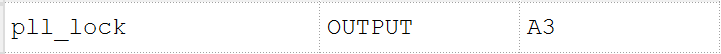

10.以下管脚可约束在 LED,方便观察实验现象;

11.可按以下方式查看 IP 核的用户指南,了解 Example 模块组成;

四、实验现象

注:例程位置:2_Demo\07_ddr3_test\ipcore\ddr3_test\pnr

下载程序,可以看到 LED1 常亮,LED2 常灭, LED3 闪烁,LED4 常亮;