1 瑞芯微GPIO引脚定义

1.1 引脚命名

GPIO{bank}{letter}{number}{mode}

GPIO0_C1_d

- GPIO0:表示第0组GPIO控制器(RK3568有多个GPIO控制器,如GPIO0、GPIO1等)。

- 字母部分(C):表示GPIO组内的子组(如A、B、C、D),对应不同的引脚偏移,如32个引脚,分成A,B,C,D四组

- 数字部分(1):表示在该子组中的引脚序号(从0开始)。

- _d:可能表示引脚的复用功能模式(如_a, _b, _c, _d等)

即下面GPIO4_D5 pin脚计算方法:

bank = 4; //GPIO4_D5 => 4, bank ∈ [0,4]

group = 3; //GPIO4_D5 => 3, group ∈ {(A=0), (B=1), (C=2), (D=3)}

X = 5; //GPIO4_D5 => 5, X ∈ [0,7]

number = group * 8 + X = 3 * 8 + 5 = 29

pin = bank*32 + number= 4 * 32 + 29 = 157;

1.2 调试信息

查看当前使用的引脚

root@RK3562-Tronlong:~# cat /sys/kernel/debug/gpio

gpiochip0: GPIOs 0-31, parent: platform/ff260000.gpio, gpio0:

gpio-5 ( |heartbeat ) out lo

gpio-6 ( |disk ) out lo

gpio-8 ( |vcc5v0-usb-otg ) out lo

gpio-19 ( |vcc3v3-lcd0-n ) out lo

gpiochip1: GPIOs 32-63, parent: platform/ff620000.gpio, gpio1:

gpiochip2: GPIOs 64-95, parent: platform/ff630000.gpio, gpio2:

gpiochip3: GPIOs 96-127, parent: platform/ffac0000.gpio, gpio3:

gpio-113 ( |ch482d_sel ) out lo ACTIVE LOW

gpiochip4: GPIOs 128-143, parent: platform/ffad0000.gpio, gpio4:

gpio-137 ( |user-led0 ) out lo

gpio-143 ( |user-led1 ) out lo

gpiochip5: GPIOs 511-511, parent: platform/rk805-pinctrl, rk817-gpio, can sleep:

查看当前配置的引脚

root@RK3562-Tronlong:~# ls /sys/kernel/debug/pinctrl/pinctrl-rockchip-pinctrl

gpio-ranges pinconf-pins pinmux-functions pins

pinconf-groups pingroups pinmux-pins

1.3配置

默认,在设备树文件tl3562-minievm.dts中,将所有的扩展引脚皆配置为gpio

export-pins {

export_pins_gpio: export_pins_gpio {

rockchip,pins = <

0 RK_PC0 RK_FUNC_GPIO &pcfg_pull_none

0 RK_PC1 RK_FUNC_GPIO &pcfg_pull_none

0 RK_PC6 RK_FUNC_GPIO &pcfg_pull_none

0 RK_PC7 RK_FUNC_GPIO &pcfg_pull_none

3 RK_PA0 RK_FUNC_GPIO &pcfg_pull_none

3 RK_PA1 RK_FUNC_GPIO &pcfg_pull_none

4 RK_PB4 RK_FUNC_GPIO &pcfg_pull_none

4 RK_PB5 RK_FUNC_GPIO &pcfg_pull_none

1 RK_PC1 RK_FUNC_GPIO &pcfg_pull_none

1 RK_PC2 RK_FUNC_GPIO &pcfg_pull_none

1 RK_PC3 RK_FUNC_GPIO &pcfg_pull_none

1 RK_PC4 RK_FUNC_GPIO &pcfg_pull_none

1 RK_PC5 RK_FUNC_GPIO &pcfg_pull_none

1 RK_PC6 RK_FUNC_GPIO &pcfg_pull_none

4 RK_PB6 RK_FUNC_GPIO &pcfg_pull_none

3 RK_PD2 RK_FUNC_GPIO &pcfg_pull_none

3 RK_PD3 RK_FUNC_GPIO &pcfg_pull_none

3 RK_PB7 RK_FUNC_GPIO &pcfg_pull_none

3 RK_PC0 RK_FUNC_GPIO &pcfg_pull_none>;

};

};

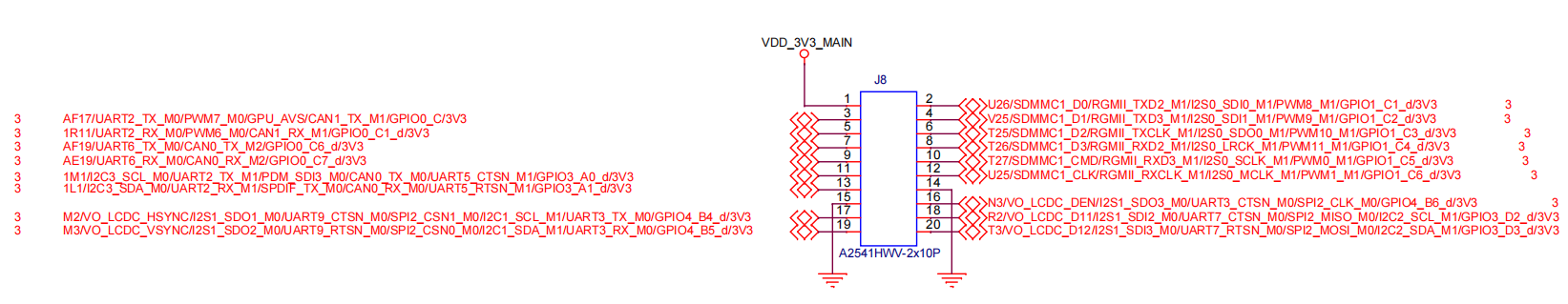

即对应的J8引脚为

1.4 控制引脚

:/ # ls /sys/class/gpio/

export gpiochip128 gpiochip32 gpiochip64 unexport

gpiochip0 gpiochip255 gpiochip500 gpiochip96

:/ # echo 157 > /sys/class/gpio/export

:/ # ls /sys/class/gpio/

export gpiochip0 gpiochip255 gpiochip500 gpiochip96

gpio157 gpiochip128 gpiochip32 gpiochip64 unexport

:/ # ls /sys/class/gpio/gpio157

ative_low device direction edge power subsystem uevent value

:/ # cat /sys/class/gpio/gpio157/direction

in

:/ # cat /sys/class/gpio/gpio157/value

0

2 pwm控制

2.1 配置

以pwm7为例,默认rk3562.dtsi配置如下

pwm7: pwm@ff700030 {

compatible = "rockchip,rk3562-pwm", "rockchip,rk3328-pwm";

reg = <0x0 0xff700030 0x0 0x10>;

interrupts = <GIC_SPI 22 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 23 IRQ_TYPE_LEVEL_HIGH>;

#pwm-cells = <3>;

pinctrl-names = "active";

pinctrl-0 = <&pwm7m0_pins>;

clocks = <&cru CLK_PWM1_PERI>, <&cru PCLK_PWM1_PERI>;

clock-names = "pwm", "pclk";

status = "disabled";

};

即使用pwm7m0_pins引脚配置,它在rk3562-pintrl.dtsi中定义如下

pwm7 {

/omit-if-no-ref/

pwm7m0_pins: pwm7m0-pins {

rockchip,pins =

<0 RK_PC0 2 &pcfg_pull_none_drv_level_1>;

};

/omit-if-no-ref/

pwm7m1_pins: pwm7m1-pins {

rockchip,pins =

<1 RK_PD4 4 &pcfg_pull_none_drv_level_1>;

};

};

即使用GPIO0_C0引脚,正好与原理图的J8_3相对应

3.2 控制

如下所示,可以到/sys/class/pwm/下控制,也可以到具体的/sys/devices/platform/xx/pwm/下控制,它们通过软链接指向同一个

root@RK3562-Tronlong:~# cd /sys/class/pwm/

root@RK3562-Tronlong:/sys/class/pwm# ls -al

total 0

drwxr-xr-x 2 root root 0 Jun 18 04:29 .

drwxr-xr-x 76 root root 0 Jun 18 04:29 ..

lrwxrwxrwx 1 root root 0 Jun 18 04:29 pwmchip0 -> ../../devices/platform/ff230030.pwm/pwm/pwmchip0

lrwxrwxrwx 1 root root 0 Jun 18 04:29 pwmchip1 -> ../../devices/platform/ff700000.pwm/pwm/pwmchip1

lrwxrwxrwx 1 root root 0 Jun 18 04:29 pwmchip2 -> ../../devices/platform/ff700030.pwm/pwm/pwmchip2

root@RK3562-Tronlong:/sys/class/pwm# cd /sys/devices/platform/ff700030.pwm/pwm/

root@RK3562-Tronlong:/sys/devices/platform/ff700030.pwm/pwm# ls

pwmchip2

root@RK3562-Tronlong:/sys/devices/platform/ff700030.pwm/pwm# cd pwmchip2/

root@RK3562-Tronlong:/sys/devices/platform/ff700030.pwm/pwm/pwmchip2# ls

device export npwm power subsystem uevent unexport

root@RK3562-Tronlong:/sys/devices/platform/ff700030.pwm/pwm/pwmchip2# echo 0 >export

root@RK3562-Tronlong:/sys/devices/platform/ff700030.pwm/pwm/pwmchip2# cd pwm0

root@RK3562-Tronlong:/sys/devices/platform/ff700030.pwm/pwm/pwmchip2/pwm0# ls

capture duty_cycle enable output_type period polarity power uevent

3 adc控制

3.1 配置

默认支持8通道10位的saadc,配置如下

saradc0: saradc@ff730000 {

compatible = "rockchip,rk3562-saradc";

reg = <0x0 0xff730000 0x0 0x100>;

interrupts = <GIC_SPI 40 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&cru CLK_SARADC>, <&cru PCLK_SARADC>;

clock-names = "saradc", "apb_pclk";

resets = <&cru SRST_P_SARADC>;

reset-names = "saradc-apb";

status = "disabled";

};

对的J9如下所示

3.2 控制

root@RK3562-Tronlong:~# cd /sys/bus/iio/devices/iio

iio:device0/ iio:device1/ iio_sysfs_trigger/

root@RK3562-Tronlong:~# cd /sys/bus/iio/devices/iio:device0

root@RK3562-Tronlong:/sys/bus/iio/devices/iio:device0# ls

buffer in_voltage2_raw in_voltage6_raw of_node trigger

dev in_voltage3_raw in_voltage7_raw power uevent

in_voltage0_raw in_voltage4_raw in_voltage_scale scan_elements

in_voltage1_raw in_voltage5_raw name subsystem

4 i2c控制

4.1 配置

以i2c3为例子,默认rk3562.dtsi配置为

i2c3: i2c@ffa20000 {

compatible = "rockchip,rk3562-i2c", "rockchip,rk3399-i2c";

reg = <0x0 0xffa20000 0x0 0x1000>;

clocks = <&cru CLK_I2C3>, <&cru PCLK_I2C3>;

clock-names = "i2c", "pclk";

interrupts = <GIC_SPI 15 IRQ_TYPE_LEVEL_HIGH>;

pinctrl-names = "default";

pinctrl-0 = <&i2c3m0_xfer>;

#address-cells = <1>;

#size-cells = <0>;

status = "disabled";

};

即使用i2c3m0_xfer引脚配置,它在rk3562-pintrl.dtsi中定义如下

i2c3 {

/omit-if-no-ref/

i2c3m0_xfer: i2c3m0-xfer {

rockchip,pins =

<3 RK_PA0 1 &pcfg_pull_none_smt>,

<3 RK_PA1 1 &pcfg_pull_none_smt>;

};

/omit-if-no-ref/

i2c3m1_xfer: i2c3m1-xfer {

rockchip,pins =

<4 RK_PA5 5 &pcfg_pull_none_smt>,

<4 RK_PA6 5 &pcfg_pull_none_smt>;

};

};

即使用GPIO3_A0和GPIO3_A1引脚,正好与原理图的J8_13/J8_15相对应

但这里有个问题,纵观整个原理图,i2c没有硬件上位,故需要修改引脚配置

/omit-if-no-ref/

i2c3m0_xfer: i2c3m0-xfer {

rockchip,pins =

<3 RK_PA0 1 &pcfg_pull_up>,

<3 RK_PA1 1 &pcfg_pull_up>;

};

4.2 控制

通过设备节点控制

root@RK3562-Tronlong:~# ls /dev/i2c-

i2c-0 i2c-1 i2c-2 i2c-3

也可以通过i2ctools工具通过

i2cset [-f] [-y] [-m MASK] [-r] [-a] I2CBUS CHIP-ADDRESS DATA-ADDRESS [VALUE] ... [MODE]

backlight=0x62

mode1=0x00

i2cset -y 1 $backlight $mode1 0x00

电子发烧友论坛

电子发烧友论坛 /9

/9

淘帖

淘帖 294

294