Srinadh,

谢谢。

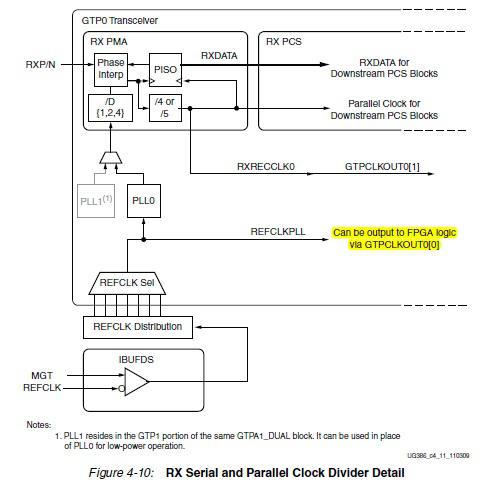

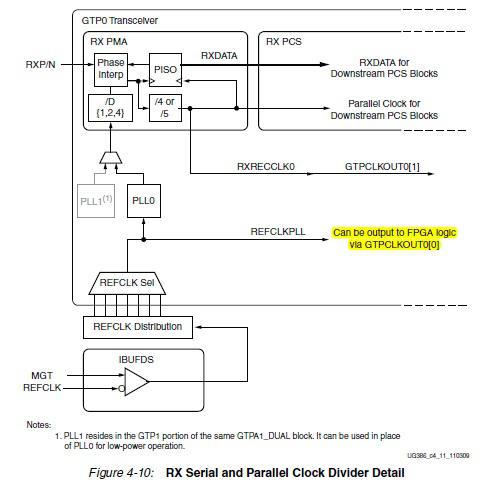

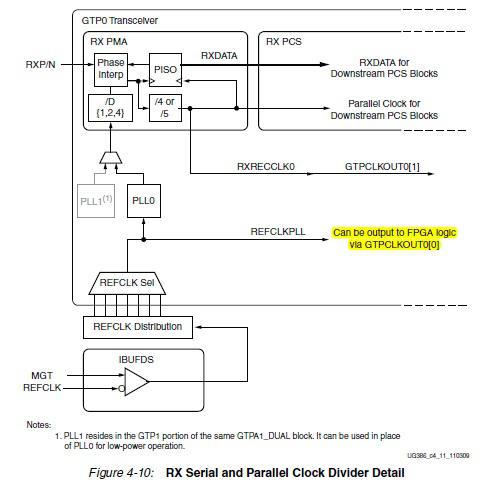

gtpclkout0(0)用于Tx,gtpclkout0(1)用于Rx。

来自UG386,

据说REFCLKPLL可以通过gtpclkout0(0)输出到FPGA逻辑,但你是对的。

如果我们“只”考虑频率,那么这个时钟与我设计中的rxrecclk相同。

你发现设计在模拟中工作吗?

如果您使用逗号对齐,请检查此模块的状态信号以开始。

是的,tile0_gtp1在使用gtpclkout0(1)和rxrecclk0(我不确定我检查了gtoclkout0(0))的模拟中效果很好。

没有我的设计没有逗号对齐。

我正在使用基于逻辑的DRU和框架......当我使用每个GTP的gtpclkout(1)时,一切都没问题,但我不能与其他GTP共享一个GTP的gtpclkout(1),即使所有线路速率和clks都是

一样。

问候,

马兹

以上来自于谷歌翻译

以下为原文

Srinadh,

Thanks.

gtpclkout0(0) is for Tx and gtpclkout0(1) is for Rx.

From UG386,

It is said that REFCLKPLL can be ouput to FPGA logic via gtpclkout0(0), But you are right. If we "only" consider the frequency this clock is the same as rxrecclk in my design.

Do you find the design working in simulation? if you are using comma alignment, check the status signals of this module to start with.

Yes the tile0_gtp1 works well in simulation with gtpclkout0(1) and rxrecclk0 (I am not sure I checked the gtoclkout0(0)).

And no my desing doesn't have comma alignment. I am using a logic based DRU and framing and .... Everything is okay when I use each GTP's gtpclkout(1), but I cannot share one GTP's gtpclkout(1) with other GTPs, even though all the line rates and clks are the same.

Regards,

Maz

Srinadh,

谢谢。

gtpclkout0(0)用于Tx,gtpclkout0(1)用于Rx。

来自UG386,

据说REFCLKPLL可以通过gtpclkout0(0)输出到FPGA逻辑,但你是对的。

如果我们“只”考虑频率,那么这个时钟与我设计中的rxrecclk相同。

你发现设计在模拟中工作吗?

如果您使用逗号对齐,请检查此模块的状态信号以开始。

是的,tile0_gtp1在使用gtpclkout0(1)和rxrecclk0(我不确定我检查了gtoclkout0(0))的模拟中效果很好。

没有我的设计没有逗号对齐。

我正在使用基于逻辑的DRU和框架......当我使用每个GTP的gtpclkout(1)时,一切都没问题,但我不能与其他GTP共享一个GTP的gtpclkout(1),即使所有线路速率和clks都是

一样。

问候,

马兹

以上来自于谷歌翻译

以下为原文

Srinadh,

Thanks.

gtpclkout0(0) is for Tx and gtpclkout0(1) is for Rx.

From UG386,

It is said that REFCLKPLL can be ouput to FPGA logic via gtpclkout0(0), But you are right. If we "only" consider the frequency this clock is the same as rxrecclk in my design.

Do you find the design working in simulation? if you are using comma alignment, check the status signals of this module to start with.

Yes the tile0_gtp1 works well in simulation with gtpclkout0(1) and rxrecclk0 (I am not sure I checked the gtoclkout0(0)).

And no my desing doesn't have comma alignment. I am using a logic based DRU and framing and .... Everything is okay when I use each GTP's gtpclkout(1), but I cannot share one GTP's gtpclkout(1) with other GTPs, even though all the line rates and clks are the same.

Regards,

Maz

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报