我试图从图5中的XAPP1064实现ISERDES设计,它使用差分输入和PLL。

我使用的Xilinx代码几乎没有动过。

我已经模拟了它的行为,但我无法快速模拟后期地图。

在307Mhz和310Mhz的PLL输出之间,它会发生故障。

在一个单独的项目中,我成功创建了一个没有ISERDES块的PLL。

最近我将其简化为单个ISERDES块和带有缓冲区的PLL,不包括IODELAY。

我得到了相同的结果。

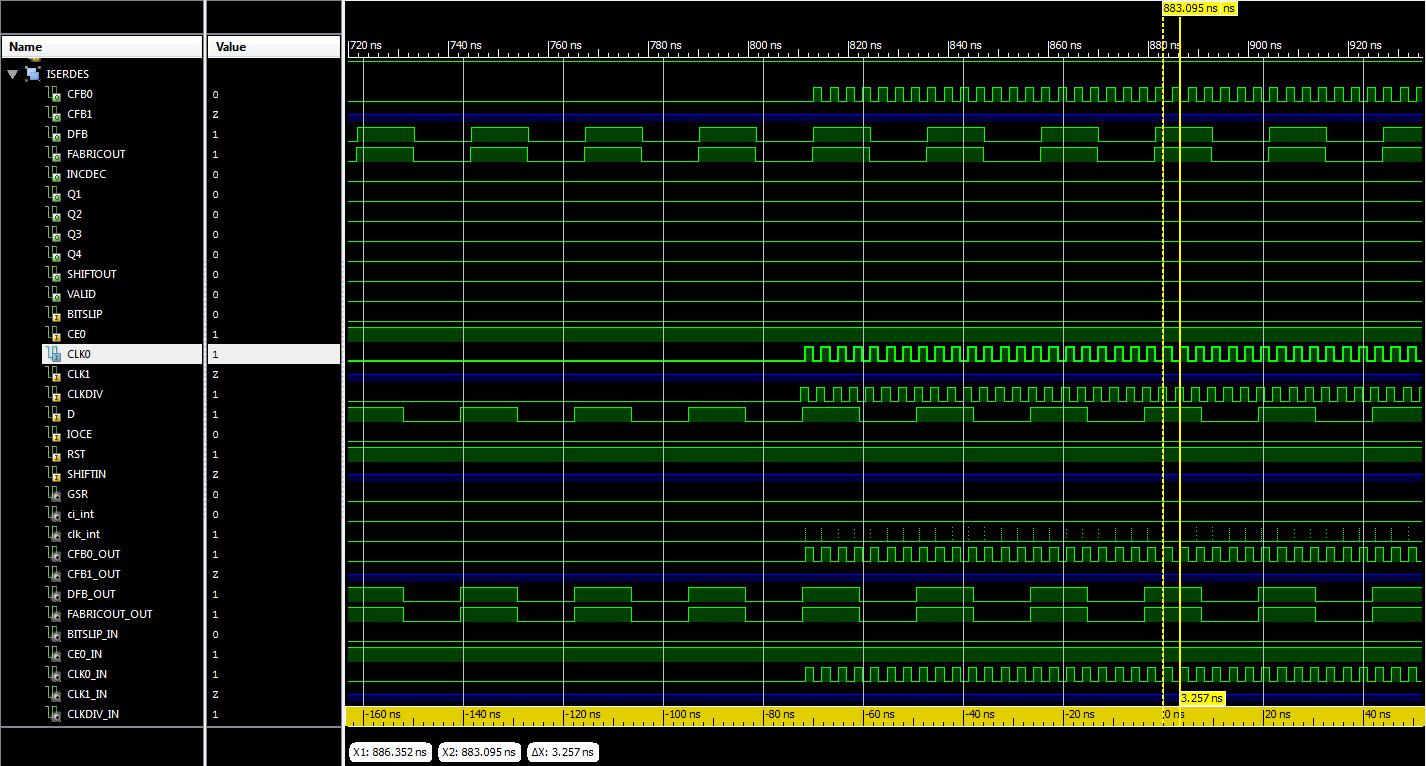

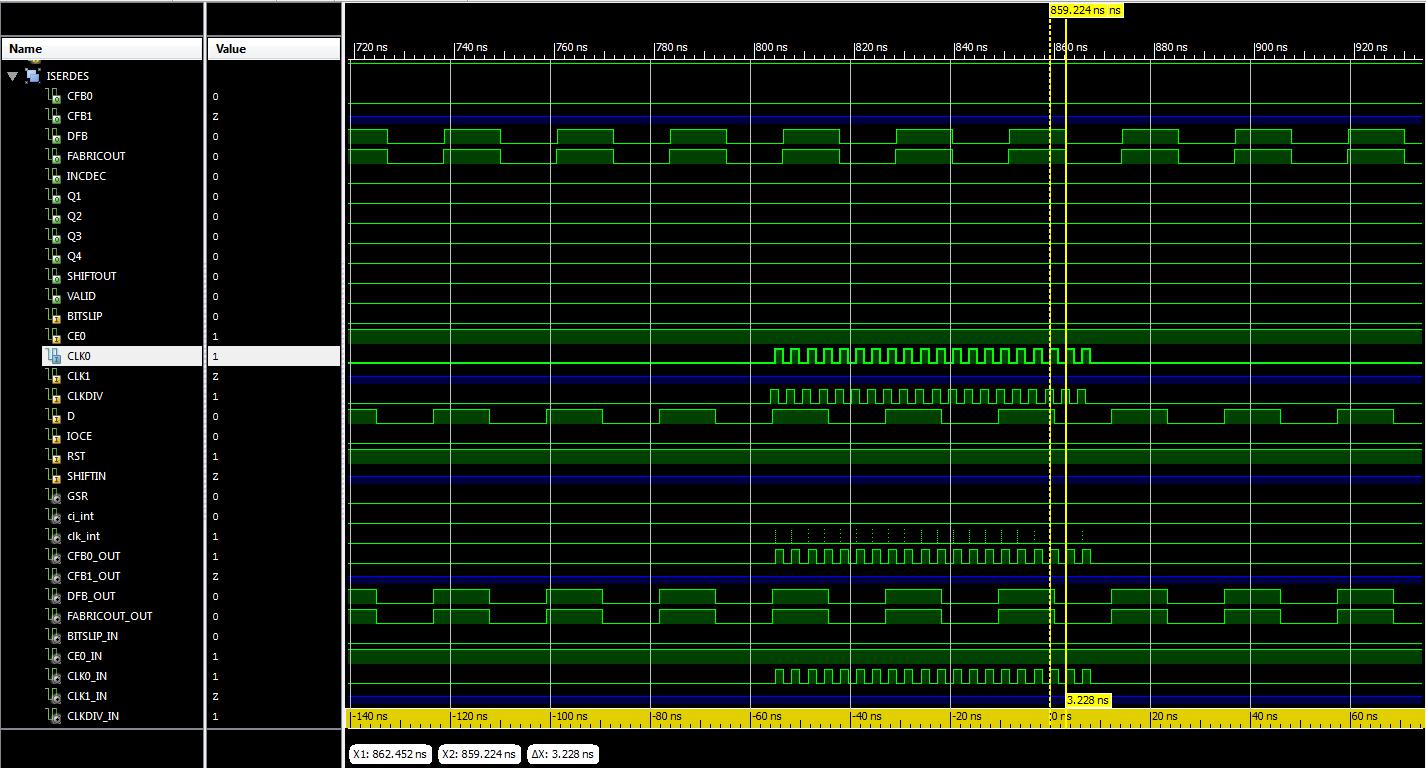

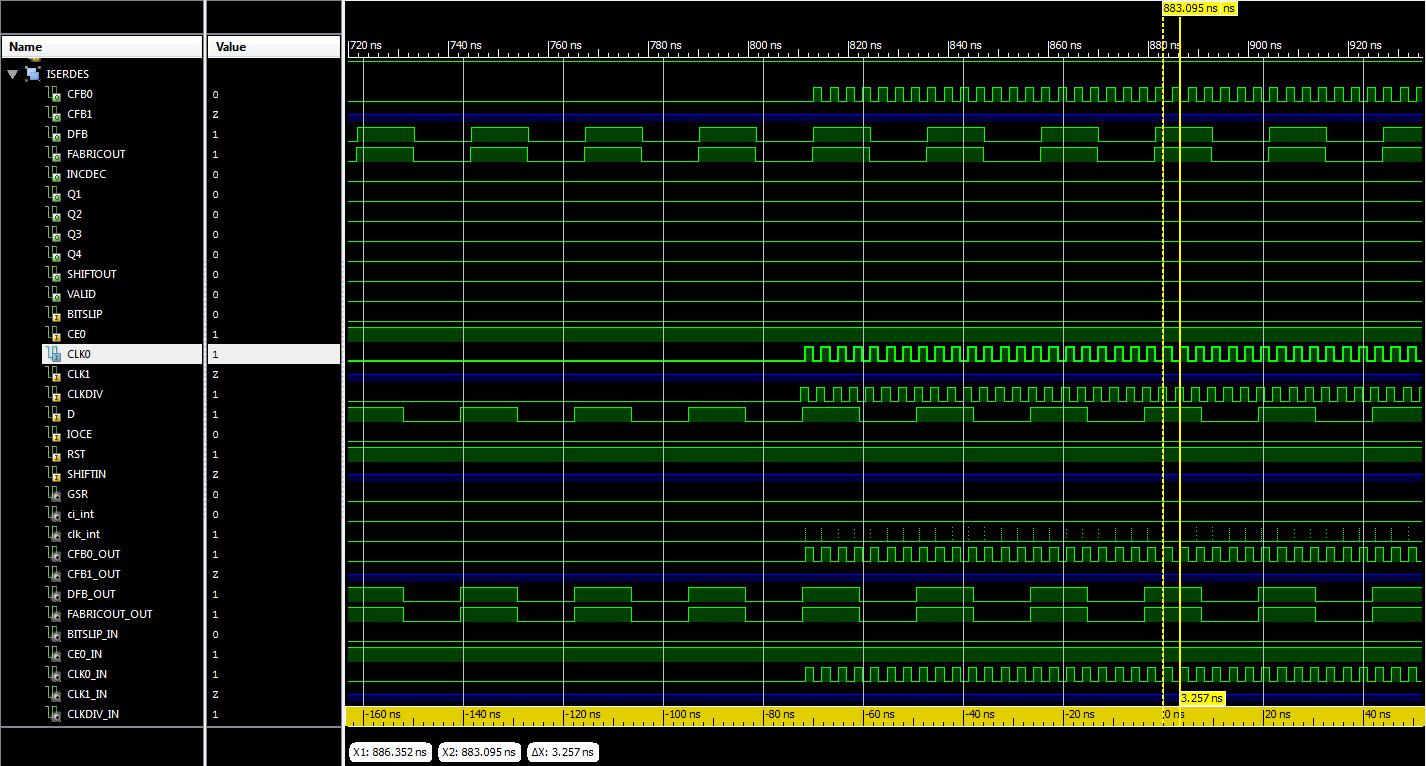

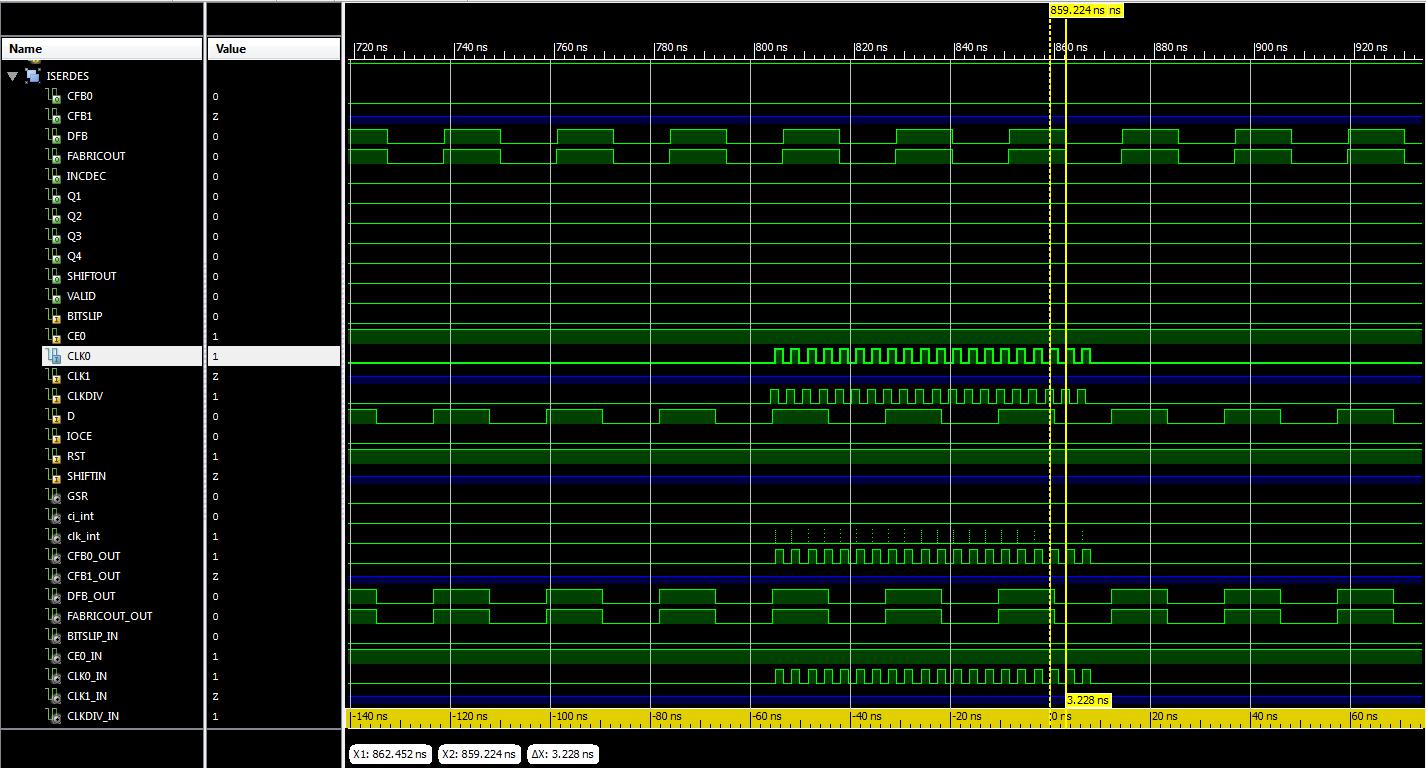

我在下面放了两个屏幕截图,一个在307Mhz,另一个在310Mhz。

对我来说,ISERDES反馈输出(CFB0)就是它发生故障的地方。

实际上,CFB0_OUT内部连接工作的时间很短,但不是CFB0。

我使用的是IDE 14.4和Spartan 6 XC6SLX9。

还有其他人遇到过这个问题吗?

关于可能出现什么问题的任何想法?

谢谢!

以上来自于谷歌翻译

以下为原文

I am trying to implement the ISERDES design from XAPP1064, Fig. 5, which uses differen

tial inputs and the PLL. I am using the Xilinx code almost untouched. I have simulated it behaviorally but am unable to simulate post map at speed. Somewhere between PLL output of 307Mhz and 310Mhz it breaks down. In a separate project I successfully created a PLL without the ISERDES blocks. And most recently I simplified it down to a single ISERDES block and the PLL with buffers, excluding the IODELAYs. I get the same result. I included two screen shots below, one at 307Mhz and the other at 310Mhz. It looks like to me that the ISERDES feedback output (CFB0) is where it breaks down. In fact, the CFB0_OUT internal connection is working for a short time, but not CFB0. I am using IDE version 14.4 and the Spartan 6 XC6SLX9. Has anyone else experienced this problem? Any thoughts on what might be the issue? Thanks!

举报

举报

举报

举报

举报

举报