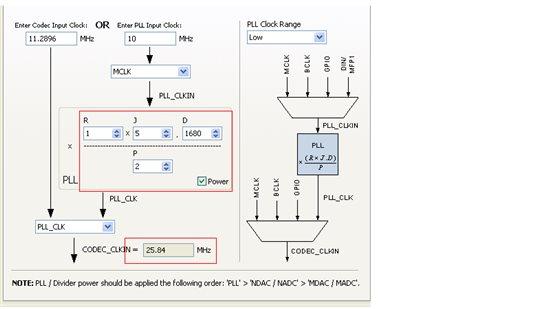

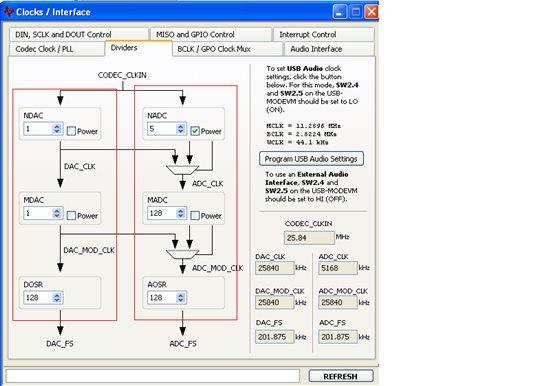

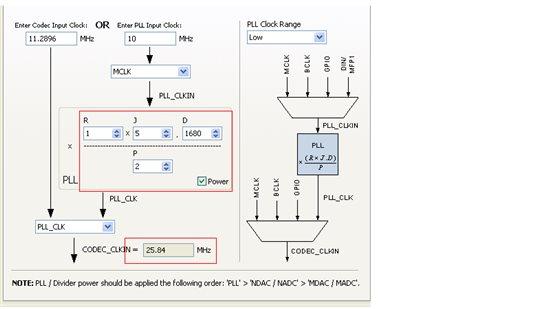

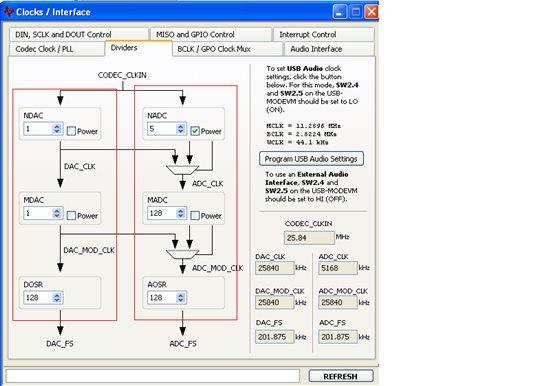

我将你的代码数据放到我们的EVM板上测试,发现你的PLL与Divider设置有问题。

这个系数是你们需要的吗?并且没有power

on divider。

还有就是你们的配置时序也有点问题。建议参考如下顺序:

page 0 is selected

w

30 00 00

reg[ 0][ 1] = 0x01 ; Initialize the device through software reset

01

---------------------------------------------------------------

page 1 is selected

w

30 00 01

reg[ 1][ 1] = 0x08 ; Disable weak AVDD to DVDD connection

08

reg[ 1][ 2] = 0x00 ; Enable Master Analog Power Control

00

reg[ 1][ 71] = 0x32 ; Set the input power-up time to 3.1ms

w

30 47 32

reg[ 1][123] = 0x05 ; Force REF charging time to 40ms

w

30 7b 05

---------------------------------------------------------------

page 0 is selected

w

30 00 00

reg[ 0][ 5] = 0x91 ; P=1, R=1, J=24

w

30 05 91

reg[ 0][ 6] = 0x18 ; P=1, R=1, J=24

18

reg[ 0][ 7] = 0x00 ; D=0000 (MSB)

00

reg[ 0][ 8] = 0x00 ; D=0000 (LSB)

00

reg[ 0][ 4] = 0x03 ; PLL_clkin = MCLK, codec_clkin = PLL_CLK, PLL on

w

30 04 03

reg[ 0][254] = 0x0a ; Delay 10ms for PLL to lock

w

30 fe 0a

reg[ 0][ 12] = 0x88 ; MDAC = 8, divider powered on

w

30 0c 88

reg[ 0][ 13] = 0x03 ; DOSR = 768 (MSB)

03

reg[ 0][ 14] = 0x00 ; DOSR = 768 (LSB)

00

reg[ 0][ 18] = 0x02 ; NADC = 2, divider powered off

w

30 12 02

reg[ 0][ 19] = 0xb0 ; MADC = 48, divider powered on

b0

reg[ 0][ 20] = 0x80 ; AOSR = 128

80

reg[ 0][ 11] = 0x82 ; NDAC = 2, divider powered on

w

30 0b 82

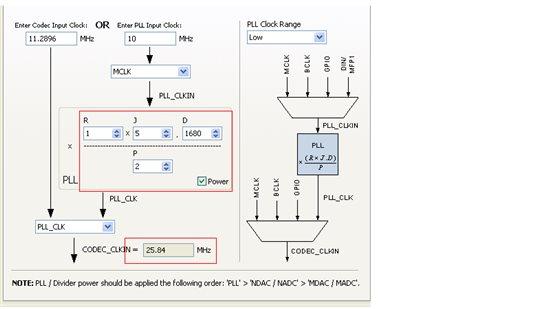

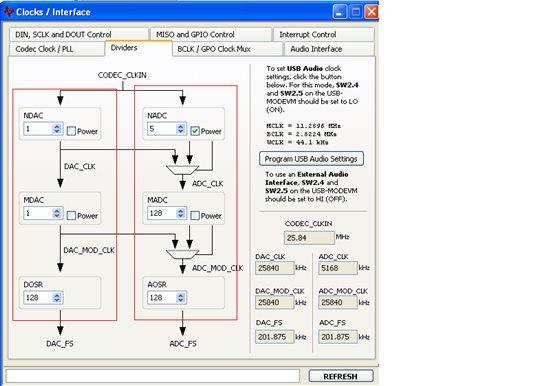

我将你的代码数据放到我们的EVM板上测试,发现你的PLL与Divider设置有问题。

这个系数是你们需要的吗?并且没有power

on divider。

还有就是你们的配置时序也有点问题。建议参考如下顺序:

page 0 is selected

w

30 00 00

reg[ 0][ 1] = 0x01 ; Initialize the device through software reset

01

---------------------------------------------------------------

page 1 is selected

w

30 00 01

reg[ 1][ 1] = 0x08 ; Disable weak AVDD to DVDD connection

08

reg[ 1][ 2] = 0x00 ; Enable Master Analog Power Control

00

reg[ 1][ 71] = 0x32 ; Set the input power-up time to 3.1ms

w

30 47 32

reg[ 1][123] = 0x05 ; Force REF charging time to 40ms

w

30 7b 05

---------------------------------------------------------------

page 0 is selected

w

30 00 00

reg[ 0][ 5] = 0x91 ; P=1, R=1, J=24

w

30 05 91

reg[ 0][ 6] = 0x18 ; P=1, R=1, J=24

18

reg[ 0][ 7] = 0x00 ; D=0000 (MSB)

00

reg[ 0][ 8] = 0x00 ; D=0000 (LSB)

00

reg[ 0][ 4] = 0x03 ; PLL_clkin = MCLK, codec_clkin = PLL_CLK, PLL on

w

30 04 03

reg[ 0][254] = 0x0a ; Delay 10ms for PLL to lock

w

30 fe 0a

reg[ 0][ 12] = 0x88 ; MDAC = 8, divider powered on

w

30 0c 88

reg[ 0][ 13] = 0x03 ; DOSR = 768 (MSB)

03

reg[ 0][ 14] = 0x00 ; DOSR = 768 (LSB)

00

reg[ 0][ 18] = 0x02 ; NADC = 2, divider powered off

w

30 12 02

reg[ 0][ 19] = 0xb0 ; MADC = 48, divider powered on

b0

reg[ 0][ 20] = 0x80 ; AOSR = 128

80

reg[ 0][ 11] = 0x82 ; NDAC = 2, divider powered on

w

30 0b 82

举报

举报

举报

举报

举报

举报