千兆网输入与输出模块的设计

gbit_top模块:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : nnzhang1996@foxmail.com

// Website :

// Module Name : gbit_top.v

// Create Time : 2020-03-17 09:43:00

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module gbit_top(

//System Interfaces

input sclk ,

input rst_n ,

//Gigbit Interfaces

output reg phy_rst_n ,

input [ 3:0] rx_data ,

input rx_ctrl ,

input rx_clk

);

//========================================================================================

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

reg [20:0] phy_rst_cnt ;

wire rx_clk_90 ;

//iddr_ctrl_inst

wire [ 7:0] gb_rx_data ;

wire gb_rx_data_en ;

wire gb_rx_data_err ;

//========================================================================================

//************** Main Code **********************************

//========================================================================================/

clk_wiz_0 clk_wiz_0_inst(

// Clock out ports

.clk_out1 (rx_clk_90 ), // output clk_out1

// Clock in ports

.clk_in1 (rx_clk )

);

iddr_ctrl iddr_ctrl_inst(

//System Interfaces

.rst_n (rst_n ),

//Gigabit Interfaces

.rx_data (rx_data ),

.rx_ctrl (rx_ctrl ),

.rx_clk (rx_clk_90 ),

//Communication Interfaces

.gb_rx_data (gb_rx_data ),

.gb_rx_data_en (gb_rx_data_en ),

.gb_rx_data_err (gb_rx_data_err )

);

always @(posedge sclk or negedge rst_n)

if(rst_n == 1‘b0)

phy_rst_cnt 《= 21’d0;

else if(phy_rst_cnt[20] == 1‘b0)

phy_rst_cnt 《= phy_rst_cnt + 1’b1;

else

phy_rst_cnt 《= phy_rst_cnt;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1‘b0)

phy_rst_n 《= 1’b0;

else if(phy_rst_cnt[20] == 1‘b1)

phy_rst_n 《= 1’b1;

else

phy_rst_n 《= phy_rst_n;

endmodule

1234567891011121314151617181920212223242526272829303132333435363738394041424344454647484950515253545556575859606162636465666768697071727374757677787980818283

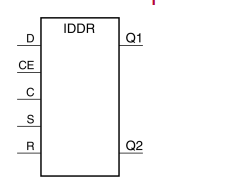

iddr_ctrl模块

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : nnzhang1996@foxmail.com

// Website :

// Module Name : iddr_ctrl.v

// Create Time : 2020-03-17 09:21:20

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module iddr_ctrl(

//System Interfaces

input rst_n ,

//Gigabit Interfaces

input [ 3:0] rx_data ,

input rx_ctrl ,

input rx_clk ,

//Communication Interfaces

output reg [ 7:0] gb_rx_data ,

output reg gb_rx_data_en ,

output reg gb_rx_data_err

);

//========================================================================================

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

wire [ 7:0] data ;

wire data_en ;

wire data_err ;

//========================================================================================

//************** Main Code **********************************

//========================================================================================/

IDDR #(

.DDR_CLK_EDGE (“OPPOSITE_EDGE” ), // “OPPOSITE_EDGE”, “SAME_EDGE”

// or “SAME_EDGE_PIPELINED”

.INIT_Q1 (1‘b0 ), // Initial value of Q1: 1’b0 or 1‘b1

.INIT_Q2 (1’b0 ), // Initial value of Q2: 1‘b0 or 1’b1

.SRTYPE (“SYNC” ) // Set/Reset type: “SYNC” or “ASYNC”

) IDDR_ctrl (

.Q1 (data_en ), // 1-bit output for positive edge of clock

.Q2 (data_err ), // 1-bit output for negative edge of clock

.C (rx_clk ), // 1-bit clock input

.CE (1‘b1 ), // 1-bit clock enable input

.D (rx_ctrl ), // 1-bit DDR data input

.R (~rst_n ), // 1-bit reset

.S (1’b0 ) // 1-bit set

);

genvar i;

generate

for (i = 0; i 《 4; i = i+1) begin

IDDR #(

.DDR_CLK_EDGE (“OPPOSITE_EDGE” ), // “OPPOSITE_EDGE”, “SAME_EDGE”

// or “SAME_EDGE_PIPELINED”

.INIT_Q1 (1‘b0 ), // Initial value of Q1: 1’b0 or 1‘b1

.INIT_Q2 (1’b0 ), // Initial value of Q2: 1‘b0 or 1’b1

.SRTYPE (“SYNC” ) // Set/Reset type: “SYNC” or “ASYNC”

) IDDR_ctrl (

.Q1 (data[i] ), // 1-bit output for positive edge of clock

.Q2 (data[4+i] ), // 1-bit output for negative edge of clock

.C (rx_clk ), // 1-bit clock input

.CE (1‘b1 ), // 1-bit clock enable input

.D (rx_data[i] ), // 1-bit DDR data input

.R (~rst_n ), // 1-bit reset

.S (1’b0 ) // 1-bit set

);

end

endgenerate

always @(posedge rx_clk or negedge rst_n)

if(rst_n == 1‘b0)

gb_rx_data 《= 8’d0;

else

gb_rx_data 《= data;

always @(posedge rx_clk or negedge rst_n)

if(rst_n == 1‘b0)

gb_rx_data_err 《= 1’b0;

else

gb_rx_data_err 《= data_err;

always @(posedge rx_clk or negedge rst_n)

if(rst_n == 1‘b0)

gb_rx_data_en 《= 1’b0;

else

gb_rx_data_en 《= data_en;

endmodule

123456789101112131415161718192021222324252627282930313233343536373839404142434445464748495051525354555657585960616263646566676869707172737475767778798081828384858687888990919293949596979899100

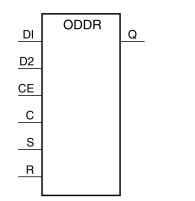

oddr_ctrl模块

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : nnzhang1996@foxmail.com

// Website :

// Module Name : oddr_ctrl.v

// Create Time : 2020-03-17 09:56:53

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module oddr_ctrl(

//System Interfaces

input rst_n ,

//Gigbit Interfaces

output wire [ 3:0] tx_data ,

output wire tx_data_ctrl ,

output wire tx_clk ,

//Communication Interfaces

input [ 7:0] gb_tx_data ,

input gb_tx_data_en ,

input gb_tx_data_err ,

input gb_tx_clk

);

//========================================================================================

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

//========================================================================================

//************** Main Code **********************************

//========================================================================================/

ODDR #(

.DDR_CLK_EDGE (“SAME_EDGE” ), // “OPPOSITE_EDGE” or “SAME_EDGE”

.INIT (1‘b0 ), // Initial value of Q: 1’b0 or 1‘b1

.SRTYPE (“SYNC” ) // Set/Reset type: “SYNC” or “ASYNC”

) ODDR_ctrl (

.Q (tx_data_ctrl ), // 1-bit DDR output

.C (gb_tx_clk ), // 1-bit clock input

.CE (1’b1 ), // 1-bit clock enable input

.D1 (gb_tx_data_en ), // 1-bit data input (positive edge)

.D2 (gb_tx_data_err ), // 1-bit data input (negative edge)

.R (~rst_n ), // 1-bit reset

.S (1‘b0 ) // 1-bit set

);

ODDR #(

.DDR_CLK_EDGE (“SAME_EDGE” ), // “OPPOSITE_EDGE” or “SAME_EDGE”

.INIT (1’b0 ), // Initial value of Q: 1‘b0 or 1’b1

.SRTYPE (“SYNC” ) // Set/Reset type: “SYNC” or “ASYNC”

) ODDR_clk (

.Q (tx_clk ), // 1-bit DDR output

.C (gb_tx_clk ), // 1-bit clock input

.CE (1‘b1 ), // 1-bit clock enable input

.D1 (1’b1 ), // 1-bit data input (positive edge)

.D2 (1‘b0 ), // 1-bit data input (negative edge)

.R (~rst_n ), // 1-bit reset

.S (1’b0 ) // 1-bit set

);

genvar i;

generate

for (i = 0; i 《 4; i = i+1) begin

ODDR #(

.DDR_CLK_EDGE (“SAME_EDGE” ), // “OPPOSITE_EDGE” or “SAME_EDGE”

.INIT (1‘b0 ), // Initial value of Q: 1’b0 or 1‘b1

.SRTYPE (“SYNC” ) // Set/Reset type: “SYNC” or “ASYNC”

) ODDR_data (

.Q (tx_data[i] ), // 1-bit DDR output

.C (gb_tx_clk ), // 1-bit clock input

.CE (1’b1 ), // 1-bit clock enable input

.D1 (gb_tx_data[i] ), // 1-bit data input (positive edge)

.D2 (gb_tx_data[4+i] ), // 1-bit data input (negative edge)

.R (~rst_n ), // 1-bit reset

.S (1‘b0 ) // 1-bit set

);

end

endgenerate

endmodule

千兆网输入与输出模块的设计

gbit_top模块:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : nnzhang1996@foxmail.com

// Website :

// Module Name : gbit_top.v

// Create Time : 2020-03-17 09:43:00

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module gbit_top(

//System Interfaces

input sclk ,

input rst_n ,

//Gigbit Interfaces

output reg phy_rst_n ,

input [ 3:0] rx_data ,

input rx_ctrl ,

input rx_clk

);

//========================================================================================

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

reg [20:0] phy_rst_cnt ;

wire rx_clk_90 ;

//iddr_ctrl_inst

wire [ 7:0] gb_rx_data ;

wire gb_rx_data_en ;

wire gb_rx_data_err ;

//========================================================================================

//************** Main Code **********************************

//========================================================================================/

clk_wiz_0 clk_wiz_0_inst(

// Clock out ports

.clk_out1 (rx_clk_90 ), // output clk_out1

// Clock in ports

.clk_in1 (rx_clk )

);

iddr_ctrl iddr_ctrl_inst(

//System Interfaces

.rst_n (rst_n ),

//Gigabit Interfaces

.rx_data (rx_data ),

.rx_ctrl (rx_ctrl ),

.rx_clk (rx_clk_90 ),

//Communication Interfaces

.gb_rx_data (gb_rx_data ),

.gb_rx_data_en (gb_rx_data_en ),

.gb_rx_data_err (gb_rx_data_err )

);

always @(posedge sclk or negedge rst_n)

if(rst_n == 1‘b0)

phy_rst_cnt 《= 21’d0;

else if(phy_rst_cnt[20] == 1‘b0)

phy_rst_cnt 《= phy_rst_cnt + 1’b1;

else

phy_rst_cnt 《= phy_rst_cnt;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1‘b0)

phy_rst_n 《= 1’b0;

else if(phy_rst_cnt[20] == 1‘b1)

phy_rst_n 《= 1’b1;

else

phy_rst_n 《= phy_rst_n;

endmodule

1234567891011121314151617181920212223242526272829303132333435363738394041424344454647484950515253545556575859606162636465666768697071727374757677787980818283

iddr_ctrl模块

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : nnzhang1996@foxmail.com

// Website :

// Module Name : iddr_ctrl.v

// Create Time : 2020-03-17 09:21:20

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module iddr_ctrl(

//System Interfaces

input rst_n ,

//Gigabit Interfaces

input [ 3:0] rx_data ,

input rx_ctrl ,

input rx_clk ,

//Communication Interfaces

output reg [ 7:0] gb_rx_data ,

output reg gb_rx_data_en ,

output reg gb_rx_data_err

);

//========================================================================================

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

wire [ 7:0] data ;

wire data_en ;

wire data_err ;

//========================================================================================

//************** Main Code **********************************

//========================================================================================/

IDDR #(

.DDR_CLK_EDGE (“OPPOSITE_EDGE” ), // “OPPOSITE_EDGE”, “SAME_EDGE”

// or “SAME_EDGE_PIPELINED”

.INIT_Q1 (1‘b0 ), // Initial value of Q1: 1’b0 or 1‘b1

.INIT_Q2 (1’b0 ), // Initial value of Q2: 1‘b0 or 1’b1

.SRTYPE (“SYNC” ) // Set/Reset type: “SYNC” or “ASYNC”

) IDDR_ctrl (

.Q1 (data_en ), // 1-bit output for positive edge of clock

.Q2 (data_err ), // 1-bit output for negative edge of clock

.C (rx_clk ), // 1-bit clock input

.CE (1‘b1 ), // 1-bit clock enable input

.D (rx_ctrl ), // 1-bit DDR data input

.R (~rst_n ), // 1-bit reset

.S (1’b0 ) // 1-bit set

);

genvar i;

generate

for (i = 0; i 《 4; i = i+1) begin

IDDR #(

.DDR_CLK_EDGE (“OPPOSITE_EDGE” ), // “OPPOSITE_EDGE”, “SAME_EDGE”

// or “SAME_EDGE_PIPELINED”

.INIT_Q1 (1‘b0 ), // Initial value of Q1: 1’b0 or 1‘b1

.INIT_Q2 (1’b0 ), // Initial value of Q2: 1‘b0 or 1’b1

.SRTYPE (“SYNC” ) // Set/Reset type: “SYNC” or “ASYNC”

) IDDR_ctrl (

.Q1 (data[i] ), // 1-bit output for positive edge of clock

.Q2 (data[4+i] ), // 1-bit output for negative edge of clock

.C (rx_clk ), // 1-bit clock input

.CE (1‘b1 ), // 1-bit clock enable input

.D (rx_data[i] ), // 1-bit DDR data input

.R (~rst_n ), // 1-bit reset

.S (1’b0 ) // 1-bit set

);

end

endgenerate

always @(posedge rx_clk or negedge rst_n)

if(rst_n == 1‘b0)

gb_rx_data 《= 8’d0;

else

gb_rx_data 《= data;

always @(posedge rx_clk or negedge rst_n)

if(rst_n == 1‘b0)

gb_rx_data_err 《= 1’b0;

else

gb_rx_data_err 《= data_err;

always @(posedge rx_clk or negedge rst_n)

if(rst_n == 1‘b0)

gb_rx_data_en 《= 1’b0;

else

gb_rx_data_en 《= data_en;

endmodule

123456789101112131415161718192021222324252627282930313233343536373839404142434445464748495051525354555657585960616263646566676869707172737475767778798081828384858687888990919293949596979899100

oddr_ctrl模块

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : nnzhang1996@foxmail.com

// Website :

// Module Name : oddr_ctrl.v

// Create Time : 2020-03-17 09:56:53

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module oddr_ctrl(

//System Interfaces

input rst_n ,

//Gigbit Interfaces

output wire [ 3:0] tx_data ,

output wire tx_data_ctrl ,

output wire tx_clk ,

//Communication Interfaces

input [ 7:0] gb_tx_data ,

input gb_tx_data_en ,

input gb_tx_data_err ,

input gb_tx_clk

);

//========================================================================================

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

//========================================================================================

//************** Main Code **********************************

//========================================================================================/

ODDR #(

.DDR_CLK_EDGE (“SAME_EDGE” ), // “OPPOSITE_EDGE” or “SAME_EDGE”

.INIT (1‘b0 ), // Initial value of Q: 1’b0 or 1‘b1

.SRTYPE (“SYNC” ) // Set/Reset type: “SYNC” or “ASYNC”

) ODDR_ctrl (

.Q (tx_data_ctrl ), // 1-bit DDR output

.C (gb_tx_clk ), // 1-bit clock input

.CE (1’b1 ), // 1-bit clock enable input

.D1 (gb_tx_data_en ), // 1-bit data input (positive edge)

.D2 (gb_tx_data_err ), // 1-bit data input (negative edge)

.R (~rst_n ), // 1-bit reset

.S (1‘b0 ) // 1-bit set

);

ODDR #(

.DDR_CLK_EDGE (“SAME_EDGE” ), // “OPPOSITE_EDGE” or “SAME_EDGE”

.INIT (1’b0 ), // Initial value of Q: 1‘b0 or 1’b1

.SRTYPE (“SYNC” ) // Set/Reset type: “SYNC” or “ASYNC”

) ODDR_clk (

.Q (tx_clk ), // 1-bit DDR output

.C (gb_tx_clk ), // 1-bit clock input

.CE (1‘b1 ), // 1-bit clock enable input

.D1 (1’b1 ), // 1-bit data input (positive edge)

.D2 (1‘b0 ), // 1-bit data input (negative edge)

.R (~rst_n ), // 1-bit reset

.S (1’b0 ) // 1-bit set

);

genvar i;

generate

for (i = 0; i 《 4; i = i+1) begin

ODDR #(

.DDR_CLK_EDGE (“SAME_EDGE” ), // “OPPOSITE_EDGE” or “SAME_EDGE”

.INIT (1‘b0 ), // Initial value of Q: 1’b0 or 1‘b1

.SRTYPE (“SYNC” ) // Set/Reset type: “SYNC” or “ASYNC”

) ODDR_data (

.Q (tx_data[i] ), // 1-bit DDR output

.C (gb_tx_clk ), // 1-bit clock input

.CE (1’b1 ), // 1-bit clock enable input

.D1 (gb_tx_data[i] ), // 1-bit data input (positive edge)

.D2 (gb_tx_data[4+i] ), // 1-bit data input (negative edge)

.R (~rst_n ), // 1-bit reset

.S (1‘b0 ) // 1-bit set

);

end

endgenerate

endmodule

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报