“现在,根据我的理解 - 这8 - (xyz + 3.8)ns必须超过FPGA架构中FF的Tsetup。

8 - (xyz + 3.8)> FPGA中的FF的Tsetup,然后该工具将给出时序违规,即因为输入路径很长,当输入数据到达FF时,数据在设置窗口内转换

clk边缘 - 因此失败。

“

我认为正确的说法是:

如果8 - (xyz + 3.8)小于FPGA中FF的Tsetup,则该工具将给出时序违规,即因为输入路径非常长,当输入数据到达FF时,数据正在内部转换

clk边缘的设置窗口 - 因此失败。

但请记住,实际的Tsetup是通过从引脚(时钟和数据)到触发器的内部路由计算出来的。

如果您的FF锁定在IOB中,那么工具无法尝试改善设置或保持时间,它们只能报告实际的松弛(如果失败则为负)。

如果FF位于结构中,则工具可以使用路由延迟来修复某些类型的设置或保留问题。

默认综合设置“自动”允许工具根据时序要求决定FF应该在结构中还是IOB中。

“我的问题是 - 在CLK上升之前使用-OFFSET = IN 4.2 ns VALID 4.8 ns之间是否有任何特别的优势;在CLK上升之前VsOFFSET = IN 4.2 ns之间有什么特别的优势;?”

如果没有约束的VALID部分,工具将仅检查设置时间。

我不记得这些工具是否完全忽略了保持时间或者假设它为零。

在任何情况下,最好指出实际可用的保持时间,以便工具可以更好地决定FF放置和相关时间。

“此外,我的外部设备(生成输入数据和clk)进入FPGA - 也是一个FPGA。

那么我应该看一下数据表中的哪个部分来获得FPGA的clk-q延迟时间(我看到几个clk-q字段)?“

如果另一个器件是Xilinx FPGA,那么通常您可以从最后一个P& R时序报告的“数据表”部分获得此信息。

请注意,如果FPGA提供时钟和数据,则需要将包括时钟转发ODDR的所有输出FFS锁定到IOB中。

在论坛中搜索“source synchronous”以获取有关在此配置中进行稳健输出计时的更多信息。

如果您的数据输出“单数据速率”并且您在时钟上升沿接收数据,则标准做法是将ODDR用作反相时钟转发器,方法是将上升沿D连接到“0”并且下降 -

边D到'1'。

这将上升时钟边沿置于数据位周期的中心。

OFFSET OUT约束后,从FPGA引脚的时钟输入到FPGA引脚的数据输出有一个最大延迟。

如果将输出FF放在IOB中,除了告诉您设计是否满足时序外,它实际上什么都不做 - 它不能改变时钟输出时序。

如果您的输出FF在FPGA架构中或不受约束,那么这些工具有一些余地来尝试修复输出时序。

没有OFFSET OUT约束可以对输出延迟施加最小时钟。

这就是为什么你需要仔细地将所有输出放在IOB中以获得源同步设计的可用输出时序,其中FPGA驱动时钟和数据。

- Gabor

以上来自于谷歌翻译

以下为原文

"now, as per my understanding - this 8 - (xyz + 3.8) ns has to be more than the Tsetup of the FF in the FPGA fabric. if

8 - (xyz + 3.8) > Tsetup of the FF in the FPGA, then the tool will give a timing violation i.e. because input path is very long, by the time the input data reaches the FF, the data is transitioning inside the setup window of the clk edge - hence a failure. "

I think the correct way to say thie is:

if 8 - (xyz + 3.8)

is less than Tsetup of the FF in the FPGA, then the tool will give a timing violation i.e. because input path is very long, by the time the input data reaches the FF, the data is transitioning inside the setup window of the clk edge - hence a failure.

Remember however that the actual Tsetup is calculated with the internal routing from the pins (clock and data) to the flip-flop already taken into account. If your FF is locked into the IOB, then there is nothing the tools can do to try to improve setup or hold time, they can only report the actual slack (negative if failing). If the FF is in the fabric, the tools can use routing delays to fix some kinds of setup or hold issues. The default synthesis setting of "Auto" allows the tools to decide whether the FF should be in the fabric or the IOB based on timing requirements.

"my question is - is there any particular advantage between using - OFFSET = IN 4.2 ns VALID 4.8 ns BEFORE CLK RISING ; Vs OFFSET = IN 4.2 ns BEFORE CLK RISING ;?"

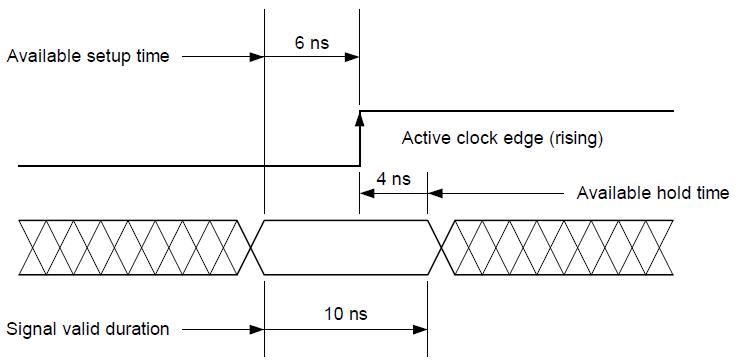

Without the VALID part of the constraint, the tools will only check for setup time. I don't remember if the tools totally ignore hold time or assume it to be zero. In any case it is better to indicate the actual available hold time so the tools can make a better decision about FF placement and related timing.

"Also, my external device (which is generating the input data and clk) going into the FPGA - is ALSO an FPGA.

so which section in the datasheet should I look at to get any time of clk-q delay for the FPGAs (i see several clk-q fields)?"

If the other device is a Xilinx FPGA, then normally you get this information from the "datasheet" section of the final post P&R timing report. Note that if the FPGA is sourcing the clock as well as the data, you need to lock all output FFS including the clock-forwarding ODDR into the IOBs. Search the forums for "source synchronous" to get more information about making robust output timing in this configuration. If your data is going out "single data rate" and you receive it on the rising clock edge, the standard practice is to use the ODDR as an inverting clock-forwarder by tying the rising-edge D to '0' and the falling-edge D to '1'. This places the rising clock edge in the center of the data bit period.

OFFSET OUT AFTER constraints place a maximum delay from the clock input at the FPGA pin to the data output at the FPGA pin. If you place your output FFs in the IOB, it really doesn't do anything except tell you whether the design met timing - it can't change the clock to output timing. If your output FFs are in the FPGA fabric or unconstrained, the tools have some leeway to try to fix output timing. There is no OFFSET OUT constraint that can impose a minimum clock to output delay. That's why you need to carefully place all outputs in the IOBs to get a usable output timing for source-synchronous designs, where the FPGA drives both clock and data.

-- Gabor

“现在,根据我的理解 - 这8 - (xyz + 3.8)ns必须超过FPGA架构中FF的Tsetup。

8 - (xyz + 3.8)> FPGA中的FF的Tsetup,然后该工具将给出时序违规,即因为输入路径很长,当输入数据到达FF时,数据在设置窗口内转换

clk边缘 - 因此失败。

“

我认为正确的说法是:

如果8 - (xyz + 3.8)小于FPGA中FF的Tsetup,则该工具将给出时序违规,即因为输入路径非常长,当输入数据到达FF时,数据正在内部转换

clk边缘的设置窗口 - 因此失败。

但请记住,实际的Tsetup是通过从引脚(时钟和数据)到触发器的内部路由计算出来的。

如果您的FF锁定在IOB中,那么工具无法尝试改善设置或保持时间,它们只能报告实际的松弛(如果失败则为负)。

如果FF位于结构中,则工具可以使用路由延迟来修复某些类型的设置或保留问题。

默认综合设置“自动”允许工具根据时序要求决定FF应该在结构中还是IOB中。

“我的问题是 - 在CLK上升之前使用-OFFSET = IN 4.2 ns VALID 4.8 ns之间是否有任何特别的优势;在CLK上升之前VsOFFSET = IN 4.2 ns之间有什么特别的优势;?”

如果没有约束的VALID部分,工具将仅检查设置时间。

我不记得这些工具是否完全忽略了保持时间或者假设它为零。

在任何情况下,最好指出实际可用的保持时间,以便工具可以更好地决定FF放置和相关时间。

“此外,我的外部设备(生成输入数据和clk)进入FPGA - 也是一个FPGA。

那么我应该看一下数据表中的哪个部分来获得FPGA的clk-q延迟时间(我看到几个clk-q字段)?“

如果另一个器件是Xilinx FPGA,那么通常您可以从最后一个P& R时序报告的“数据表”部分获得此信息。

请注意,如果FPGA提供时钟和数据,则需要将包括时钟转发ODDR的所有输出FFS锁定到IOB中。

在论坛中搜索“source synchronous”以获取有关在此配置中进行稳健输出计时的更多信息。

如果您的数据输出“单数据速率”并且您在时钟上升沿接收数据,则标准做法是将ODDR用作反相时钟转发器,方法是将上升沿D连接到“0”并且下降 -

边D到'1'。

这将上升时钟边沿置于数据位周期的中心。

OFFSET OUT约束后,从FPGA引脚的时钟输入到FPGA引脚的数据输出有一个最大延迟。

如果将输出FF放在IOB中,除了告诉您设计是否满足时序外,它实际上什么都不做 - 它不能改变时钟输出时序。

如果您的输出FF在FPGA架构中或不受约束,那么这些工具有一些余地来尝试修复输出时序。

没有OFFSET OUT约束可以对输出延迟施加最小时钟。

这就是为什么你需要仔细地将所有输出放在IOB中以获得源同步设计的可用输出时序,其中FPGA驱动时钟和数据。

- Gabor

以上来自于谷歌翻译

以下为原文

"now, as per my understanding - this 8 - (xyz + 3.8) ns has to be more than the Tsetup of the FF in the FPGA fabric. if

8 - (xyz + 3.8) > Tsetup of the FF in the FPGA, then the tool will give a timing violation i.e. because input path is very long, by the time the input data reaches the FF, the data is transitioning inside the setup window of the clk edge - hence a failure. "

I think the correct way to say thie is:

if 8 - (xyz + 3.8)

is less than Tsetup of the FF in the FPGA, then the tool will give a timing violation i.e. because input path is very long, by the time the input data reaches the FF, the data is transitioning inside the setup window of the clk edge - hence a failure.

Remember however that the actual Tsetup is calculated with the internal routing from the pins (clock and data) to the flip-flop already taken into account. If your FF is locked into the IOB, then there is nothing the tools can do to try to improve setup or hold time, they can only report the actual slack (negative if failing). If the FF is in the fabric, the tools can use routing delays to fix some kinds of setup or hold issues. The default synthesis setting of "Auto" allows the tools to decide whether the FF should be in the fabric or the IOB based on timing requirements.

"my question is - is there any particular advantage between using - OFFSET = IN 4.2 ns VALID 4.8 ns BEFORE CLK RISING ; Vs OFFSET = IN 4.2 ns BEFORE CLK RISING ;?"

Without the VALID part of the constraint, the tools will only check for setup time. I don't remember if the tools totally ignore hold time or assume it to be zero. In any case it is better to indicate the actual available hold time so the tools can make a better decision about FF placement and related timing.

"Also, my external device (which is generating the input data and clk) going into the FPGA - is ALSO an FPGA.

so which section in the datasheet should I look at to get any time of clk-q delay for the FPGAs (i see several clk-q fields)?"

If the other device is a Xilinx FPGA, then normally you get this information from the "datasheet" section of the final post P&R timing report. Note that if the FPGA is sourcing the clock as well as the data, you need to lock all output FFS including the clock-forwarding ODDR into the IOBs. Search the forums for "source synchronous" to get more information about making robust output timing in this configuration. If your data is going out "single data rate" and you receive it on the rising clock edge, the standard practice is to use the ODDR as an inverting clock-forwarder by tying the rising-edge D to '0' and the falling-edge D to '1'. This places the rising clock edge in the center of the data bit period.

OFFSET OUT AFTER constraints place a maximum delay from the clock input at the FPGA pin to the data output at the FPGA pin. If you place your output FFs in the IOB, it really doesn't do anything except tell you whether the design met timing - it can't change the clock to output timing. If your output FFs are in the FPGA fabric or unconstrained, the tools have some leeway to try to fix output timing. There is no OFFSET OUT constraint that can impose a minimum clock to output delay. That's why you need to carefully place all outputs in the IOBs to get a usable output timing for source-synchronous designs, where the FPGA drives both clock and data.

-- Gabor

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报