插入ILA时的时序故障可以是两种类型1. ILA本身的故障路径2. dbg_hub中的故障路径

在第一种情况下,确保探头宽度小于200

在第二节,上面提到的约束将会出现。

让我们举两个例子1.只有一个ILA @ 300Mhz

在这种情况下,dbg_hub时钟和ILA时钟将是相同的

所以你必须使用下面的约束来消除dbg_hub中的任何计时故障

set_property C_CLK_INPUT_FREQ_HZ 300000000 [get_debug_cores dbg_hub]

set_property C_ENABLE_CLK_DIVIDER true [get_debug_cores dbg_hub]

此值“300000000”应与freq(以hz为单位)相同,与连接到dbg_hub块的时钟相同

现在是第二个例子,有两个ILA的1 @ 300&

2 @ 250

在这种情况下,dbg_hub时钟也会获得上述时钟之一(300或250)

现在对dbg_hub使用相同的约束,并根据连接到dbg_hub模块的时钟正确设置hq中的freq值

上面提到的两个约束是通过使用MMCM来降低dbg_hub模块的频率

内部set_property C_ENABLE_CLK_DIVIDER true [get_debug_cores dbg_hub]

如果此属性设置为false,则不会对任何MMCM进行实例化...

希望这可以帮助。

问候

Sikta

以上来自于谷歌翻译

以下为原文

The timing failures when ILA is inserted can be of two types

1. The failure paths in ILA itself

2. The failure paths in dbg_hub

In 1st case make sure your probe width is less 200

In 2nd the constraint mentioned above will come into picture.

lets take two examples

1. Only one ILA @ 300Mhz

In this case the dbg_hub clock and ILA clock will be same

so you have to use below constraints to eliminate any timing failures in dbg_hub

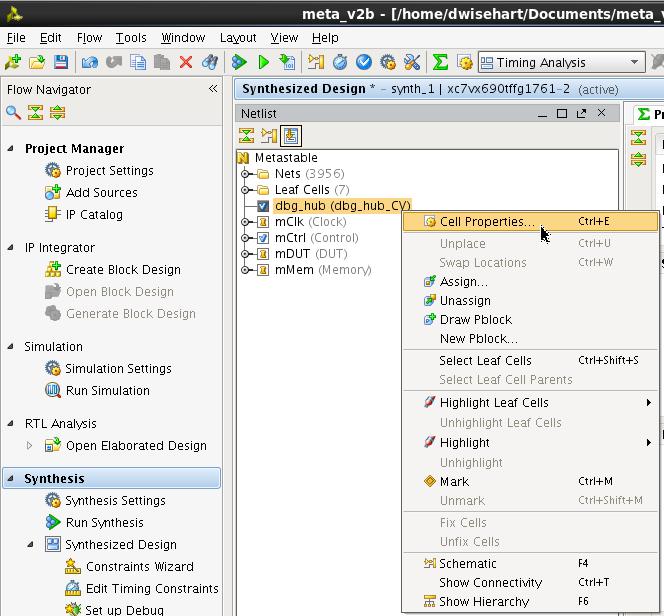

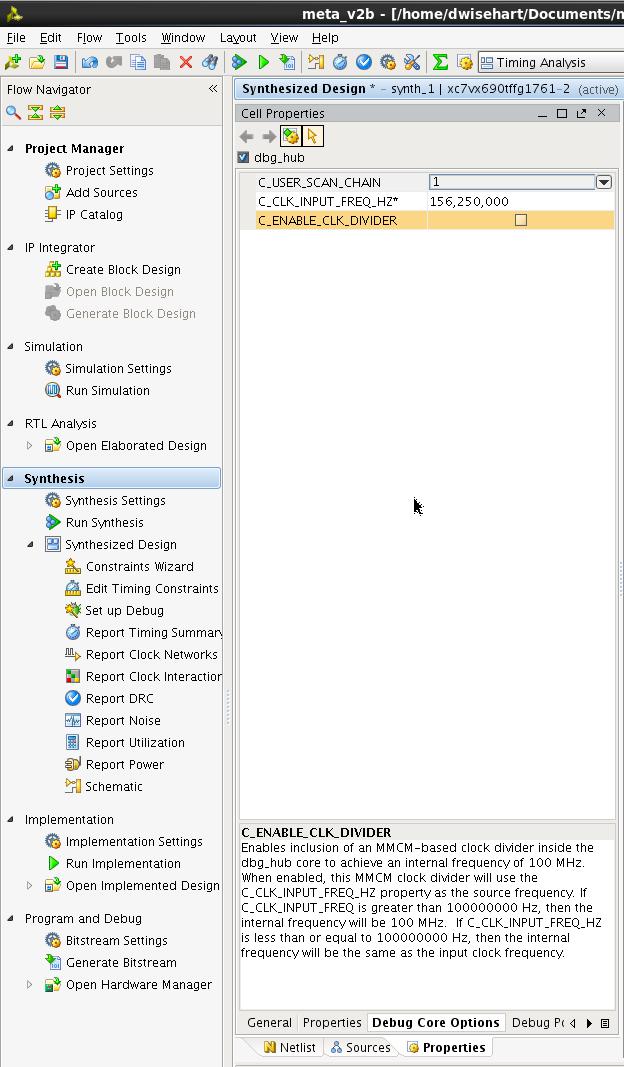

set_property C_CLK_INPUT_FREQ_HZ 300000000 [get_debug_cores dbg_hub]

set_property C_ENABLE_CLK_DIVIDER true [get_debug_cores dbg_hub]

This value "300000000" should be same as the freq (in hz) as that of clock connected to dbg_hub block

and now 2nd example

with two ILA's 1 @ 300 & 2 @ 250

In this case also dbg_hub clock gets one of above clocks (either 300 or 250)

now use same constraints above for dbg_hub and properly set the freq value in hz based on the clock connected to dbg_hub module

above mentioned two constraints are to reduce frequency for dbg_hub module by using an MMCM

internally set_property C_ENABLE_CLK_DIVIDER true [get_debug_cores dbg_hub]

if this property is set to false there wont be any MMCM instantiated...

Hope this helps.

Regards

Sikta

插入ILA时的时序故障可以是两种类型1. ILA本身的故障路径2. dbg_hub中的故障路径

在第一种情况下,确保探头宽度小于200

在第二节,上面提到的约束将会出现。

让我们举两个例子1.只有一个ILA @ 300Mhz

在这种情况下,dbg_hub时钟和ILA时钟将是相同的

所以你必须使用下面的约束来消除dbg_hub中的任何计时故障

set_property C_CLK_INPUT_FREQ_HZ 300000000 [get_debug_cores dbg_hub]

set_property C_ENABLE_CLK_DIVIDER true [get_debug_cores dbg_hub]

此值“300000000”应与freq(以hz为单位)相同,与连接到dbg_hub块的时钟相同

现在是第二个例子,有两个ILA的1 @ 300&

2 @ 250

在这种情况下,dbg_hub时钟也会获得上述时钟之一(300或250)

现在对dbg_hub使用相同的约束,并根据连接到dbg_hub模块的时钟正确设置hq中的freq值

上面提到的两个约束是通过使用MMCM来降低dbg_hub模块的频率

内部set_property C_ENABLE_CLK_DIVIDER true [get_debug_cores dbg_hub]

如果此属性设置为false,则不会对任何MMCM进行实例化...

希望这可以帮助。

问候

Sikta

以上来自于谷歌翻译

以下为原文

The timing failures when ILA is inserted can be of two types

1. The failure paths in ILA itself

2. The failure paths in dbg_hub

In 1st case make sure your probe width is less 200

In 2nd the constraint mentioned above will come into picture.

lets take two examples

1. Only one ILA @ 300Mhz

In this case the dbg_hub clock and ILA clock will be same

so you have to use below constraints to eliminate any timing failures in dbg_hub

set_property C_CLK_INPUT_FREQ_HZ 300000000 [get_debug_cores dbg_hub]

set_property C_ENABLE_CLK_DIVIDER true [get_debug_cores dbg_hub]

This value "300000000" should be same as the freq (in hz) as that of clock connected to dbg_hub block

and now 2nd example

with two ILA's 1 @ 300 & 2 @ 250

In this case also dbg_hub clock gets one of above clocks (either 300 or 250)

now use same constraints above for dbg_hub and properly set the freq value in hz based on the clock connected to dbg_hub module

above mentioned two constraints are to reduce frequency for dbg_hub module by using an MMCM

internally set_property C_ENABLE_CLK_DIVIDER true [get_debug_cores dbg_hub]

if this property is set to false there wont be any MMCM instantiated...

Hope this helps.

Regards

Sikta

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报