我遇到了我的UCF问题。

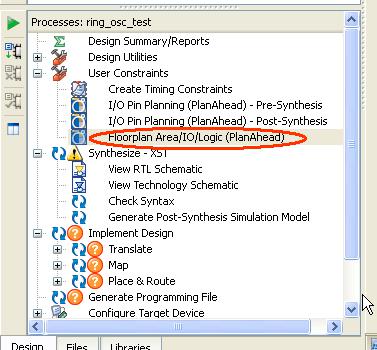

问题是ISE中的实现工具无法找到我的网络路径。

我有一个瞬时组件的层次结构(设计是在vhdl中),即顶层模块的瞬间称为u_ddr_interface然后 - > inst u_mem controller - > infrastructure_top0 - > clk_dcm0。

在最低级别的层次结构(clk_dcm0)中,有一个信号u2_clk0_out,我想在网络中连接(我需要它用于

timespec约束)。

现在我有这样的东西:NET“u_ddr_interface / u_mem_controller / infrastructure_top0 / clk_dcm0 / u2_clk0_out”TNM_NET =“U2_CLK0_OUT”;

在我的UCF中。

ConstraintSystem工具没有看到u2_clk0_out信号的路径,我得到以下错误:错误:ConstraintSystem:59 - 约束[vga.ucf(33)]:NET

“u_ddr_interface / u_mem_controller / infrastructure_top0 / clk_dcm0 / u2_clk0_out”

未找到。

请验证:

1.指定的设计元素实际存在于原始设计中。

2.指定的对象在约束源文件中拼写正确。

知道该怎么做以及我做错了什么?

该设计适用于Spartan-3E,我使用CoreGen生成的ddr控制器。

谢谢和问候,Piotr

以上来自于谷歌翻译

以下为原文

I am encountering a problem with my UCF. The issue is that the implementation tool in ISE can't find my net path. I've got a hierarchy of instantations od components (the design is in vhdl), i.e. top module has the instantation called u_ddr_interface then -> inst u_mem controller ->infrastructure_top0 -> clk_dcm0. In the lowest level of hierarchy (clk_dcm0) there is a signal u2_clk0_out that I want to connect in a net (I need it for timespec constraint). Now I've got something like this: NET "u_ddr_interface/u_mem_controller/infrastructure_top0/clk_dcm0/u2_clk0_out" TNM_NET = "U2_CLK0_OUT"; in my UCF. ConstraintSystem tool doesn't see the path to u2_clk0_out signal and I get the following error: ERROR:ConstraintSystem:59 - Constraint

"u_ddr_interface/u_mem_controller/infrastructure_top0/clk_dcm0/u2_clk0_out"

TNM_NET = "U2_CLK0_OUT";> [vga.ucf(33)]: NET

"u_ddr_interface/u_mem_controller/infrastructure_top0/clk_dcm0/u2_clk0_out"

not found. Please verify that:

1. The specified design element actually exists in the original design.

2. The specified object is spelled correctly in the constraint source file. Any idea what to do with that and what I am doing wrong? The design is for Spartan-3E and I use the ddr controller generated by CoreGen. Thanks and regards, Piotr

举报

举报

举报

举报

举报

举报

举报

举报