JTAG(Joint Test Action Group,联合测试行动小组)接口是一种 国际标准的电子电路测试协议 ,最初是为了便于芯片级的测试和调试而开发的。JTAG技术主要应用于嵌入式系统中,尤其是对于那些具有复杂可编程逻辑器件(如FPGA、CPLD)和微控制器的电路板。

JTAG接口通常由 四个必要信号线组成 :TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。JTAG接口广泛应用于硬件调试、固件升级、电路测试等领域,是现代电子设计和制造中不可或缺的一部分。

一、JTAG接口的介绍

JTAG是一种用于 测试芯片和Debug的接口技术 ,它可以让开发者通过JTAG接口访问CPU内部寄存器和挂在CPU总线上的设备,如FLASH、RAM、SOC等内置模块的寄存器,如UART、Timers、GPIO等等的寄存器。含有JTAG Debug接口模块的CPU只要 时钟正常 ,就可以通过JTAG接口访问这些寄存器。

要使用JTAG接口下载程序到RAM,需要先设置RAM的基地址、总线宽度、访问速度等等。有些SOC可能还需要Remap才能正常工作。如果使用JTAG接口,相关的寄存器可能还处在上电值或错误值,RAM不能正常工作,所以下载必然要失败。因此,在使用JTAG接口之前,需要 先设置RAM (在ADW中,可以在Console窗口通过Let命令设置;在AXD中可以在Console窗口通过Set命令设置)。

二、JTAG接口引脚定义

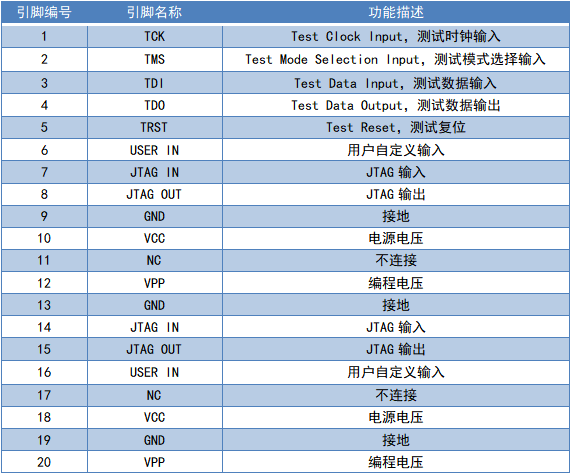

JTAG接口有许多不同种类,包括4针脚、6针脚、10针脚、14针脚、20针脚等。这里以JTAG接口的20针脚为例,参考下图引脚定义表格。

以上是 20针JTAG接口的引脚定义 ,其中包含了TCK、TMS、TDI、TDO、TRST等测试相关的信号,以及JTAG输入输出、用户自定义输入、电源和编程电压等。

三、JTAG接口PCB设计

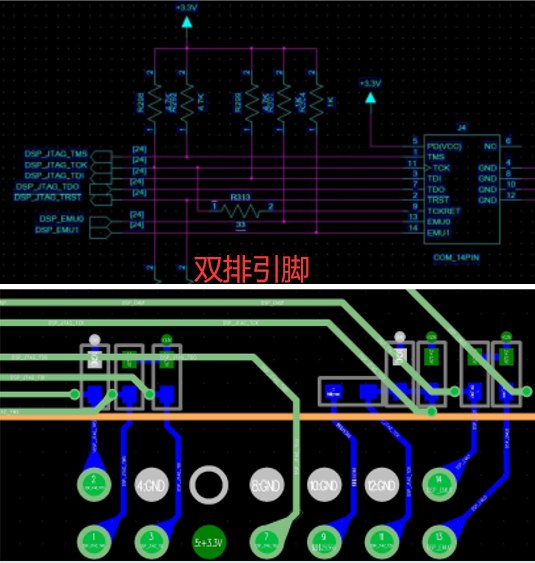

1、 确定JTAG接口的 规格要求 ,例如JTAG信号的数量、电平范围等。根据规格要求,选择合适的JTAG连接器和PCB封装。

2、 在PCB上预留JTAG连接器的位置,并确保连接器的接脚与PCB布线边缘 预留足够的距离 ,以避免信号完整性问题和EMC辐射问题。

3、 为了方便烧录程序,布局时通常摆放在板边, 并尽量靠近CPU。一般是 1脚朝外布局 。

4、 放置TEST、JATA接口的上下拉或串接电阻 靠近接口 。

5、 布线注意走在同一层,时钟线与其他信号线保持 4w以上间距 。

6、 根据JTAG连接器的规格书和PCB布线规则,设计JTAG连接器的焊盘布局和信号线宽、线距等。

7、 考虑JTAG连接器与周边组件和电源的交互,设计相应的 电源和地平面 ,以提供稳定的电源电压和良好的信号完整性。

四、PCB可制造性设计

JTAG是一种串行接口标准,用于 测试和调试嵌入式系统中的集成电路 。在进行PCB设计时,需要考虑JTAG接口的制造性设计方面。

1、走线宽度

JTAG接口的信号线宽度应该根据信号的电流和负载要求进行设计,此时需考虑生产的 蚀刻公差 ,避免线宽被蚀刻线幼。

2、走线间距

JTAG接口的信号线 间距应该足够大 ,以保证信号的质量和稳定性。此时需考虑生产的制成能力,避免因间距小导致信号质量差或短路。

3、焊盘设计

JTAG接口的 焊盘应该足够大 ,以便于焊接和连接,同时应该避免与其他信号焊盘冲突。

4、元件布局

JTAG接口的元件应该尽量 靠近板边 ,方便测试与程序烧录。同时应该 避免元件布局过于密集 ,造成组装焊接不方便。

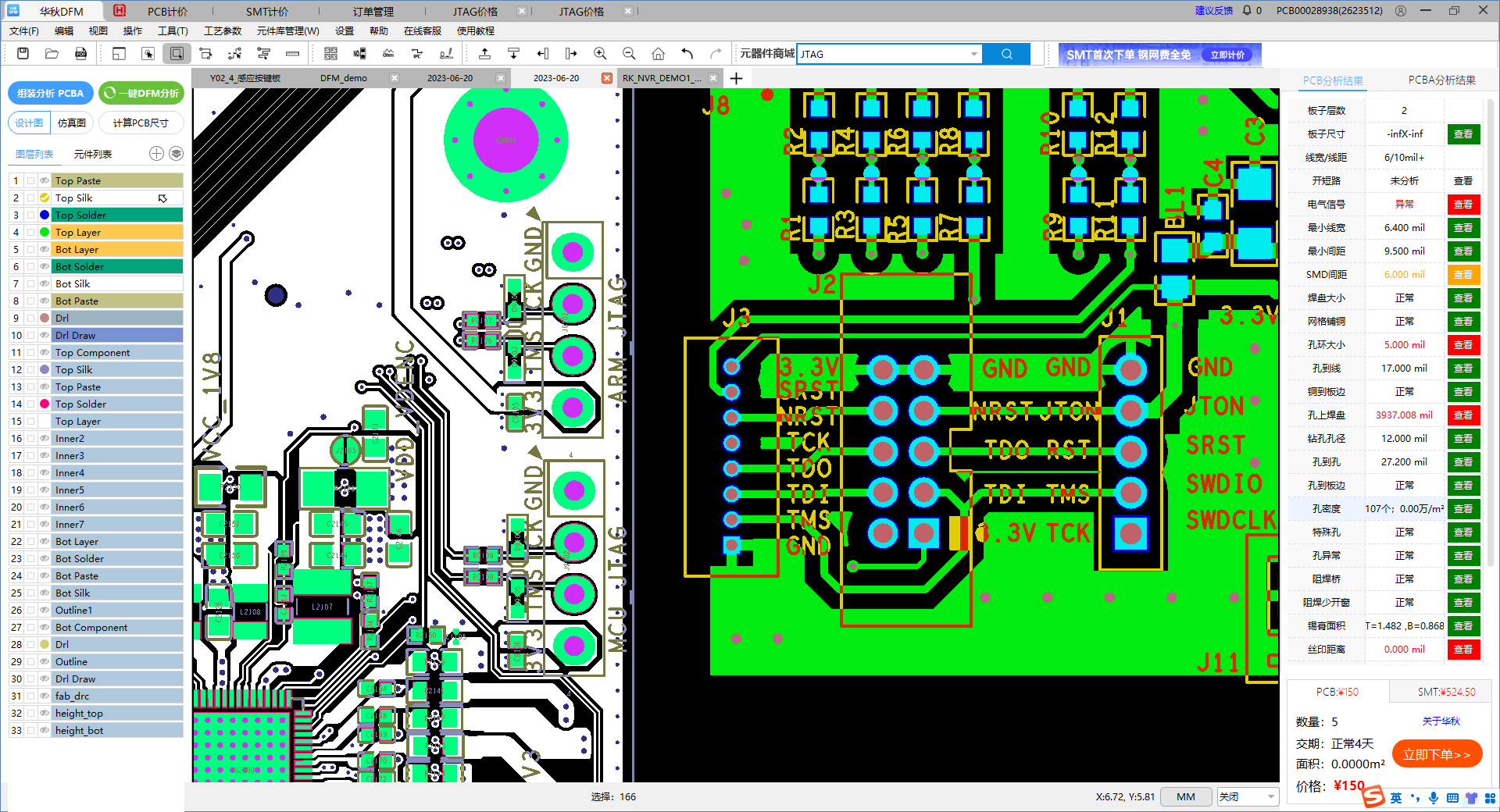

这里推荐一款可制造性检查的工艺软件: 华秋DFM ,对于JTAG接口的PCB可制造性,可以 检查走线是否合理、焊盘的大小是否合适 ,还可以 检查JTAG接口可组装性问题 ;并且还能 提前预防JTAG接口的PCB是否存在可制造性的问题 。

华秋DFM软件是国内首款免费PCB可制造性和装配分析软件,拥有 600万+元件库 ,可轻松高效完成装配分析。其PCB裸板的分析功能,开发了 29大项,100+细项检查规则 ,PCBA组装的分析功能,开发了 14大项,800+细项检查规则 。

基本可涵盖所有可能发生的制造性问题,能帮助设计工程师在生产前检查出可制造性问题,且能够 满足工程师需要的多种场景 ,将产品研制的迭代次数降到最低,减少成本。

● 华秋DFM软件下载地址(复制到电脑浏览器打开):

https://dfm.elecfans.com/dl/software/hqdfm.zip?from=zdwz

华秋DFM软件新客福利

首次下单不限金额,立返1000元优惠券;

首次下单金额超500元,立返2000元优惠券。

●关注【华秋DFM】获取最新可制造性干货合集

/9

/9