FPGA点亮LED 1

下面以点LED灯为例进行进行fpga使用的介绍。

首先修改VE文件如下

SYSCLK 200

BUSCLK 100

HSECLK 8

LED1 PIN_34:OUTPUT # LED1

这里我们将PIN_34接到了LED1信号线上。

之后在VS code中点击Prepare LOGIC,生成LOGIC工程,并对其中的user_ip.v文件进行如下修改

module user_ip (

output tri0 LED1,

input sys_clock,

input bus_clock,

input resetn,

input stop,

input [1:0] mem_ahb_htrans,

input mem_ahb_hready,

input mem_ahb_hwrite,

input [31:0] mem_ahb_haddr,

input [2:0] mem_ahb_hsize,

input [2:0] mem_ahb_hburst,

input [31:0] mem_ahb_hwdata,

output tri1 mem_ahb_hreadyout,

output tri0 mem_ahb_hresp,

output tri0 [31:0] mem_ahb_hrdata,

output tri0 slave_ahb_hsel,

output tri1 slave_ahb_hready,

input slave_ahb_hreadyout,

output tri0 [1:0] slave_ahb_htrans,

output tri0 [2:0] slave_ahb_hsize,

output tri0 [2:0] slave_ahb_hburst,

output tri0 slave_ahb_hwrite,

output tri0 [31:0] slave_ahb_haddr,

output tri0 [31:0] slave_ahb_hwdata,

input slave_ahb_hresp,

input [31:0] slave_ahb_hrdata,

output tri0 [3:0] ext_dma_DMACBREQ,

output tri0 [3:0] ext_dma_DMACLBREQ,

output tri0 [3:0] ext_dma_DMACSREQ,

output tri0 [3:0] ext_dma_DMACLSREQ,

input [3:0] ext_dma_DMACCLR,

input [3:0] ext_dma_DMACTC,

output tri0 [3:0] local_int

);

assign mem_ahb_hreadyout = 1'b1;

assign slave_ahb_hready = 1'b1;

reg LED;

reg [24:0] clkcount;

assign LED1 = LED;

always @ (posedge sys_clock)

begin

clkcount <= clkcount+1;

case(clkcount[24])

0: LED <= 0;

1: LED <= 1;

endcase

end

endmodule

编译结束后可以看到逻辑资源使用非常少,没有超过2K的限制。

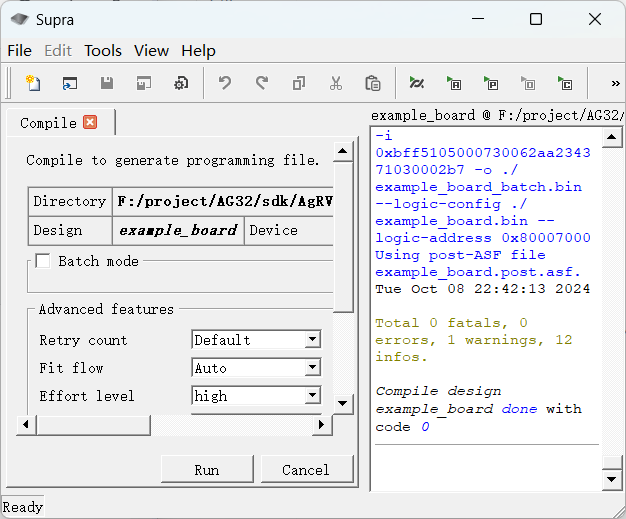

之后进行Supra编译,编译完成后如下图。

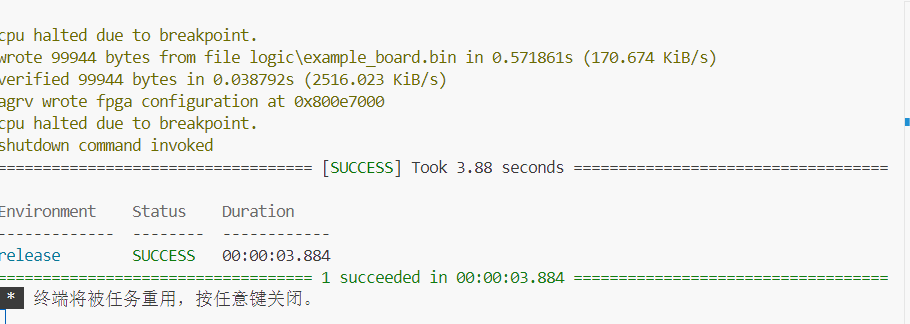

最后执行Upload LOGIC烧录,烧录完成后,就能够看到LED在疯狂闪烁啦。