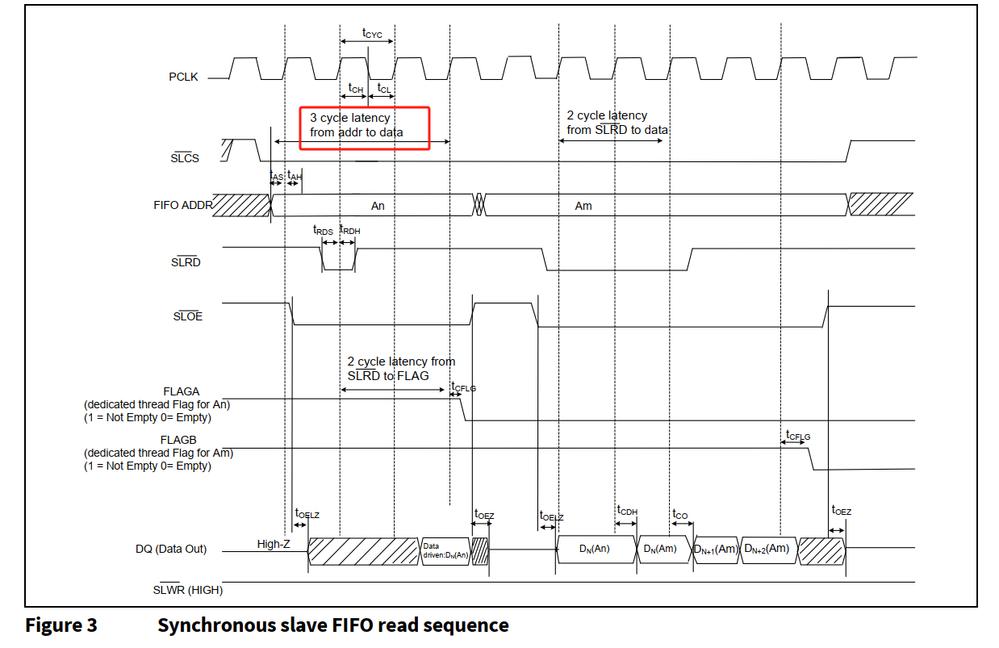

您好!关于FX3作为同步Slave FIFO的同步读时序,我理解您的疑问。在同步Slave FIFO中,确实需要一定的时延来确保数据的稳定性和可靠性。红框中提到的3个周期的时延是为了确保在SLRD拉低之前,片选和地址已经稳定。

虽然您提到了可以在片选拉低之前将地址放到地址总线上,但这样做可能会导致数据的不稳定。因为在片选拉低之前,地址总线上的数据可能还没有完全稳定,这可能会导致读取到错误的数据。

同步Slave FIFO的时序要求是为了确保数据的准确性和可靠性。在实际应用中,我们需要遵循这些时序要求,以避免潜在的问题。当然,具体的时序要求可能会因不同的硬件和设计而有所不同,因此在设计时需要参考相关硬件的数据手册和设计指南。

总之,虽然您的想法在某些情况下可能是可行的,但为了确保数据的稳定性和可靠性,遵循同步Slave FIFO的时序要求是非常重要的。希望这能帮助您解决疑问!

您好!关于FX3作为同步Slave FIFO的同步读时序,我理解您的疑问。在同步Slave FIFO中,确实需要一定的时延来确保数据的稳定性和可靠性。红框中提到的3个周期的时延是为了确保在SLRD拉低之前,片选和地址已经稳定。

虽然您提到了可以在片选拉低之前将地址放到地址总线上,但这样做可能会导致数据的不稳定。因为在片选拉低之前,地址总线上的数据可能还没有完全稳定,这可能会导致读取到错误的数据。

同步Slave FIFO的时序要求是为了确保数据的准确性和可靠性。在实际应用中,我们需要遵循这些时序要求,以避免潜在的问题。当然,具体的时序要求可能会因不同的硬件和设计而有所不同,因此在设计时需要参考相关硬件的数据手册和设计指南。

总之,虽然您的想法在某些情况下可能是可行的,但为了确保数据的稳定性和可靠性,遵循同步Slave FIFO的时序要求是非常重要的。希望这能帮助您解决疑问!

举报

举报

举报

举报

举报

举报