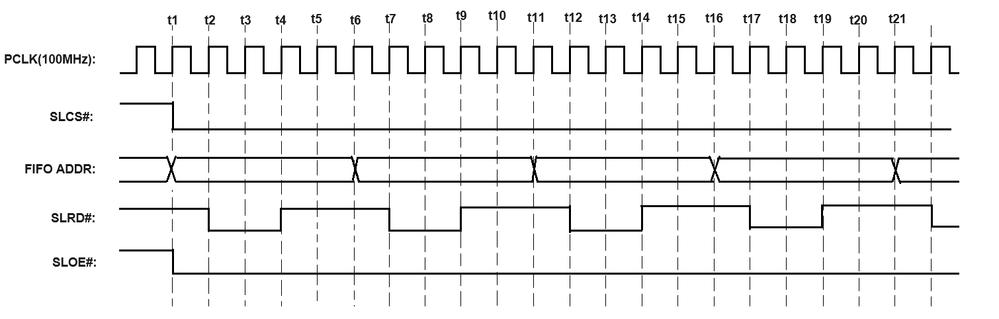

根据您提供的描述,这里是对AN65974中时序图的理解:

1. 复位时,SLCS(片选)、SLRD(读使能)和SLOE(输出使能)全部为低电平。

2. 在t1时刻,将SLCS和SLOE置为高电平,同时将地址接入地址总线。

3. 在t2时刻,将SLRD置为高电平(FX3会在下一个时钟沿,即t3时刻检查SLRD是否为低电平)。

4. 由于不是突发传输,在t4时刻将SLRD置为低电平。

5. 在t5时刻,SLRD变为低电平后已过去两个时钟周期,此时FPGA需要检查FLAG是否为高电平。如果FLAG为高电平,则对数据总线进行采样;如果FLAG为低电平,则不对数据总线进行采样。

从您的描述来看,FPGA应该能够正确接收来自FX3同步从站FIFO的数据。但是,为了确保数据传输的稳定性和可靠性,建议您仔细检查以下几点:

1. 确保FPGA和FX3之间的时钟同步。如果时钟不同步,可能会导致数据传输错误。

2. 检查FPGA和FX3之间的接口信号是否正确连接,包括地址总线、数据总线、控制信号等。

3. 确保FPGA的采样时钟与FX3的数据传输时钟相匹配,以便在正确的时刻采样数据。

4. 在FPGA端添加适当的错误检测和处理机制,以便在出现问题时能够及时发现并采取相应措施。

总之,只要确保FPGA和FX3之间的接口信号正确连接,时钟同步,以及采样时钟匹配,FPGA应该能够正确接收来自FX3同步从站FIFO的数据。

根据您提供的描述,这里是对AN65974中时序图的理解:

1. 复位时,SLCS(片选)、SLRD(读使能)和SLOE(输出使能)全部为低电平。

2. 在t1时刻,将SLCS和SLOE置为高电平,同时将地址接入地址总线。

3. 在t2时刻,将SLRD置为高电平(FX3会在下一个时钟沿,即t3时刻检查SLRD是否为低电平)。

4. 由于不是突发传输,在t4时刻将SLRD置为低电平。

5. 在t5时刻,SLRD变为低电平后已过去两个时钟周期,此时FPGA需要检查FLAG是否为高电平。如果FLAG为高电平,则对数据总线进行采样;如果FLAG为低电平,则不对数据总线进行采样。

从您的描述来看,FPGA应该能够正确接收来自FX3同步从站FIFO的数据。但是,为了确保数据传输的稳定性和可靠性,建议您仔细检查以下几点:

1. 确保FPGA和FX3之间的时钟同步。如果时钟不同步,可能会导致数据传输错误。

2. 检查FPGA和FX3之间的接口信号是否正确连接,包括地址总线、数据总线、控制信号等。

3. 确保FPGA的采样时钟与FX3的数据传输时钟相匹配,以便在正确的时刻采样数据。

4. 在FPGA端添加适当的错误检测和处理机制,以便在出现问题时能够及时发现并采取相应措施。

总之,只要确保FPGA和FX3之间的接口信号正确连接,时钟同步,以及采样时钟匹配,FPGA应该能够正确接收来自FX3同步从站FIFO的数据。

举报

举报

举报

举报