中断介绍

1)ARM cortex-A系列处理器,提供了4个管脚给soc,实现外界中断的传递。分别是:nIRQ、nFIQ、nVIRQ、nVFIQ。arm系统中,会有多个外设,均有可能产生中断发送给core,因此就需要有一个中断控制器来作为中间的桥接,收集soc的所有中断信号,然后仲裁选择合适(高优先级)的中断,再发送给CPU,等待CPU处理。

2)这里中间的桥接,就是arm公司推出的大名鼎鼎的gic(general interrupt controller)。gic其实是一个架构,版本历经了gicv1,gicv2,gicv3,gicv4。

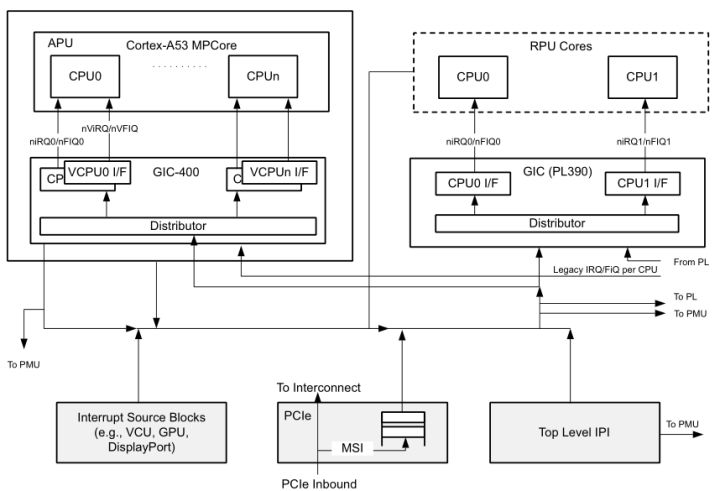

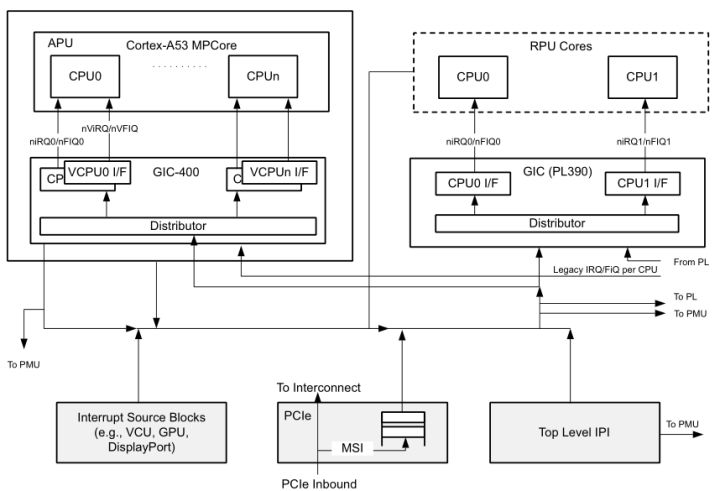

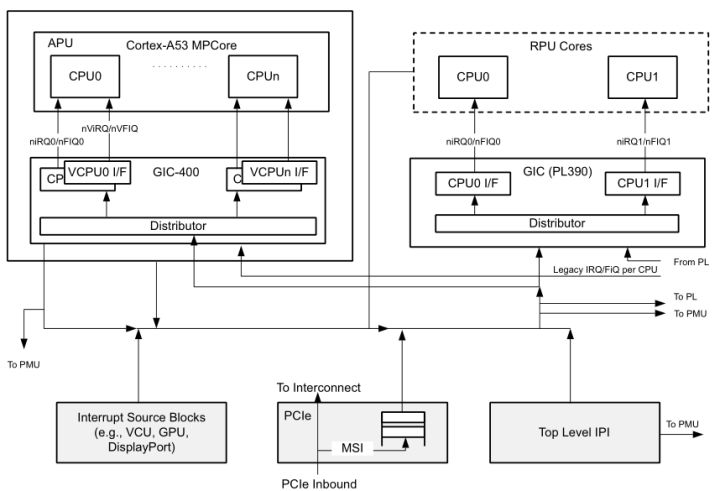

3)Ultrascale+中断框图如下

图中包含两个GIC:

RPU GIC:PL390(arm公司设计的对应GICv1 IP)

APU GIC:GIC-400(arm公司设计的对应GICv2 IP)

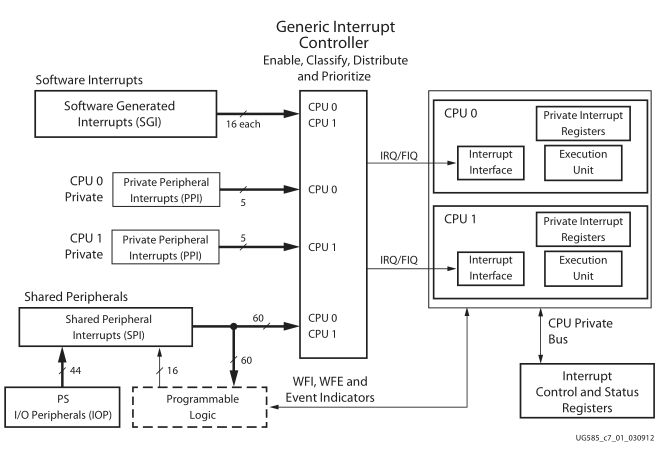

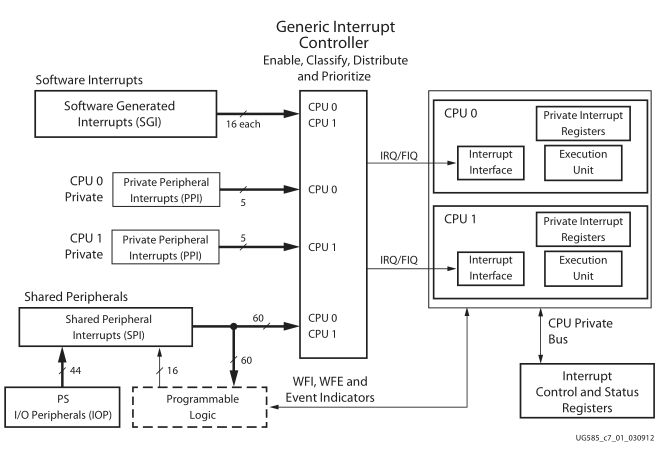

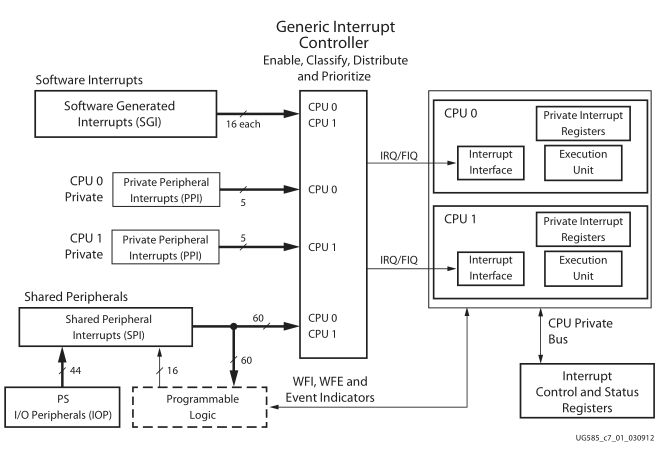

4)RPU GIC,其系统功能框图如下:

从图中可以看到,中断源主要有三种:

PPI:private peripheral interrupt,私有外设中断,该中断来源于外设,只对固定的core有效。

SPI:shared peripheral interrupt,共享外设中断,该中断来源于外设,可以对所有的core有效。

SGI:software-generated interrupt,软中断,软件产生的中断,用于给指定的core发送中断信号

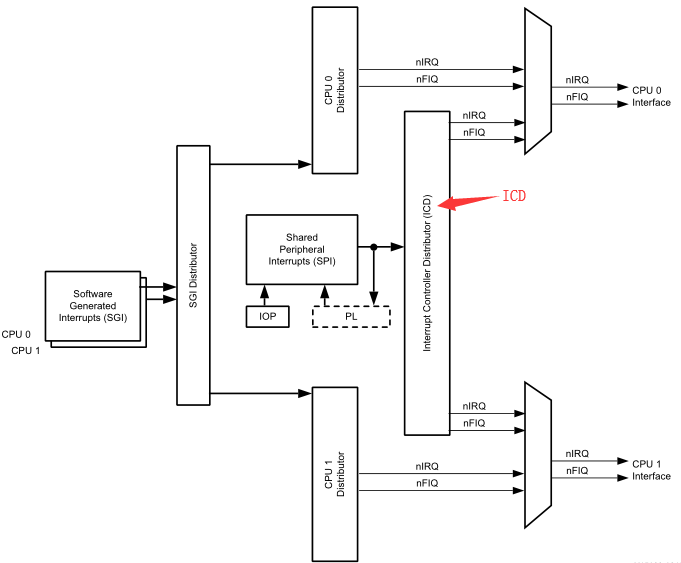

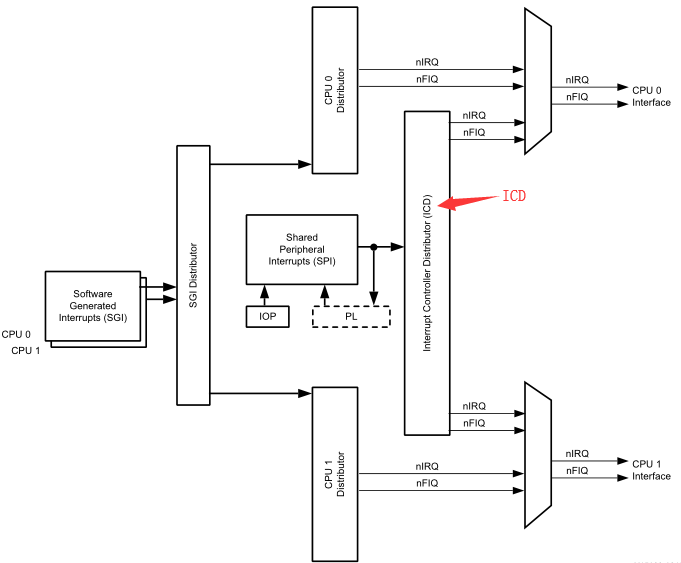

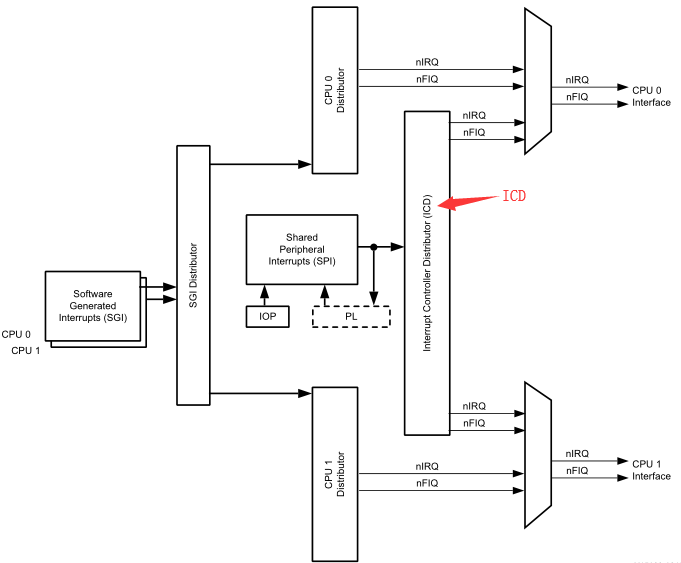

控制器功能框图如下:

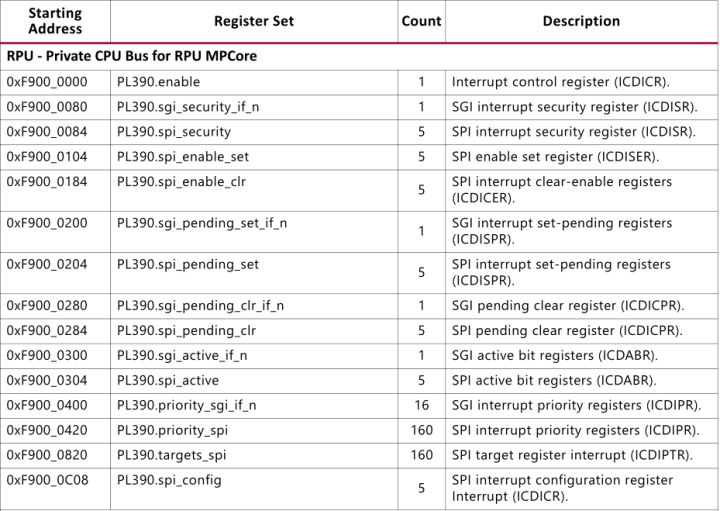

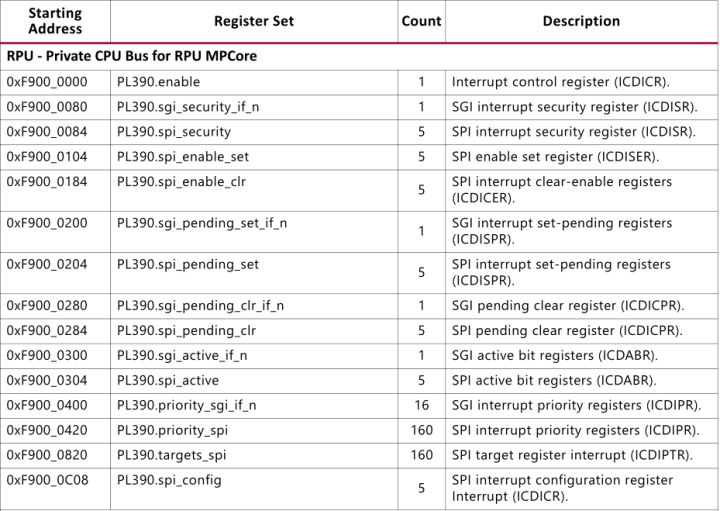

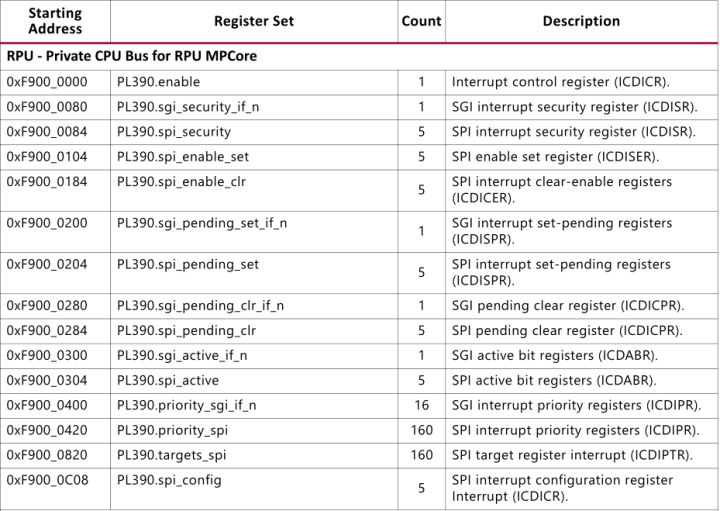

上图中, ICD的控制寄存器主要如下:

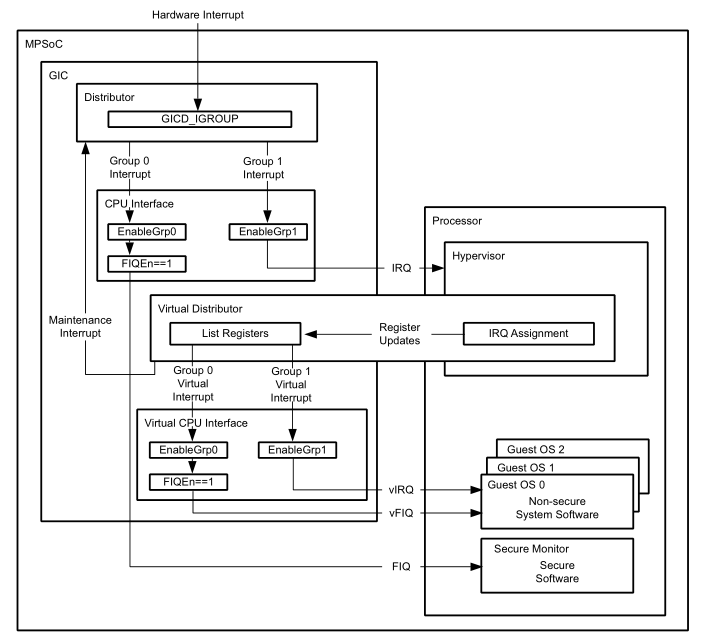

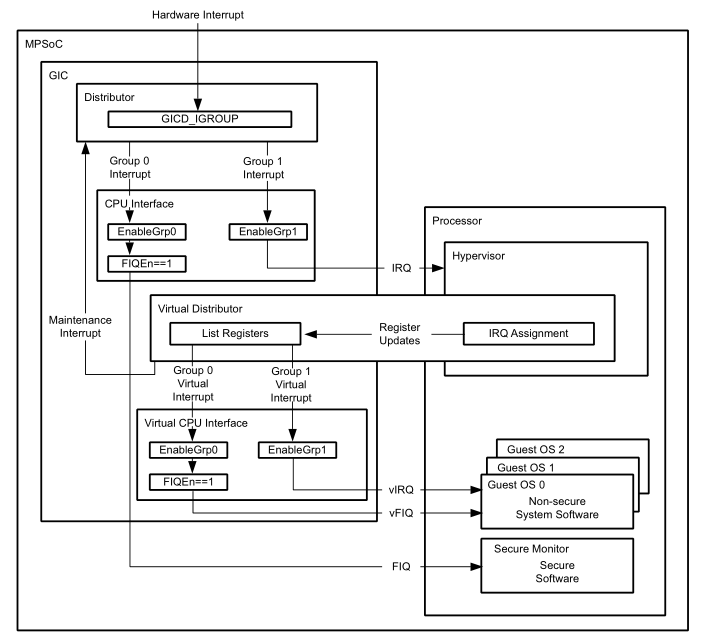

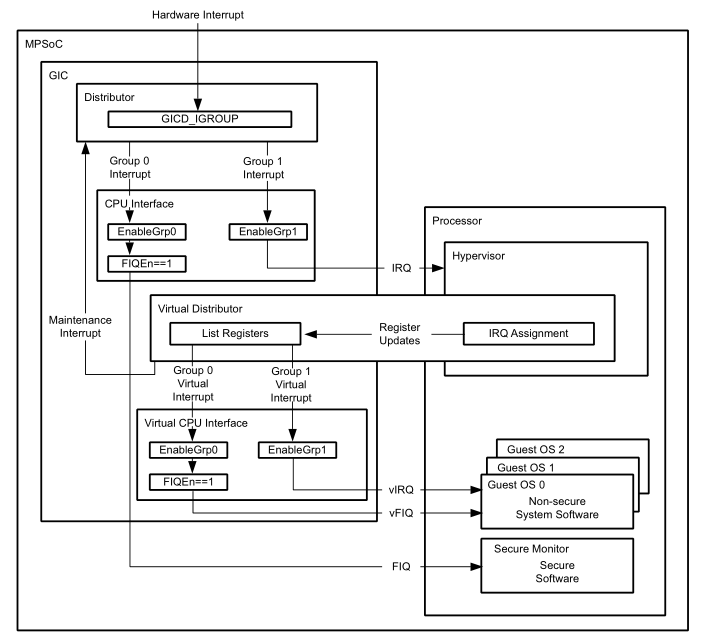

1)APU GIC,功能框图如下

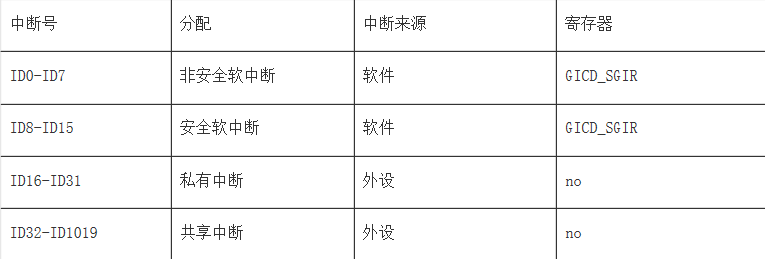

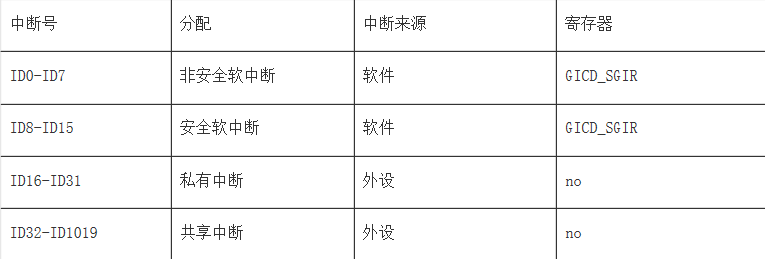

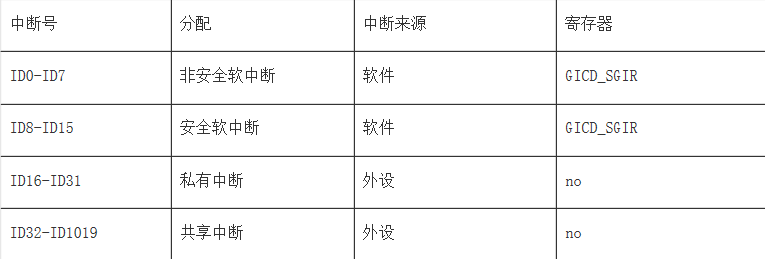

GICv2,将中断分成了group0和group1。使用寄存器GICD_IGROUPRn来对每个中断,设置组。其中group0:安全中断,由nFIQ驱动,group1:非安全中断,由nIRQ驱动。支持最大1020个中断。其中断号分配如下:

GICv2,主要由两部分组成:distributor及cpu interface。

distributor,用来收集所有的中断来源,并且为每个中断源设置中断优先级,中断分组,中断目的core。当有中断产生时,将当前最高优先级中断,发送给对应的cpu interface。其功能有:全局中断使能、每个中断的使能、中断的优先级、中断的分组、中断的目的core、中断触发方式、对于SGI中断,传输中断到指定的core、每个中断的状态管理、提供软件,可以修改中断的pending状态

cpu interface,将GICD发送的中断信息,通过IRQ,FIQ管脚,发送给连接到该cpu接口的core。其功能有:将中断请求发送给cpu、对中断进行认可(acknowledging an interrupt)、中断完成识别(indicating completion of an interrupt)、设置中断优先级屏蔽、定义中断抢占策略、决定当前处于pending状态最高优先级中断

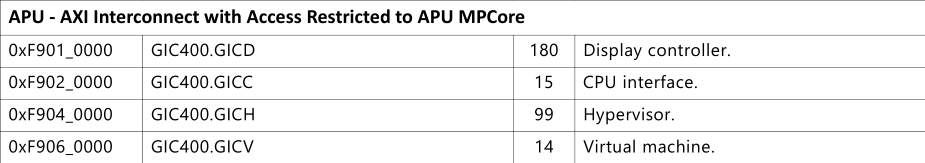

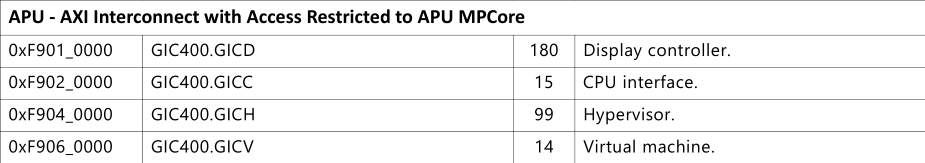

gicv2,定义了自己的一些寄存器,这些寄存器,都是使用memory-mapped的方式去访问的,也就是在soc中,会留有一片空间,给gic。cpu通过访问这部分空间,来对gic进行操作。主要寄存器如下:

这里中断只是作简单介绍,需要详细了解的,请参照xilinx提供的文档:ug1085-zynq-ultrascale-trm.pdf。

软件工程师工作内容

以下为软件工程师负责内容。

中断介绍

1)ARM cortex-A系列处理器,提供了4个管脚给soc,实现外界中断的传递。分别是:nIRQ、nFIQ、nVIRQ、nVFIQ。arm系统中,会有多个外设,均有可能产生中断发送给core,因此就需要有一个中断控制器来作为中间的桥接,收集soc的所有中断信号,然后仲裁选择合适(高优先级)的中断,再发送给CPU,等待CPU处理。

2)这里中间的桥接,就是arm公司推出的大名鼎鼎的gic(general interrupt controller)。gic其实是一个架构,版本历经了gicv1,gicv2,gicv3,gicv4。

3)Ultrascale+中断框图如下

图中包含两个GIC:

RPU GIC:PL390(arm公司设计的对应GICv1 IP)

APU GIC:GIC-400(arm公司设计的对应GICv2 IP)

4)RPU GIC,其系统功能框图如下:

从图中可以看到,中断源主要有三种:

PPI:private peripheral interrupt,私有外设中断,该中断来源于外设,只对固定的core有效。

SPI:shared peripheral interrupt,共享外设中断,该中断来源于外设,可以对所有的core有效。

SGI:software-generated interrupt,软中断,软件产生的中断,用于给指定的core发送中断信号

控制器功能框图如下:

上图中, ICD的控制寄存器主要如下:

1)APU GIC,功能框图如下

GICv2,将中断分成了group0和group1。使用寄存器GICD_IGROUPRn来对每个中断,设置组。其中group0:安全中断,由nFIQ驱动,group1:非安全中断,由nIRQ驱动。支持最大1020个中断。其中断号分配如下:

GICv2,主要由两部分组成:distributor及cpu interface。

distributor,用来收集所有的中断来源,并且为每个中断源设置中断优先级,中断分组,中断目的core。当有中断产生时,将当前最高优先级中断,发送给对应的cpu interface。其功能有:全局中断使能、每个中断的使能、中断的优先级、中断的分组、中断的目的core、中断触发方式、对于SGI中断,传输中断到指定的core、每个中断的状态管理、提供软件,可以修改中断的pending状态

cpu interface,将GICD发送的中断信息,通过IRQ,FIQ管脚,发送给连接到该cpu接口的core。其功能有:将中断请求发送给cpu、对中断进行认可(acknowledging an interrupt)、中断完成识别(indicating completion of an interrupt)、设置中断优先级屏蔽、定义中断抢占策略、决定当前处于pending状态最高优先级中断

gicv2,定义了自己的一些寄存器,这些寄存器,都是使用memory-mapped的方式去访问的,也就是在soc中,会留有一片空间,给gic。cpu通过访问这部分空间,来对gic进行操作。主要寄存器如下:

这里中断只是作简单介绍,需要详细了解的,请参照xilinx提供的文档:ug1085-zynq-ultrascale-trm.pdf。

软件工程师工作内容

以下为软件工程师负责内容。

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报