目前的 analog 样例中,支持 3 个 ADC(每个 16 路)和 2 个 DAC,1 个比较器 CMP(2 路)。

该 analog 在 cpld 中编译后,总大小大概 1.4K 个逻辑单元。

如果用户需要更多的 cpld 空间,并且只用了 adc 通道,可以对 analog 进行剪裁。

实测下来,如果只用 1 个 ADC,且只用 6 路,剪裁后大概只占 500 个逻辑单元。

(详细的测试数据,请参考文末附录)

举例:剪裁为只有 1 个 ADC,只有 6 路。

剪裁方法:

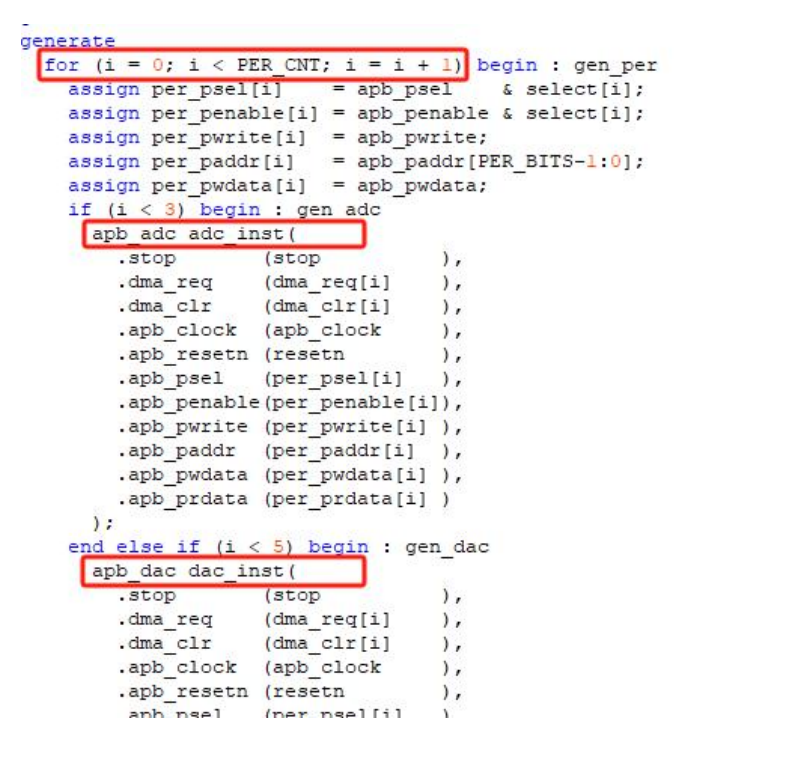

- 在 analog_ip.v 修改 adc 个数:

修改 parameter PER_CNT = 6 为:parameter PER_CNT = 1

从代码中可以看出,PER_CNT 原先为 6,就是 3 个 adc + 2 个 dac + 1 个 cmp。

如果只需要 1 路 ADC,则该值改为 1 即可。

改为 1 后,后续的 for 循环实例化 adc/dac/cmp 时,将只实例化一个 ADC。

【实例化循环:for (i = 0; i < PER_CNT; i = i + 1)】

修改后,再次编译时,会出错。对出错点进行修改:

把 assign ext_dma_DMACBREQ = dma_req[3:0] | (dma_req[4] << 2) 修改为:

assign ext_dma_DMACBREQ = dma_req[0]

原因是,修改后只有 1 路,而不再是 5 路。

此时,直接点【编译】按钮编译时,由于缓存没有清除,仍然会有报错。

这时可以重跑一次【tool】->【Tcl Scripts...】->弹出框中选 af_quartus.tcl 再点下边【Run】。

跑完后编译成功。可以看到逻辑单元变成 588 个。

- 在 **analog_ip.v **修改 adc 的 channal 数:

修改 parameter SEQ_MAX = 16 为 parameter SEQ_MAX = 6

在代码中,SEQ_MAX 表示 ADC 的最大通路数。

修改完后,重新编译。成功后看到逻辑单元变成 501 个。

注意,这样裁剪后,在 mcu 中就只能使用 1 个 ADC

裁剪出 DAC 或 CMP:

方式同上。

需要修改的点,就是 for 循环实例化时,按自己的需求产生出来 ADC/DAC/CMP 即可。

(裁剪后,不需要的代码可以注掉,减少编程时的干扰)

附录:

ADC/DAC/CMP 各种情况下使用的逻辑单元数:

空模板工程:219 //注:空模板工程为支撑 mcu 运行的最简 cpld 工程

开 ADC0 1 路:438 //指在空模板工程上只开一个 ADC 的 1 路

开 ADC0 6 路:515

开 ADC0 11 路:544

开 ADC0 16 路:584

开 ADC0+ADC1 各 16 路:890

开 ADC0+ADC1+ADC2 各 16 路:1184

开 ADC0+ADC1+ADC2+1 个 DAC: 1306

开 ADC0+ADC1+ADC2+2 个 DAC: 1322

开 ADC0+ADC1+ADC2+2 个 DAC+1 个 CMP: 1362

开 ADC0+ADC1+ADC2+2 个 DAC+1 个 CMP(开 DMA):1404

开 ADC0(16 路)+1 个 CMP:617

开 ADC0(7 路)+1 个 CMP:528

开 ADC0(7 路)+1 个 CMP(开 DMA):536

由以上结果大致可推出:

- 空模板工程需要 219 个 LE;

- ADC 占用资源不是线性增加的(开第一路是占用的比较多,约 220 个 LE,后边新增一路

占用不多,约 8 个 LE);

- DAC 占用资源也不是线性增加的(开第一个占用 122 个 LE,开第二个占用 16 个 LE)

- CMP 占用逻辑单元大概 40 个;

组合不同,可能会有一些出入,但数量级应该就是这个数量级。

/9

/9