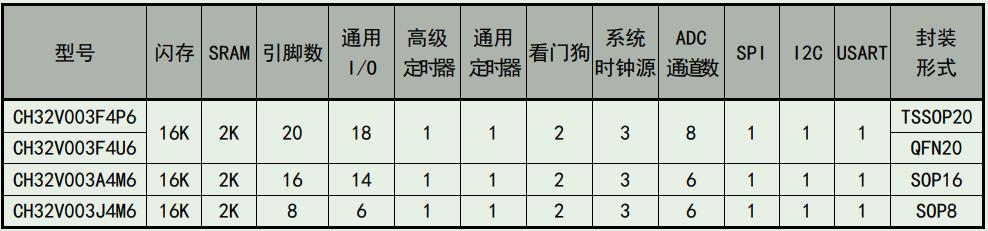

概述

CH32V003 系列是基于青稞 RISC-V2A 内核设计的工业级通用微控制器,在产品功能上支持 48MHz 系统主频。该系列具有宽压、单线调试、低功耗、超小封装等特点。提供常用的外设功能,内置 1 组 DMA控制器、1 组 10 位模数转换 ADC、1 组运放比较器、多组定时器、标准通讯接口如 USART、I2C、SPI 等。产品额定工作电压为 3.3V 或 5V,工作温度范围为-40℃~85℃工业级。

产品特性

-

内核 Core

- 青稞 32 位 RISC-V 内核,RV32EC 指令集

- 快速可编程中断控制器+硬件中断堆栈

- 支持 2 级中断嵌套

- 支持系统主频 48MHz

-

存储器

- 2KB 易失数据存储区 SRAM

- 16KB 程序存储区 CodeFlash

- 1920B 系统引导程序存储区 BootLoader

- 64B 系统非易失配置信息存储区

- 64B 用户自定义信息存储区

-

电源管理和低功耗

- 系统供电 VDD额定:3.3V 或 5V

- 低功耗模式:睡眠、待机

-

系统时钟、复位

- 内嵌出厂调校的 24MHz 的 RC 振荡器

- 内嵌 128KHz 的 RC 振荡器

- 外部支持 4~25MHz 高速振荡器

- 上/下电复位、可编程电压监测器

-

1 组 1 路通用 DMA 控制器

- 7 个通道,支持环形缓冲区管理

- 支持 TIMx/ADC/USART/I2C/SPI

-

1 组运放、比较器:连接 ADC 和 TIM2

-

1 组 10 位模数转换 ADC

- 模拟输入范围:0~VDD

- 8 路外部信号+2 路内部信号通道

- 支持外部延迟触发

-

多组定时器

- 1 个 16 位高级定时器,增加死区控制和紧急刹车,提供用于电机控制的 PWM 互补输出

-1 个 16 位通用定时器,提供输入捕获/输出比较/PWM/脉冲计数及增量编码器输入

- 2 个看门狗定时器(独立和窗口型)

- 系统时基定时器:32 位计数器

-

标准通讯接口

- 1 个 USART 接口

- 1 个 I2C 接口

- 1 个 SPI 接口

-

GPIO 端口

- 3 组 GPIO 端口,18 个 I/O 口

- 映像 1 个外部中断

-

安全特性:64 位芯片唯一 ID

-

调试模式:串行单线调试接口

-

封装形式:SOP、TSSOP、QFN

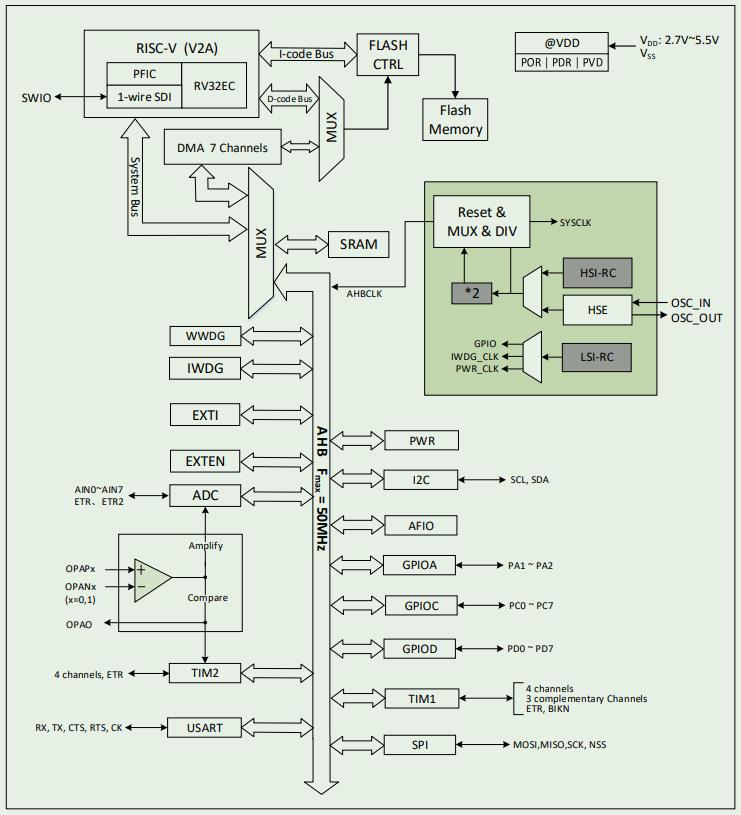

系统架构

微控制器基于 RISC-V 指令集的青稞 V2A 设计,其架构中将内核、仲裁单元、DMA 模块、SRAM 存储等部分通过多组总线实现交互。设计中集成通用 DMA 控制器以减轻 CPU 负担、提高访问效率,同时兼有数据保护机制,时钟自动切换保护等措施增加了系统稳定性。下图是系列产品内部总体架构框图。

系统框图

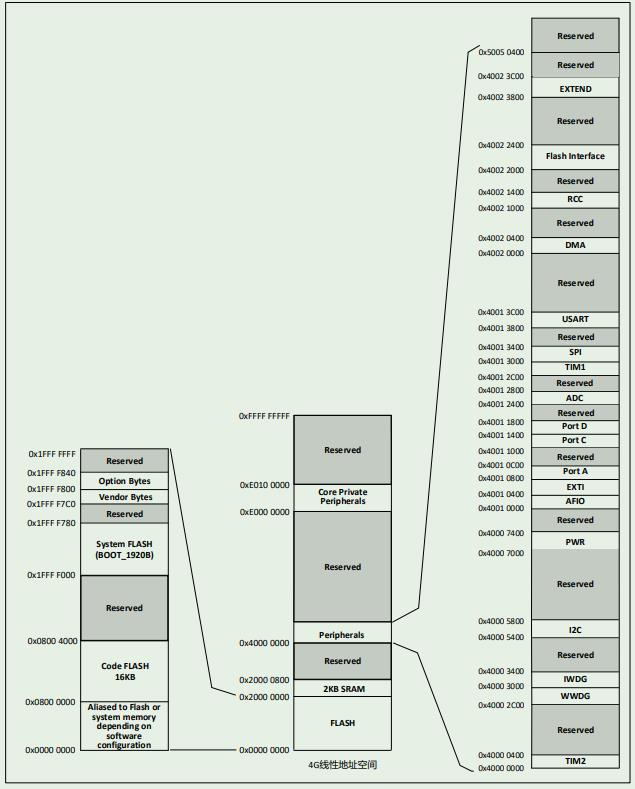

存储器地址映射

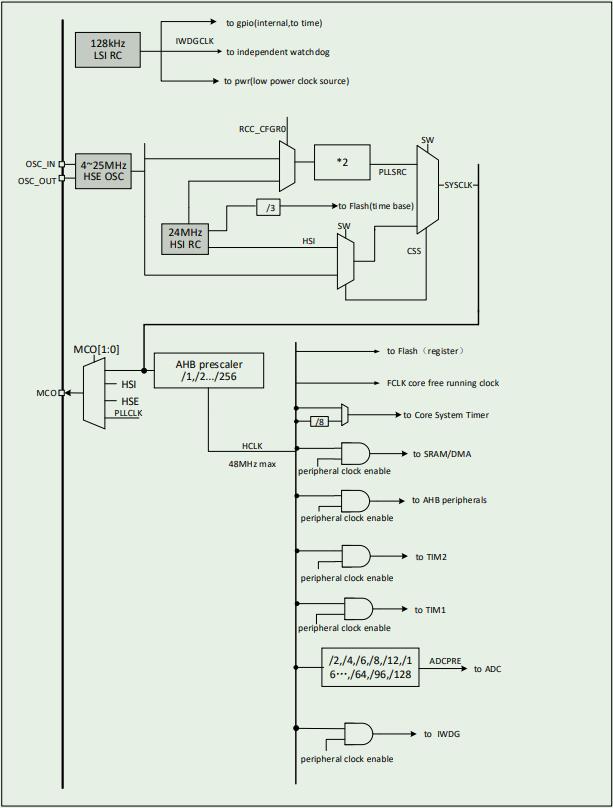

时钟树

系统中引入 3 组时钟源:内部高频 RC 振荡器(HSI)、内部低频 RC 振荡器(LSI)、外接高频振荡器(HSE)。其中,低频时钟源为独立看门狗提供了时钟基准。高频时钟源直接或者间接通过 2 倍频后输出为系统总线时钟(SYSCLK),系统时钟再由各预分频器提供了 AHB 域外设控制时钟及采样或接口输出时钟,部分模块工作需要由 PLL 时钟直接提供。

时钟树框图

功能概述

RISC-V2A 处理器

RISC-V2A 支持 RISC-V 指令集 EC 子集。处理器内部以模块化管理,包含快速可编程中断控制器(PFIC)、扩展指令支持等单元。总线与外部单元模块相连,实现外部功能模块和内核的交互。RV32EC指令集,小端数据模式。

处理器以其极简指令集、多种工作模式、模块化定制扩展等特点可以灵活应用不同场景微控制器设计,例如小面积低功耗嵌入式场景。

- 支持机器模式

- 快速可编程中断控制器(PFIC)

- 2 级硬件中断堆栈

- 串行单线调试接口

- 自定义扩展指令

片上存储器

内置 2K 字节 SRAM 区,用于存放数据,掉电后数据丢失。

内置 16K 字节程序闪存存储区(Code FLASH),用于用户的应用程序和常量数据存储。

内置 1920 字节系统存储区(System FLASH),用于系统引导程序存储(厂家固化自举加载程序)。

64 字节用于系统非易失配置信息存储区,64 字节用于用户选择字存储区。

支持 Boot 和用户代码互相跳转。

供电方案

VDD = 2.7~5.5V:为 I/O 引脚和内部调压器供电(使用 ADC 时,VDD如小于 2.9V 则性能逐渐变差)。

供电监控器

本产品内部集成了上电复位(POR)/掉电复位(PDR)电路,该电路始终处于工作状态,保证系统在供电超过 2.7V 时工作;当 VDD低于设定的阀值(VPOR/PDR)时,置器件于复位状态,而不必使用外部复位电路。

另外系统设有一个可编程的电压监测器(PVD),需要通过软件开启,用于比较 VDD供电与设定的阀值 VPVD的电压大小。打开 PVD 相应边沿中断,可在 VDD下降到 PVD 阈值或上升到 PVD 阈值时,收到中断通知。

电压调节器

复位后,调节器自动开启,根据应用方式有两个操作模式

- 开启模式:正常的运行操作,提供稳定的内核电源

- 低功耗模式:CPU 停止,系统自动进入待机模式

低功耗模式

系统支持两种低功耗模式,可以针对低功耗、短启动时间和多种唤醒事件等条件下选择达到最佳的平衡。

在睡眠模式下,只有 CPU 时钟停止,但所有外设时钟供电正常,外设处于工作状态。此模式是最浅低功耗模式,但可以达到最快唤醒。

退出条件:任意中断或唤醒事件。

置位 PDDS、SLEEPDEEP 位,执行 WFI/WFE 指令进入。内核部分的供电被关闭,HSI 的 RC 振荡器和HSE 晶体振荡器也被关闭,此模式下可以达到最低的电能消耗。

退出条件:任意外部中断/事件(EXTI 信号)、NRST 上的外部复位信号、IWDG 复位,其中 EXTI 信号包括 18 个外部 I/O 口之一、PVD 的输出、AWU 自动唤醒。

快速可编程中断控制器(PFIC)

产品内置快速可编程中断控制器(PFIC),最多支持 255 个中断向量,以最小的中断延迟提供了灵活的中断管理功能。当前产品管理了 4 个内核私有中断和 23 个外设中断管理,其他中断源保留。PFIC的寄存器均可以在机器特权模式下访问。

- 23+3 个可单独屏蔽中断

- 提供一个不可屏蔽中断 NMI

- 支持硬件中断堆栈(HPE),无需指令开销

- 提供 2 路免表中断(VTF)

- 支持地址或指令模式的向量表模式

- 支持 2 级中断嵌套

- 支持中断尾部链接功能

外部中断/事件控制器(EXTI)

外部中断/事件控制器总共包含 8 个边沿检测器,用于产生中断/事件请求。每个中断线都可以独立地配置其触发事件(上升沿或下降沿或双边沿),并能够单独地被屏蔽;挂起寄存器维持所有中断请求状态。EXTI 可以检测到脉冲宽度小于内部 AHB 的时钟周期。18 个通用 I/O 口都可选择连接到同一个个外部中断源。

通用 DMA 控制器

系统内置了 1 组通用 DMA 控制器,管理 7 个通道,灵活处理存储器到存储器、外设到存储器和存储器到外设间的高速数据传输,支持环形缓冲区方式。每个通道都有专门的硬件 DMA 请求逻辑,支持一个或多个外设对存储器的访问请求,可配置访问优先权、传输长度、传输的源地址和目标地址等。

DMA 用于主要的外设包括:通用/高级定时器 TIMx、ADC、USART、I2C、SPI。

注:DMA 和 CPU 经过仲裁器仲裁之后对系统 SRAM 进行访问。

时钟和启动

系统时钟源 HSI 默认开启,在没有配置时钟或者复位后,内部 24MH 的 RC 振荡器作为默认的 CPU时钟,随后可以另外选择外部 4~25MHz 时钟或 PLL 时钟。当打开时钟安全模式后,如果 HSE 用作系统时钟(直接或间接),此时检测到外部时钟失效,系统时钟将自动切换到内部 RC 振荡器,同时 HSE 和PLL 自动关闭;对于关闭时钟的低功耗模式,唤醒后系统也将自动地切换到内部的 RC 振荡器。如果使能了时钟中断,软件可以接收到相应的中断。

ADC(模拟/数字转换器)

产品内嵌 1 个 10 位的模拟/数字转换器(ADC),共用多达 8 个外部通道和 2 个内部通道采样,可编程的通道采样时间,可以实现单次、连续、扫描或间断转换。提供模拟看门狗功能允许非常精准地监视一路或多路选中的通道,用于监视通道信号电压。支持外部事件触发转换,触发源包括片上定时器的内部信号和外部引脚。支持使用 DMA 操作。支持外部触发延迟功能,使能该功能后,当外部触发沿产生时,控制器根据配置的延迟时间将触发信号进行延迟,延迟时间到即刻触发 ADC 转换。

定时器及看门狗

系统中的定时器包括 1 个高级定时器、1 个通用定时器、2 个看门狗定时器以及系统时基定时器。

- 高级控制定时器

高级控制定时器是一个 16 位的自动装载递加/递减计数器,具有 16 位可编程的预分频器。除了完整的通用定时器功能外,可以被看成是分配到 6 个通道的三相 PWM 发生器,具有带死区插入的互补 PWM输出功能,允许在指定数目的计数器周期之后更新定时器进行重复计数周期,刹车功能等。高级控制定时器的很多功能都与通用定时器相同,内部结构也相同,因此高级控制定时器可以通过定时器链接功能与其他 TIM 定时器协同操作,提供同步或事件链接功能。

- 通用定时器

通用定时器是一个 16 位的自动装载递加/递减计数器,具有一个可编程的 16 位预分频器以及 4个独立的通道,每个通道都支持输入捕获、输出比较、PWM 生成和单脉冲模式输出。还能通过定时器链接功能与高级控制定时器共同工作,提供同步或事件链接功能。在调试模式下,计数器可以被冻结,同时 PWM 输出被禁止,从而切断由这些输出所控制的开关。任意通用定时器都能用于产生 PWM 输出。每个定时器都有独立的 DMA 请求机制。这些定时器还能够处理增量编码器的信号,也能处理 1 至 3 个霍尔传感器的数字输出。

- 独立看门狗

独立看门狗是一个自由运行的 12 位递减计数器,支持 7 种分频系数。由一个内部独立的 128KHz的 RC 振荡器(LSI)提供时钟;LSI 独立于主时钟,可运行于待机模式。IWDG 在主程序之外,可以完全独立工作,因此,用于在发生问题时复位整个系统,或作为一个自由定时器为应用程序提供超时管理。通过选项字节可以配置成是软件或硬件启动看门狗。在调试模式下,计数器可以被冻结。

- 窗口看门狗

窗口看门狗是一个 7 位的递减计数器,并可以设置成自由运行。可以被用于在发生问题时复位整个系统。其由主时钟驱动,具有早期预警中断功能;在调试模式下,计数器可以被冻结。

- 系统时基定时器(SysTick)

这是内核控制器自带的一个 32 位递增的计数器,用于产生 SYSTICK 异常(异常号:15),可专用于实时操作系统,为系统提供“心跳”节律,也可当成一个标准的 32 位计数器。具有自动重加载功能及可编程的时钟源。

通讯接口

- 通用同步/异步收发器(USART)

产品提供了 1 组通用同步/异步收发器(USART)。支持全双工异步通信、同步单向通信以及半双工单线通信,也支持 LIN(局部互连网),兼容 ISO7816 的智能卡协议和 IrDA SIR ENDEC 传输编解码规范,以及调制解调器(CTS/RTS 硬件流控)操作,还允许多处理器通信。其采用分数波特率发生器系统,并支持 DMA 操作连续通讯。

- 串行外设接口(SPI)

1 个串行外设 SPI 接口,提供主或从操作,动态切换。支持多主模式,全双工或半双工同步传输,支持基本的 SD 卡和 MMC 模式。可编程的时钟极性和相位,数据位宽提供 8 或 16 位选择,可靠通信的硬件 CRC 产生/校验,支持 DMA 操作连续通讯。

- I2C 总线

1 个 I2C 总线接口,能够工作于多主机模式或从模式,完成所有 I2C 总线特定的时序、协议、仲裁等,支持标准和快速两种通讯速度。

I2C 接口提供 7 位或 10 位寻址,并且在 7 位从模式时支持双从地址寻址。内置了硬件 CRC 发生器/校验器。

通用输入输出接口(GPIO)

系统提供了 3 组 GPIO 端口,共 18 个 GPIO 引脚。每个引脚都可以由软件配置成输出(推挽或开漏)、输入(带或不带上拉或下拉)或复用的外设功能端口。多数 GPIO 引脚都与数字或模拟的复用外设共用。除了具有模拟输入功能的端口,所有的 GPIO 引脚都有大电流通过能力。提供锁定机制冻结 IO 配置,以避免意外的写入 I/O 寄存器。

系统中 IO 引脚电源由 VDD提供,通过改变 VDD供电将改变 IO 引脚输出电平高值来适配外部通讯接口电平。具体引脚请参考引脚描述。

运放/比较器(OPA)

产品内置 1 组运放/比较器,内部选择关联到 ADC 和 TIM2 外设,其输入和输出均可通过更改配置对多个通道进行选择。支持将外部模拟小信号被放大送入 ADC 以实现小信号 ADC 转换,也可以完成信号比较器功能,比较结果由 GPIO 输出或者直接接入 TIMx 的输入通道。

串行单线调试接口(1-wire SDI Serial Debug Interface)

内核自带一个串行单线调试的接口,SWIO 引脚(Single Wire Input Output)。系统上电或复位后默认调试接口引脚功能开启。