FPGA从1984 年到今天,发展经历了30 多年时间。它可以替代其他 PLD 或者各种中小规模数字逻辑芯片在数字系统中广泛应用,也是实现具有不同逻辑功能ASIC 的有效办法。

FPGA 融合了 ASIC 和基于处理器的系统的最大优势,它能够提供硬件定时的速度和稳定性,且无需类似自定制 ASIC 设计的巨额前期费用的大规模投入。但是和所有的数字电路一样,FPGA 电路中也存在毛刺问题。它的出现会影响电路工作的可靠性、稳定性,严重时会导致整个数字系统的误动作和逻辑紊乱。下面就来讨论交流一下FPGA 的竞争冒险与毛刺问题。

在数字电路中,常规介绍和解释:

什么是竞争与冒险现象:

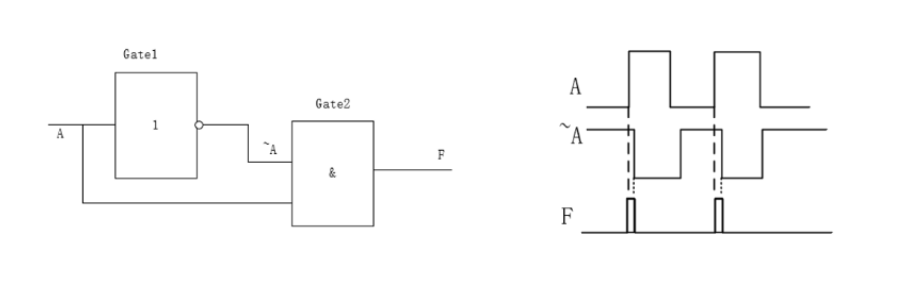

在组合电路中,某一输入变量经过不同途径传输后,到达电路中某一汇合点的时间有先有后,这种现象称竞争;由于竞争而使电路输出发生瞬时错误的现象叫做冒险。(也就是由于竞争产生的毛刺叫做冒险)。

判断方法:

1、代数法(如果布尔式中有相反的信号则可能产生

竞争和冒险现象);

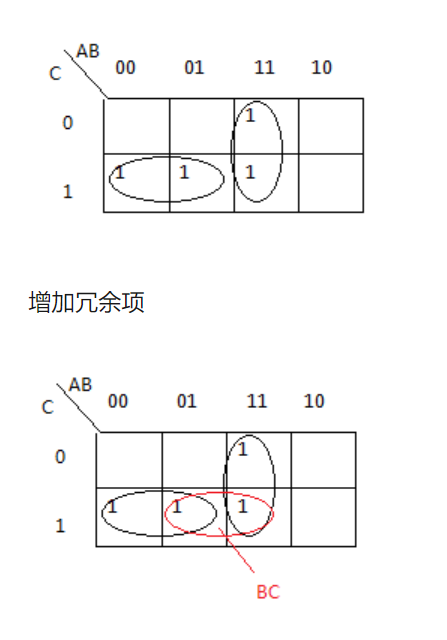

2、卡诺图:有两个相切的卡诺圈并且相切处没有被其他卡诺圈包围,就有可能出现竞争冒险;

3、实验法:示波器观测;

解决方法:

1、加滤波电路,消除毛刺的影响;

2、加选通信号,避开毛刺;

3、增加冗余项消除逻辑冒险。

那么 FPGA 产生竞争冒险的原因是什么呢?

信号在 FPGA 器件内部通过连线和逻辑单元时,都有一定的延时。延时的大小与连线的长短和逻辑单元的数目有关;同时还受器件的制造工艺、工作电压、温度等条件的影响;信号的高低电平转换也需要一定的过渡时间。

由于以上存在的因素,多路信号的电平值发生变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,并不是同时变化,往往会出现一些不正确的尖峰信号,这些尖峰信号称为“毛刺”。

如果一个组合逻辑电路中有“毛刺”出现,就说明该电路存在“冒险”。(与分立元件不同,由于 PLD 内部不存在寄生电容电感,这些毛刺将被完整的保留并向下一级传递,因此毛刺现象在 PLD、FPGA 设计中尤为突出)。毛刺的累加,将会影响整个设计的可靠性和精确性。因此判断逻辑电路中是否存在冒险以及如何避免冒险是 FPGA 设计人员必须要考虑的问题。

接下来我们就要考虑如何消除冒险,消除冒险的方式有以下几种:

1、利用冗余项消除毛刺函数式和真值表所描述的是静态逻辑,而竞争则是从一种稳态到另一种稳态的过程。因此竞争是动态过程,它发生在输入变量变化时。此时,修改卡诺图,增加多余项,在卡诺图的两圆相切处增加一个圆,可以消除逻辑冒险。但该法对于计数器型产生的毛刺是无法消除的。

2、采用格雷码我们可以通过改变设计,破坏毛刺产生的条件,来减少毛刺的发生。例如,在数字电路设计中,常常采用格雷码计数器取代普通的二进制计数器,这是因为格雷码计数器的输出每次只有一位跳变,消除了竞争冒险的发生条件,避免了毛刺的产生。

3、采样法由于冒险出现在变量发生变化的时刻,如果待信号稳定之后加入取样脉冲,那么就只有在取样脉冲作用期间输出的信号才能有效。这样可以避免产生的毛刺影响输出波形。一般说来,冒险出现在信号发生电平转换的时刻,也就是说在输出信号的建立时间内会发生冒险,而在输出信号的保持时间内是不会有毛刺信号出现的。如果在输出信号的保持时间内对其进行“采样”,就可以消除毛刺信号的影响。

4、吸收法增加输出滤波,在输出端接上小电容C可以滤除毛刺。但输出波形的前后沿将变坏,在对波形要求较严格时,应再加整形电路,该方法不宜在中间级使用。

5、延迟办法因为毛刺最终是由于延迟造成的,所以可以找出产生延迟的支路。对于相对延迟小的支路,加上毛刺宽度的延迟可以消除毛刺。还可以用高频时钟来驱动一移位寄存器,待延时信号作数据输入,按所需延时正确设置移位寄存器的级数,移位寄存器的输出即为延时后的信号。

当然最好的就是,在设计之初,就对竞争冒险进行规避,具体规避方法有:

1、在设计中每一个模块中只用一个时钟,避免使用多时钟设计,同时避免使用主时钟分频后的二次时钟作为时序器件的时钟输入,因为时钟偏斜会比较大。

2、设计译码逻辑电路时必须十分小心,因为译码器和比较器本身会产生尖峰,容易产生毛刺,把译码器或比较器的输出直接连到时钟输入端或异步清除端,会造成严重的后果。

3、在设计中应该尽量避免隐含 RS 触发器的出现。一般要控制输出被直接反馈到输入端,采用反馈环路会出现隐含 RS 触发器,其对输入尖峰和假信号很敏感,输入端有任何变化都有可能使输出值立刻改变,此时易造成毛刺的产生,导致时序的严重混乱。

4、在设计电路时要用寄存器和触发器设计电路,尽量不要用锁存器,因它对输入信号的毛刺太敏感。如果坚持用锁存器设计必须保证输入信号绝对没有毛刺,且满足保持时间。

5、在设计中充分利用资源,因为大部分 FPGA 器件都为时钟、复位、预置等信号提供特殊的全局布线资源,要充分利用这些资源。

6、在设计中不论是控制信号还是地址总线信号、数据总线信号,都要采用另外的寄存器,以使内部歪斜的数据变成同步数据。

7、在设计中应该尽量避免使用延迟线,因它对工艺过程的变化极为敏感,会大大降低电路的稳定性和可靠性,并将为测试带来麻烦。

8、在设计中对所有模块的输入时钟、输入信号、输出信号都用D触发器或寄存器进行同步处理,即输出信号直接来自触发器或寄存器的输出端。这样可以消除尖峰和毛刺信号。

注:仿真结果和实际综合的电路的不一致性。无论是时序电路还是异步逻辑电路,其行为与其仿真器结果都是不完全一样的,不要期望仿真器替你找到错误。