感谢“小眼睛FPGA”发起的这次试用活动,让我有机会近距离感受国产FPGA的魅力。

话不多说,直接开箱上板子。

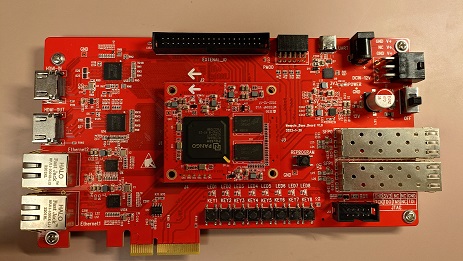

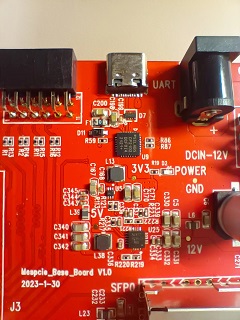

盘古50采用的是常见的核心板+底板的设计,可以最大程度的满足定制化的需求。开发板用料扎实,器件摆放整齐,焊点清晰饱满,走线都做了等长处理。

核心板上配备了大容量512MB DDR3,扩展了FPGA片外存储,满足了图像处理应用对高带宽大容量存储的需求。

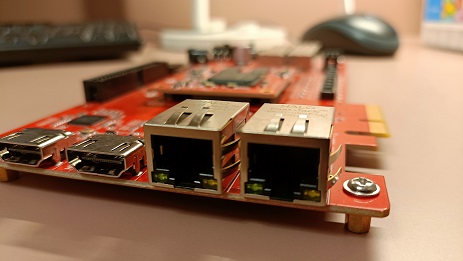

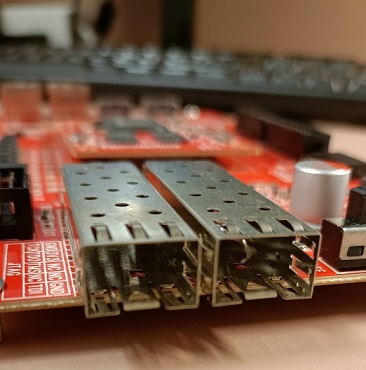

底板提供了两路千兆以太网,两路光纤接口以及PCIE接口,可以覆盖大多数数据传输的应用场景。有点遗憾,没有USB HOST或是Device接口。

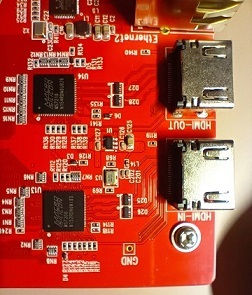

HDMI输入输出接口采用外挂专用PHY的形式,可以支持不同的图像信号格式以及音频信号传输。

底板还贴心地提供了USB TypeC转串口,可以使FPGA直接与PC之间进行信息交互,而不需要额外的转接模块。

外扩的40Pin和PMOD的接口可以用于一些外设(比如摄像头、传感器、ADC和DAC)的接入和控制信号的输出。

板载的EEPROM和SD卡分别通过IIC和SPI接入FPGA,可以用于掉电信息的存储,后者更是可以充当“硬盘”,实现GB量级的数据存储。

另外,还有8组LED和8组按键可以完成一些简单的人机交互。

从接触的第一印象来看盘古50是一款优秀开发板。相信无论是在图像视频以及通信信号处理领域,还是数据采集方向,盘古50都会有出色的表现。

下面通过点亮LED的实验,来熟悉新的开发环境和开发流程。紫光提供的IDE全称为“Pango Design Suite”,在主界面直接通过“Open Project”选项,可以打开LED例程。

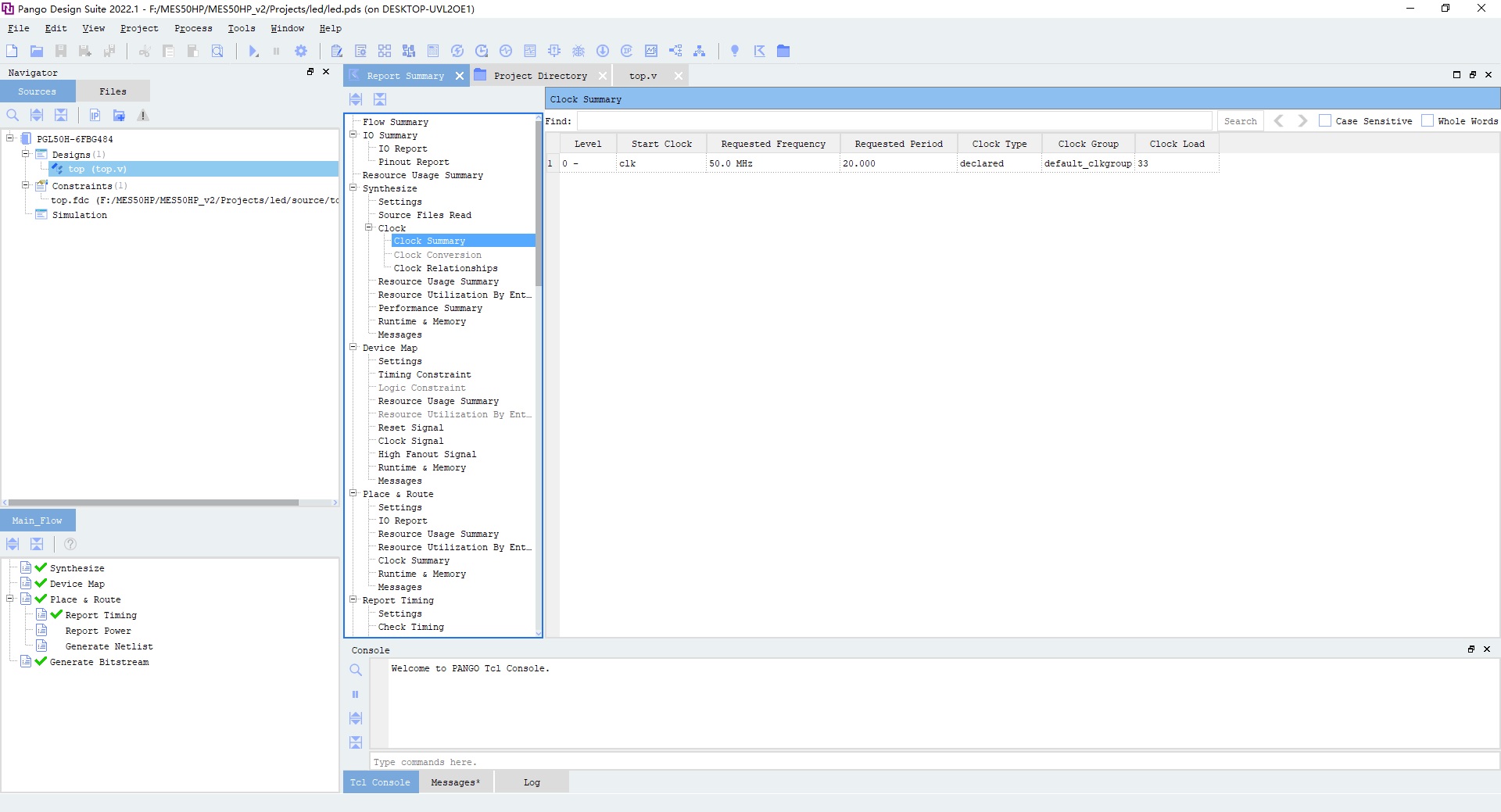

打开工程后,可以看到主界面分成了三个部分,左上显示了源文件和约束文件,左下展示了整体编译产生bit文件的流程,右边区域用于文件信息的显示。默认是“Report Summary”,可以找到当前工程的编译报告,包括IO管脚的约束,资源利用,综合的时序报告以及布局布线的报告等等。

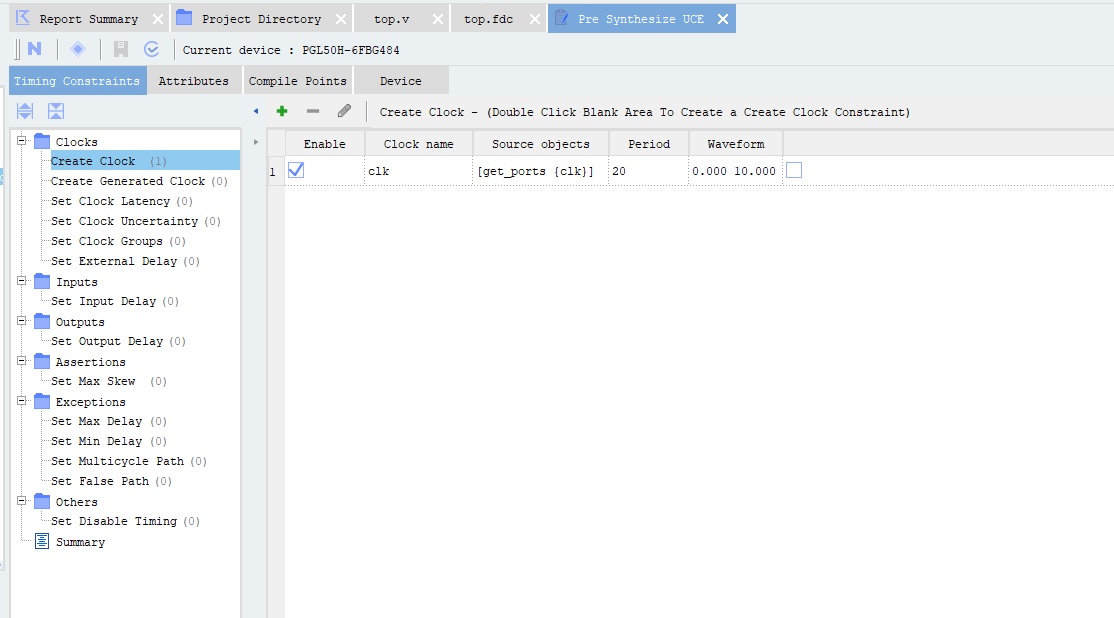

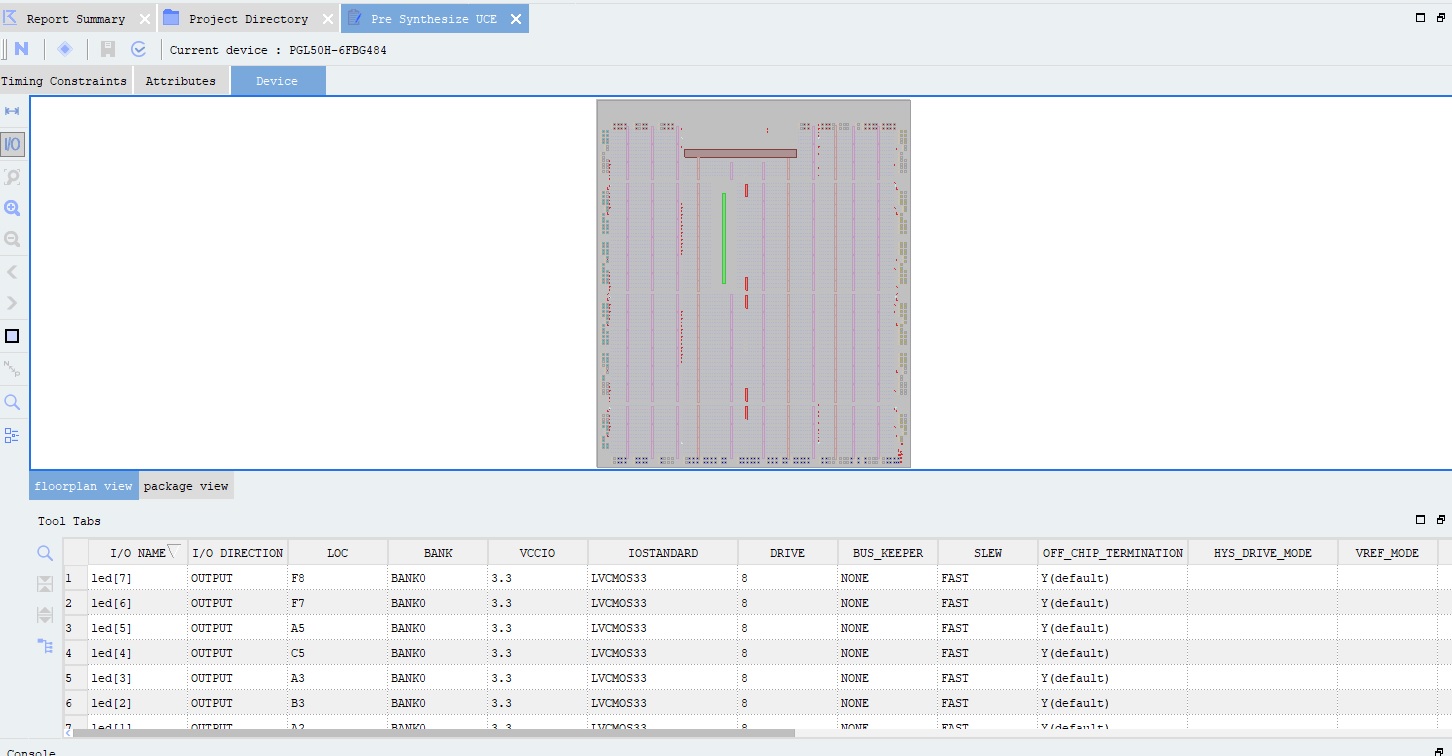

菜单栏的Tools,选中“User Constraint Editor”,再下一步打开“Pre Synthesize UCE”,在“Timing Constraints”一栏可以进行Timing的约束

选择“Device”一栏,可以进行IO pin的约束

当完成RTL和约束文件的编写后,可以在左下的“Main FLow”点击“Generate Bitstream”,一键生成FPGA下载所需的bit文件。

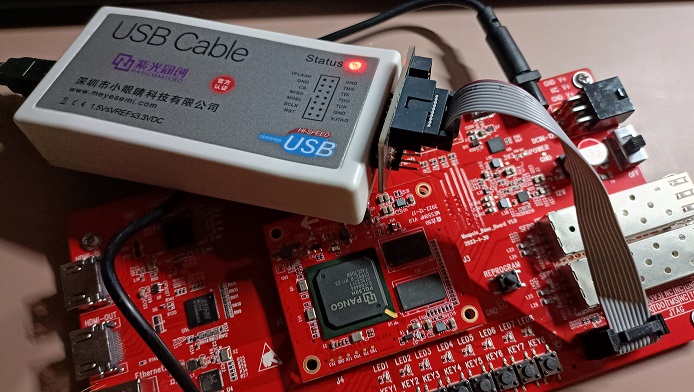

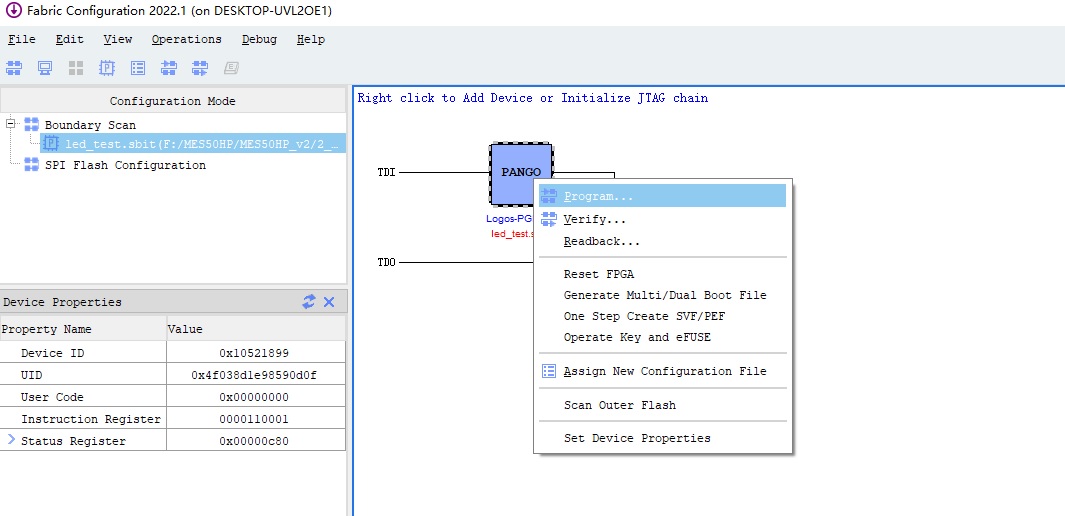

产生了bit文件后,点击Tools下面的Configuration进行下载配置。插上调试器,在弹出的窗口中点击File,选择Scan Device,找到需要进行下载的FPGA,选择配置的bit,最后进行program。

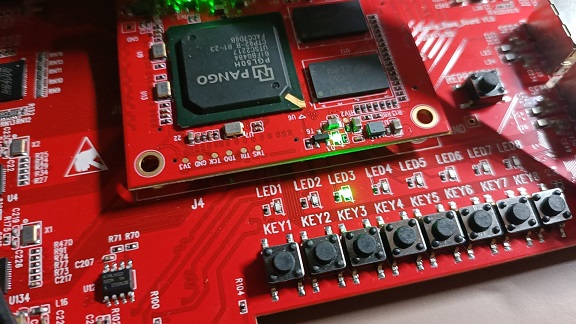

完成下载后,程序自动开始运行,效果就是简单的LED1~LED8循环点亮。

总结一下,这里快速体验了一个工程从创建,RTL和约束的编写、编译到最后的运行的流程。体验下来最直观的感受就是,新的IDE的学习成本基本为零,可以称为秒上手。

后续将会深入器件的性能进行进一步体验。