|

并行功能可以说是这个芯片最大的一个特点了,对于多路高实时控制来说,是很用的。

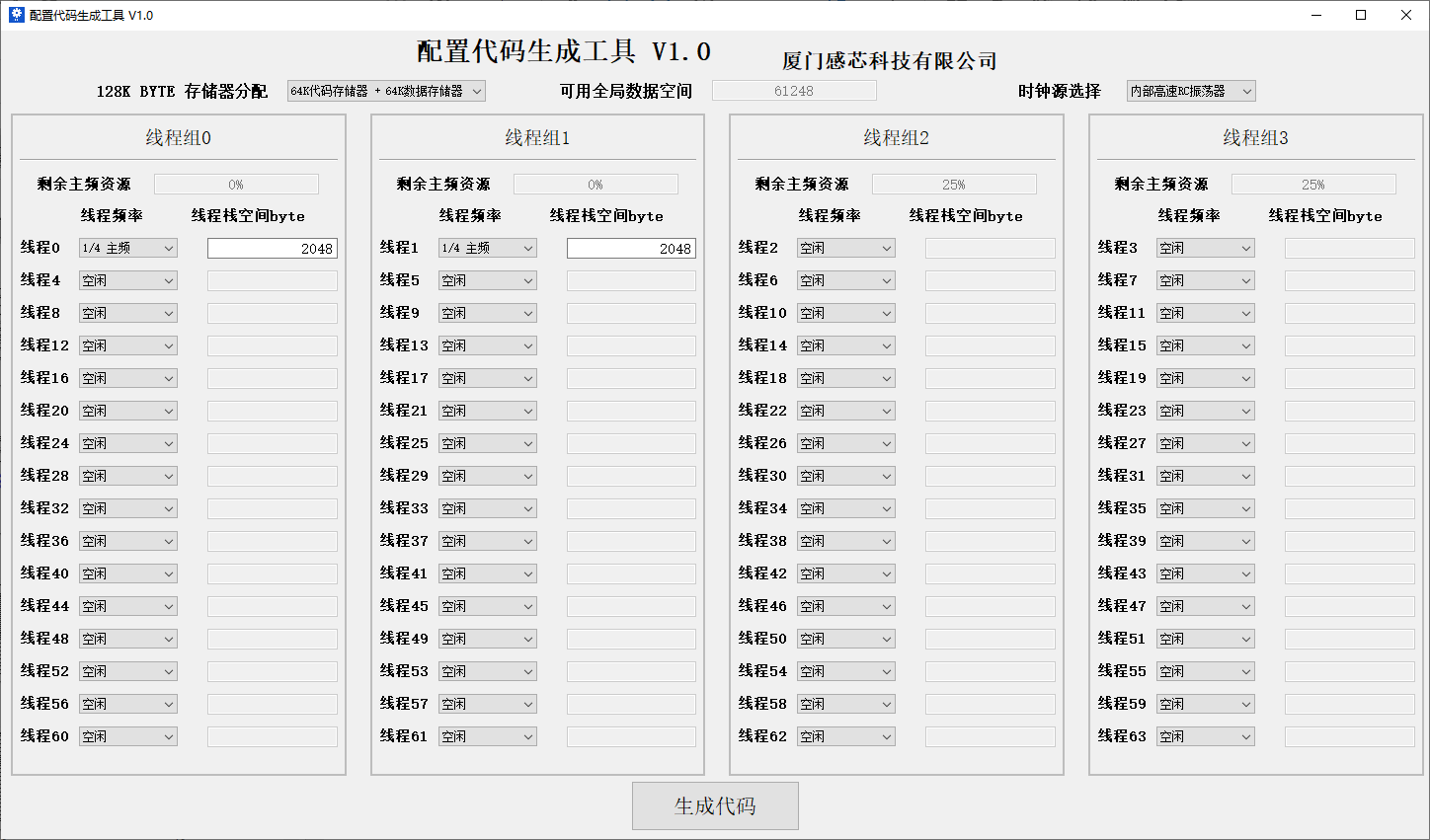

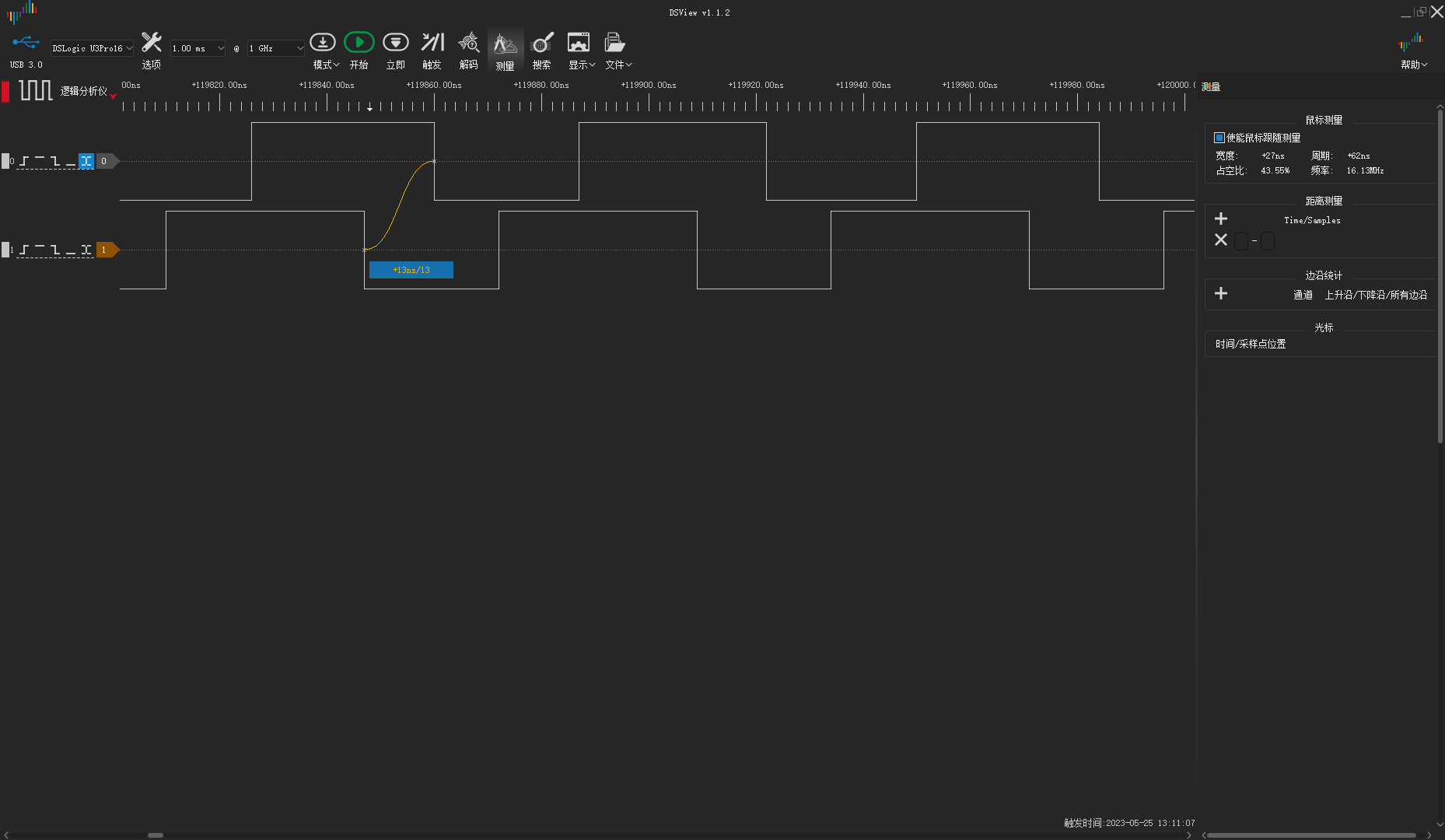

这里先启动了两个线程,把时钟设置为内部高速时钟,主频可以到达200M。每个线程使用一个GPIO进行翻转。为了确定每次线程的开始时间,把GPIO翻转设置成一次,下降沿是进程的开始位置,这样好进行测量。

代码如下:

void thread0_main(void)

{

INTDEV_SET_CLK_RST(GPIOD_BASE_ADDR,(INTDEV_RUN|INTDEV_IS_GROUP0|INTDEV_CLK_IS_CORECLK_DIV2));

GPIO_SET_OUTPUT_EN_VALUE(GPIOD_BASE_ADDR,(GPIO_PIN0),GPIO_SET_ENABLE);

while(1){

GPIO_SET_OUTPUT_PIN_TO_0(GPIOD_BASE_ADDR,(GPIO_PIN0));

GPIO_SET_OUTPUT_PIN_TO_1(GPIOD_BASE_ADDR,(GPIO_PIN0));

}

thread_end();

}

////////////////////////////////////////////////////////////

void thread1_main(void)

{

INTDEV_SET_CLK_RST(GPIOA_BASE_ADDR,(INTDEV_RUN|INTDEV_IS_GROUP0|INTDEV_CLK_IS_CORECLK_DIV2));

GPIO_SET_OUTPUT_EN_VALUE(GPIOA_BASE_ADDR,(GPIO_PIN15),GPIO_SET_ENABLE);

while(1){

GPIO_SET_OUTPUT_PIN_TO_0(GPIOA_BASE_ADDR,(GPIO_PIN15));

GPIO_SET_OUTPUT_PIN_TO_1(GPIOA_BASE_ADDR,(GPIO_PIN15));

}

thread_end();

}

如下所示,两个低电平的时间差大约是13ns,这个时间延时是非常低的了。但这个时间并不是绝对时间,随着程序运行时间,这个时间也是在变化的。

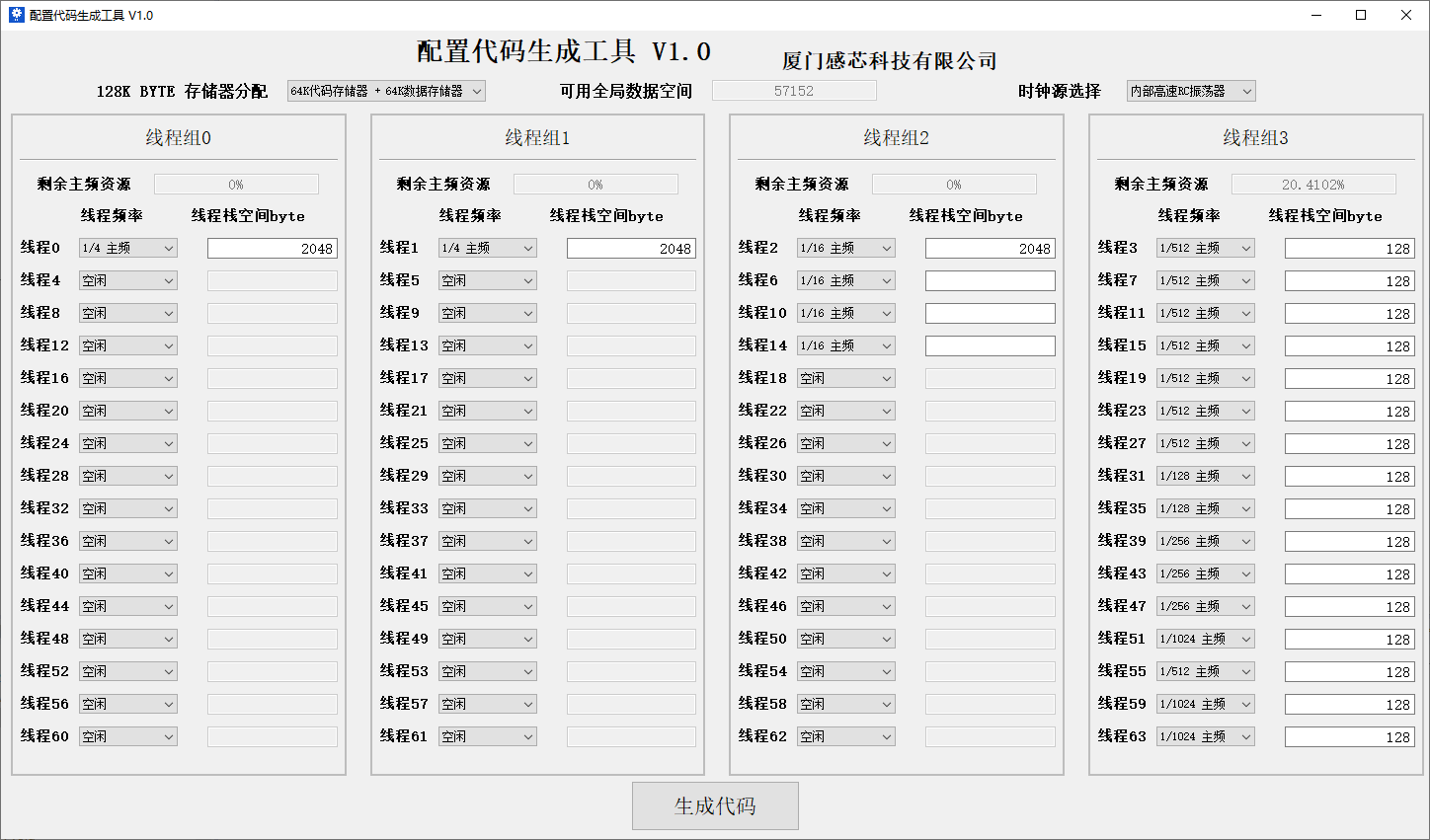

两个线程调度还是比较好处理的,那再多添加几个线程呢,如下图所示:

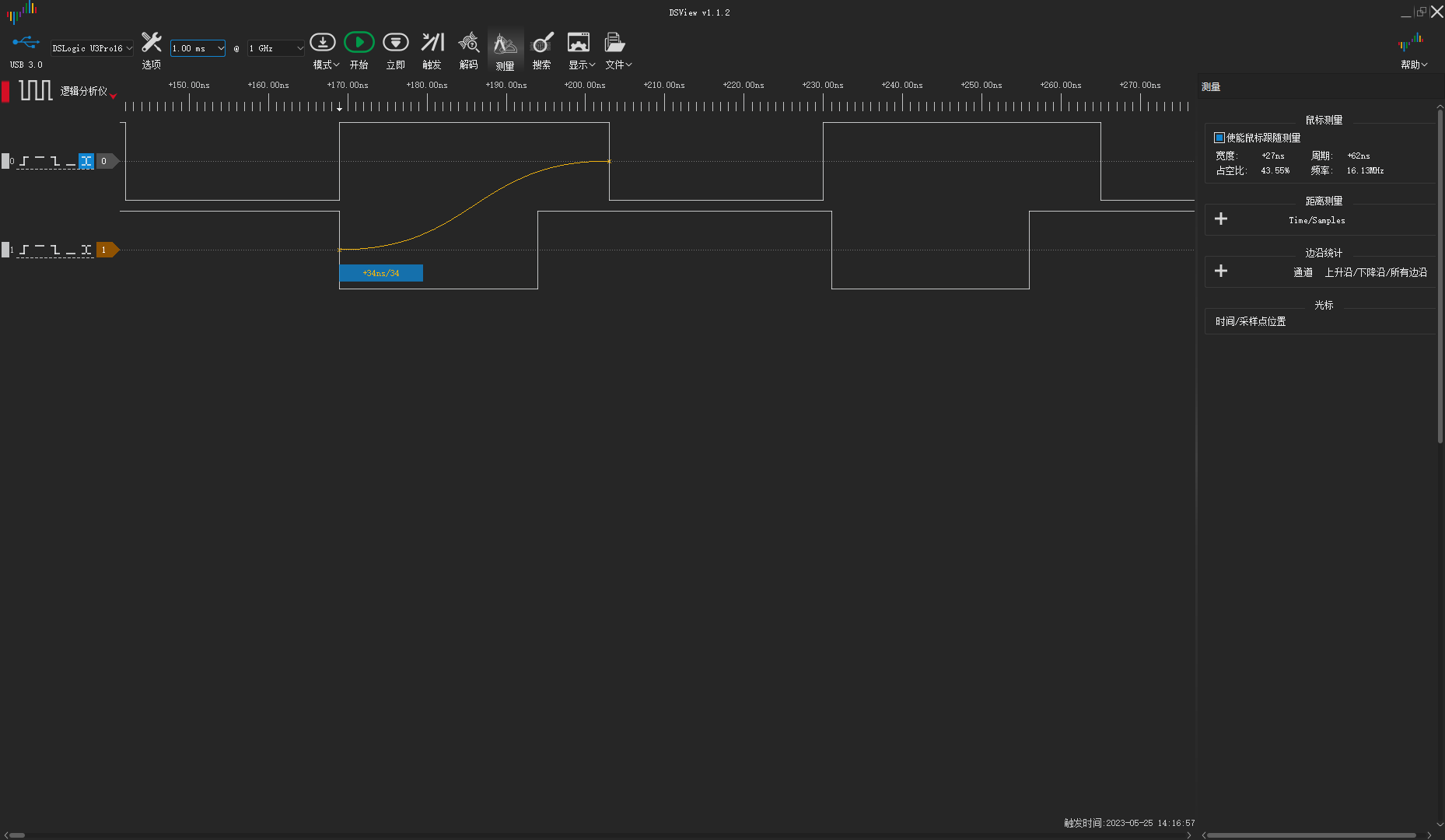

这时,再测量线程0与线程1中的GPIO翻转延时,两个下降沿之间的时间差最约为34ns。

由于添加的几个线程都是空的,只是占用了一个位置,可能线程中添加相应的代码后,这个调度时间也还是会有所变化。不过对于这个时间来说,也几乎算是并行 了。

所以,此芯片并不是与FPGA似的结构原理,猜测还应该是内部有一个调度机制,并行运行是在这个机制上进行优化,最大程度的减小线程调度所需要的时间。

对目前的调度时间来说,确实是比RTOS要快很多,大部分实时性要求高的场景都可以使用的,但也要注意这个时间,有严格时序要求的,还得用FPGA。

芯片的外设目前还不是很丰富,但每组都可以设置成相应的功能,可以全设置成串口或是CAN或是SPI,一些特殊应用就比较合适,比如全设置成CAN接口,可以做成多路的CAN总线分析工具。

|