前言

本文期望通过板载硬件SPI外加DMA传输的方式来实现对全差分同步采样模数转换器ADS8354的控制,并且将采集数据进行初步脉冲压缩,迎合以下本人正在进行的项目,同时对开发板进行测评。

简易介绍

ADS8354

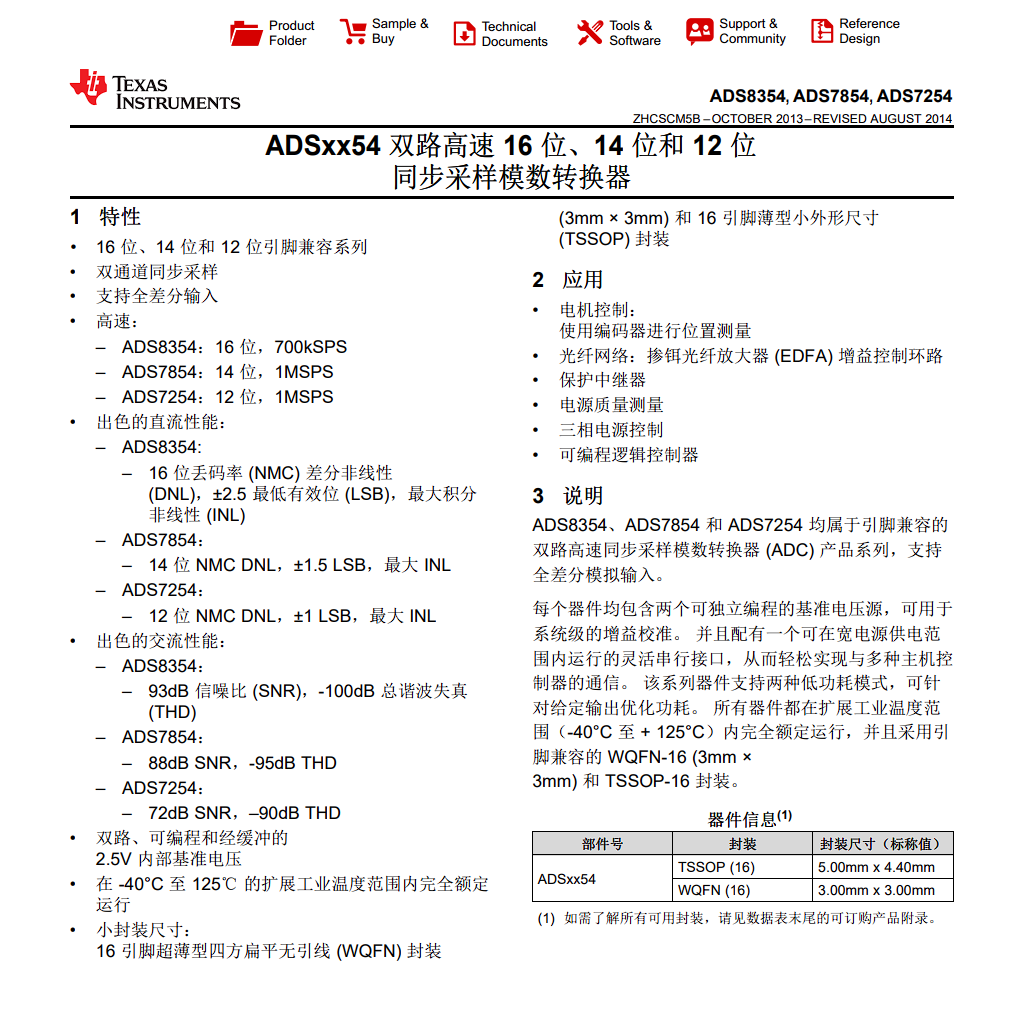

·首先,对于一款不熟悉的芯片,看一下官方手册的概述,可以得到一些简略信息,如下图所可以的到的信息有:同步采样、差分输入、700KSPS采样率、16位、双路内部参考电压2.5V

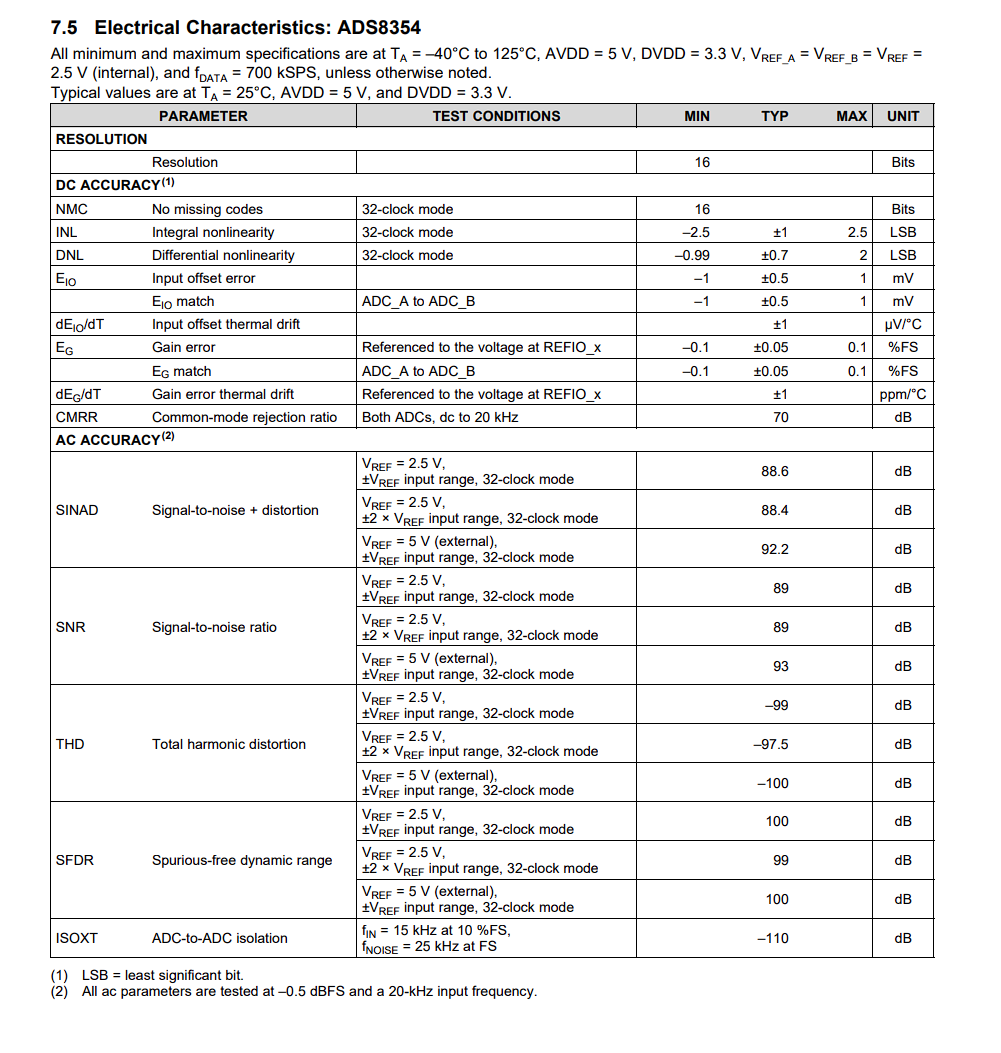

·其次,我会关注以下芯片的极限性能,也就是下图所示部分,关于这部分一般会关注电气特性(不画板子就简易了解就好)、时序特性(写代码请重点关注)

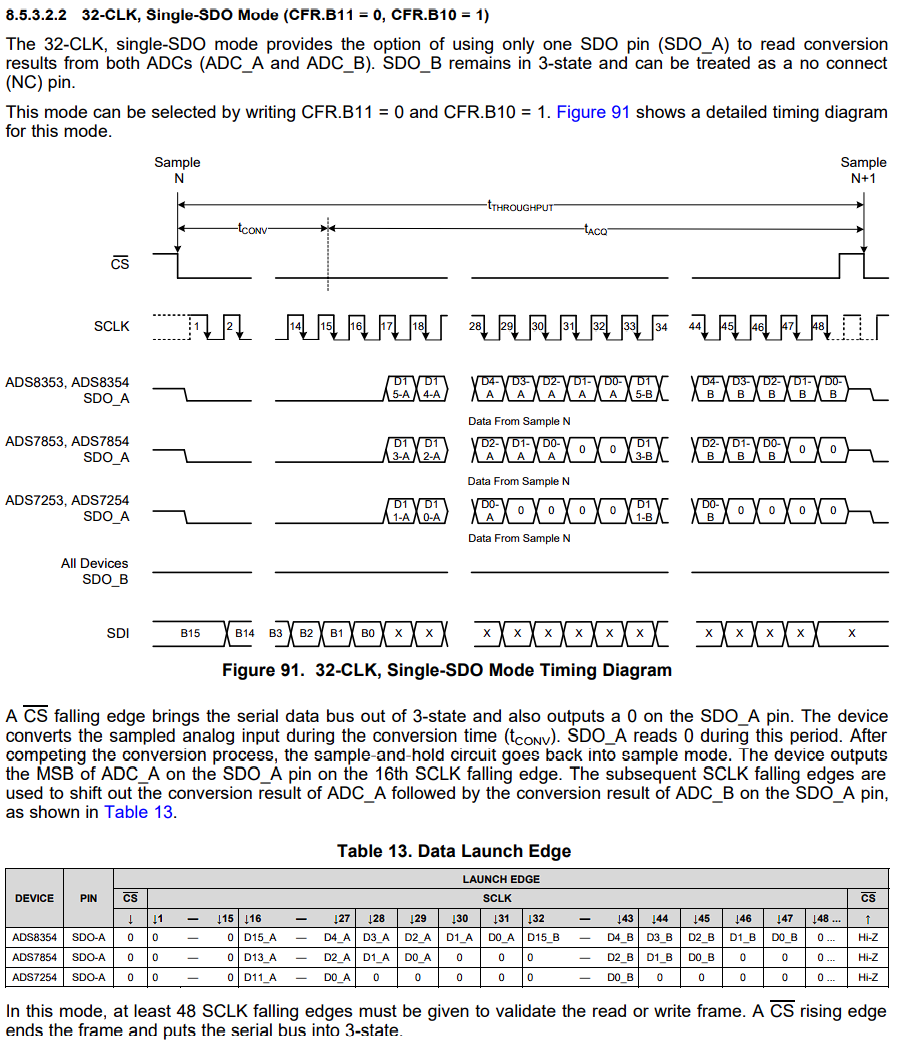

· 关于这块参数为什么要看呢?因为在压榨芯片的极限性能的时候,就需要参照这一部分参数,比如针对“Timing Characteristics: Serial Interface”部分参数(上图并未直接给出),可以得到芯片在“32-CLK, Dual-SDO Mode (CFR.B11 = 0, CFR.B10 = 0, Default)”工作模式下,一个最小时钟周期为41.66ns,也就是24Mhz,诸如此类还有很多,请自行查阅官方手册。

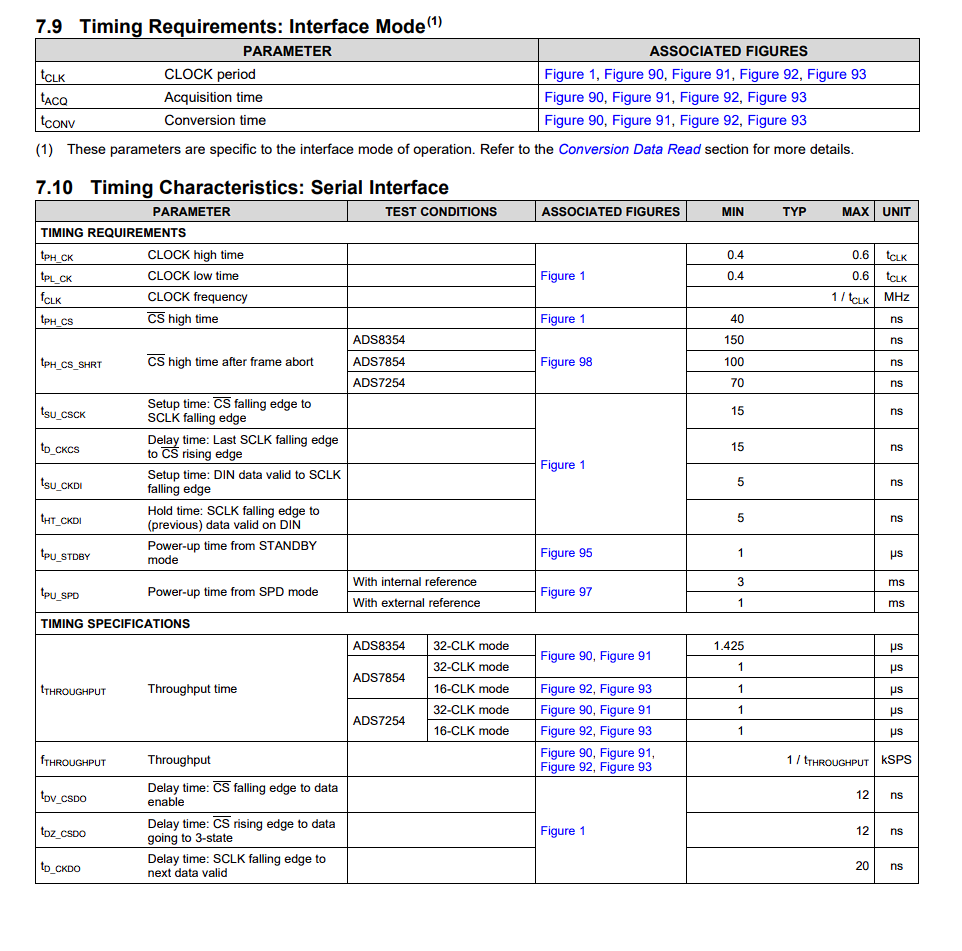

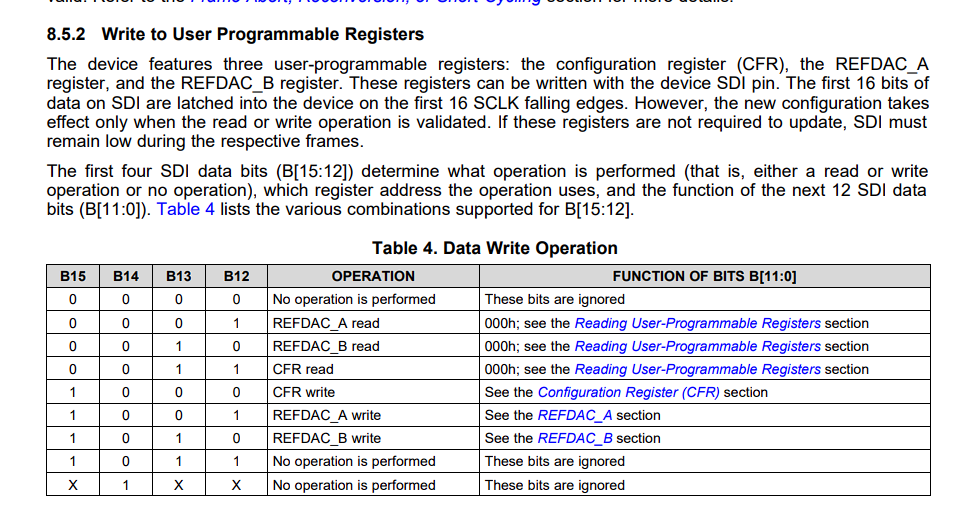

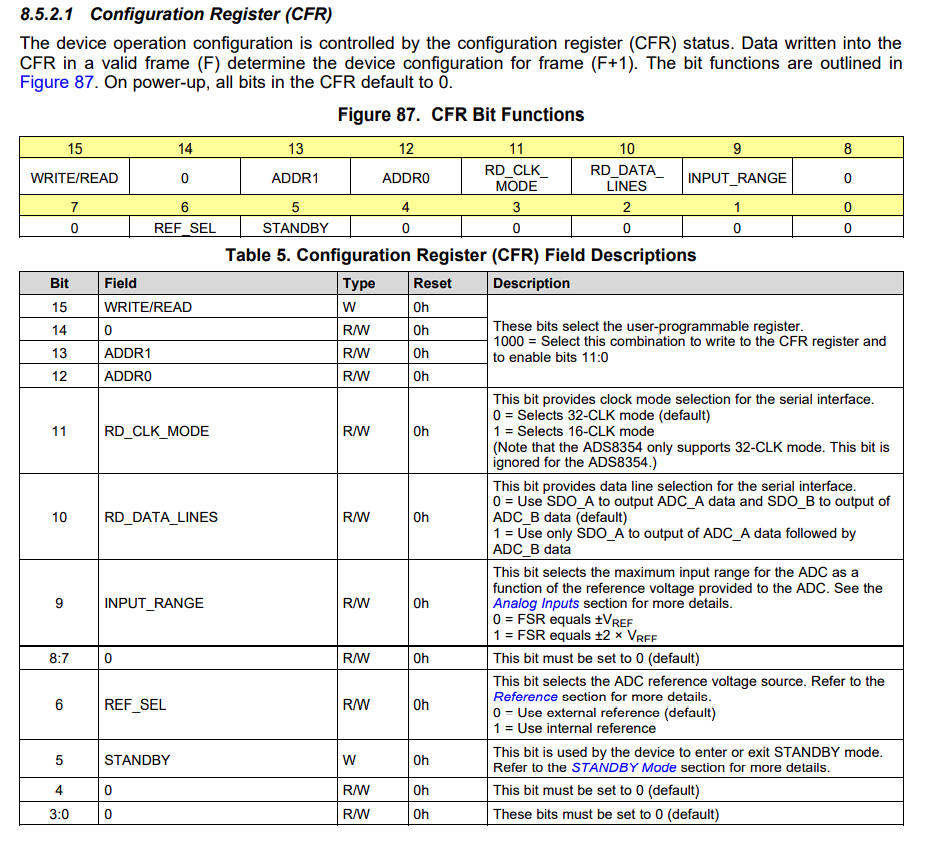

·最后,也是对写代码最为重要的,如下图所示的芯片的寄存器特性以及串行接口,在下文进行分别解读

如上图所示,有三个可以被写入的寄存器分别是CFR、REFDAC\_A和REFDAC\_B

· REFDAC\_A和REFDAC\_B:分别是A路和B路内部基准电压的控制寄存器

· CFR:配置寄存器,配置一些初始化参数等

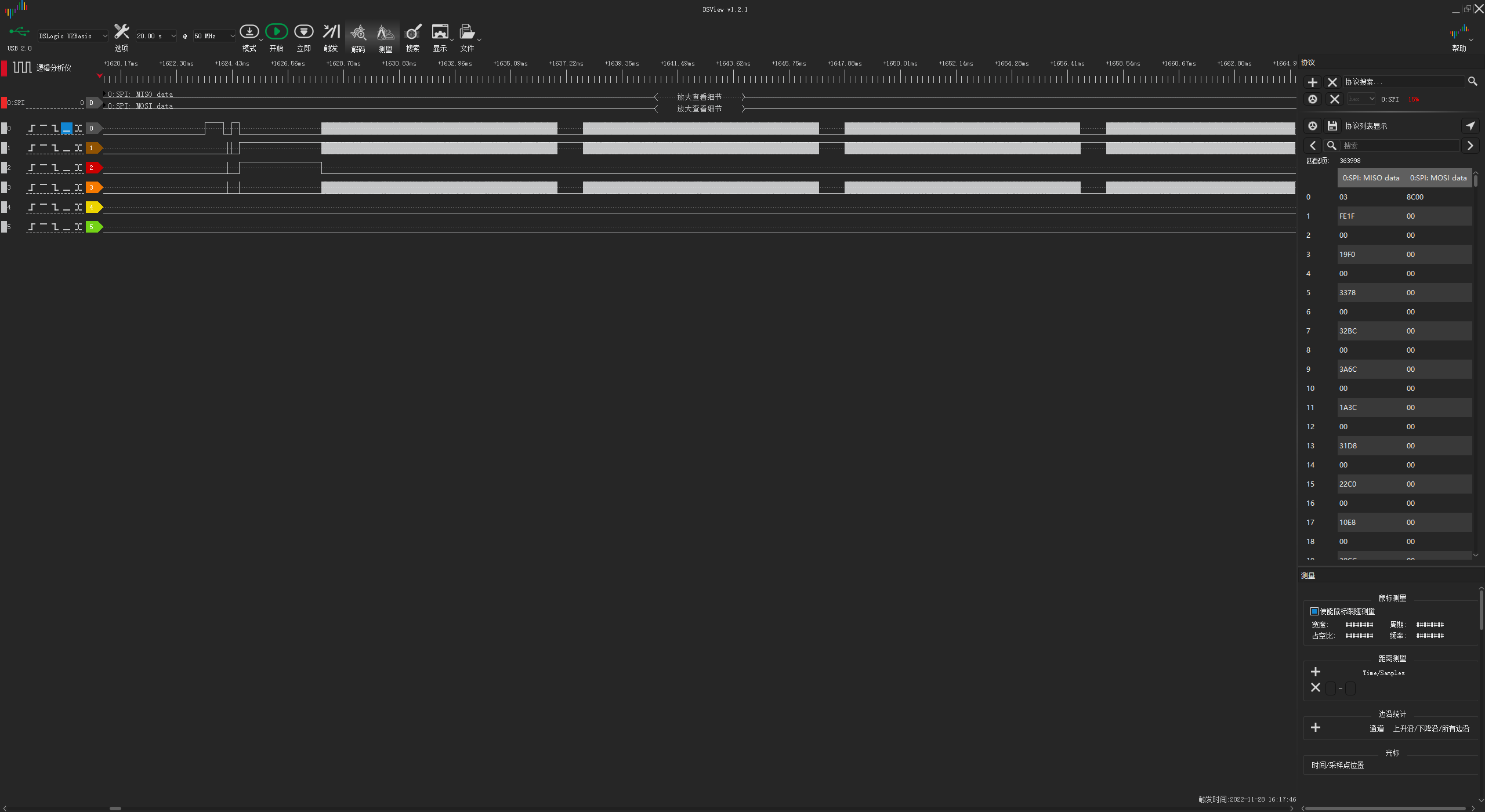

· 由于在硬件设计上,采用的是外部2.5V基准电压供电、SDOA上输出A路和B路的ADC转换数据,所以如上图所示针对CFR寄存器,应该写入的数值为:0X8600;如果是其他配置,请自行配置。

· 如上图所示,在进行读取的时候,每一帧数据有48Bit,前16Bit为留给ADC转换数据用,所以数据无意义,中间16Bit为A口数据,最后16Bit为B口数据。

GD32F427评测

·前期准备

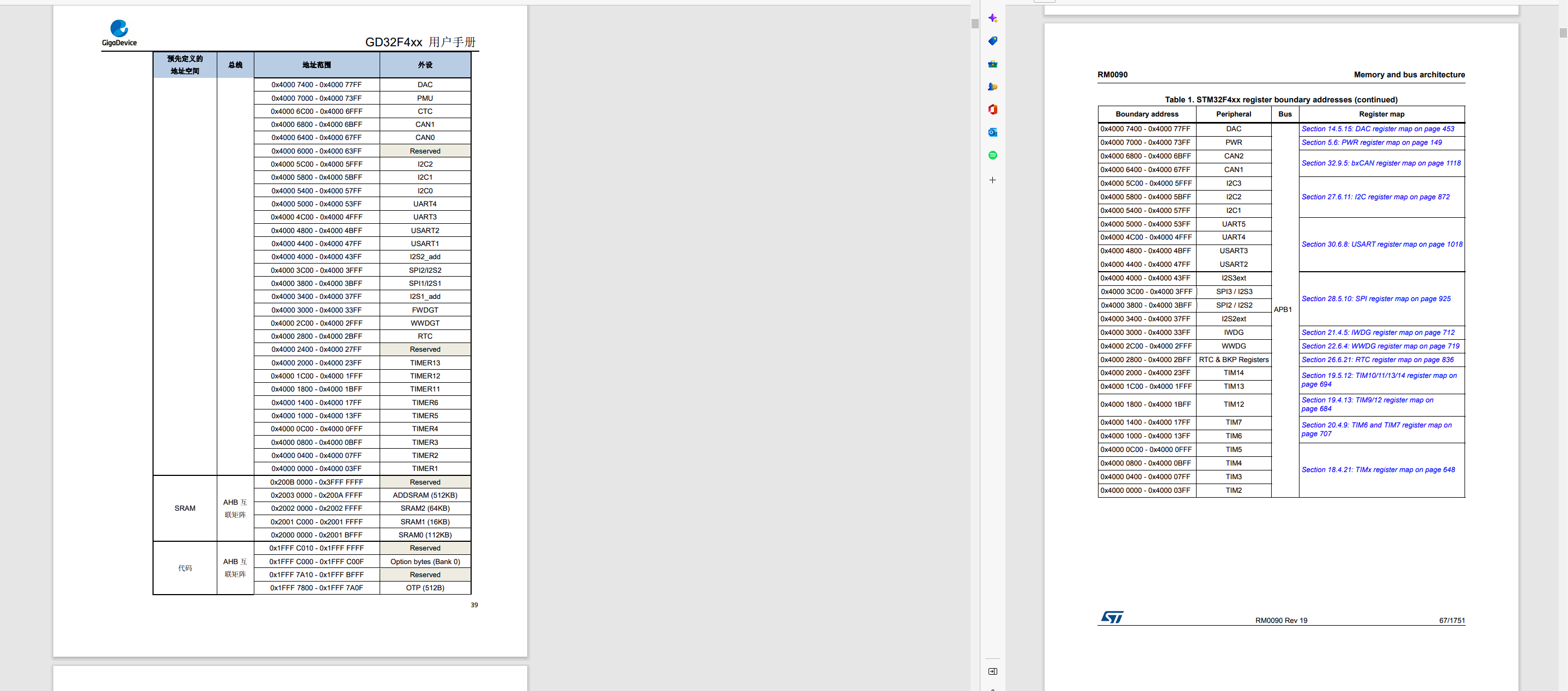

1>拿到开发板我,我第一件事做的是下载了其芯片手册,然后跟STM32F427的芯片手册做对比。如下图:

我关注了一下我此次要用的外设SPI1、UART1、DMA等,对比发现其Memory Map是完全兼容的,那么拿以前的F4的工程理论上来说是可以直接替代的。也就可以完全平替STM32了。但理论终究是理论,下面我们来进行相应尝试。

2>写代码之前,需要对相应环境进行搭建,其实步骤并不多,主要是安装相应PACK,资料在极术社区都很完善了,这里就不展开赘述了(安装下图中的PACK)

然后打开MDK➡魔术棒➡Device,看到如下图所示,即代表安装成功

·正式开始

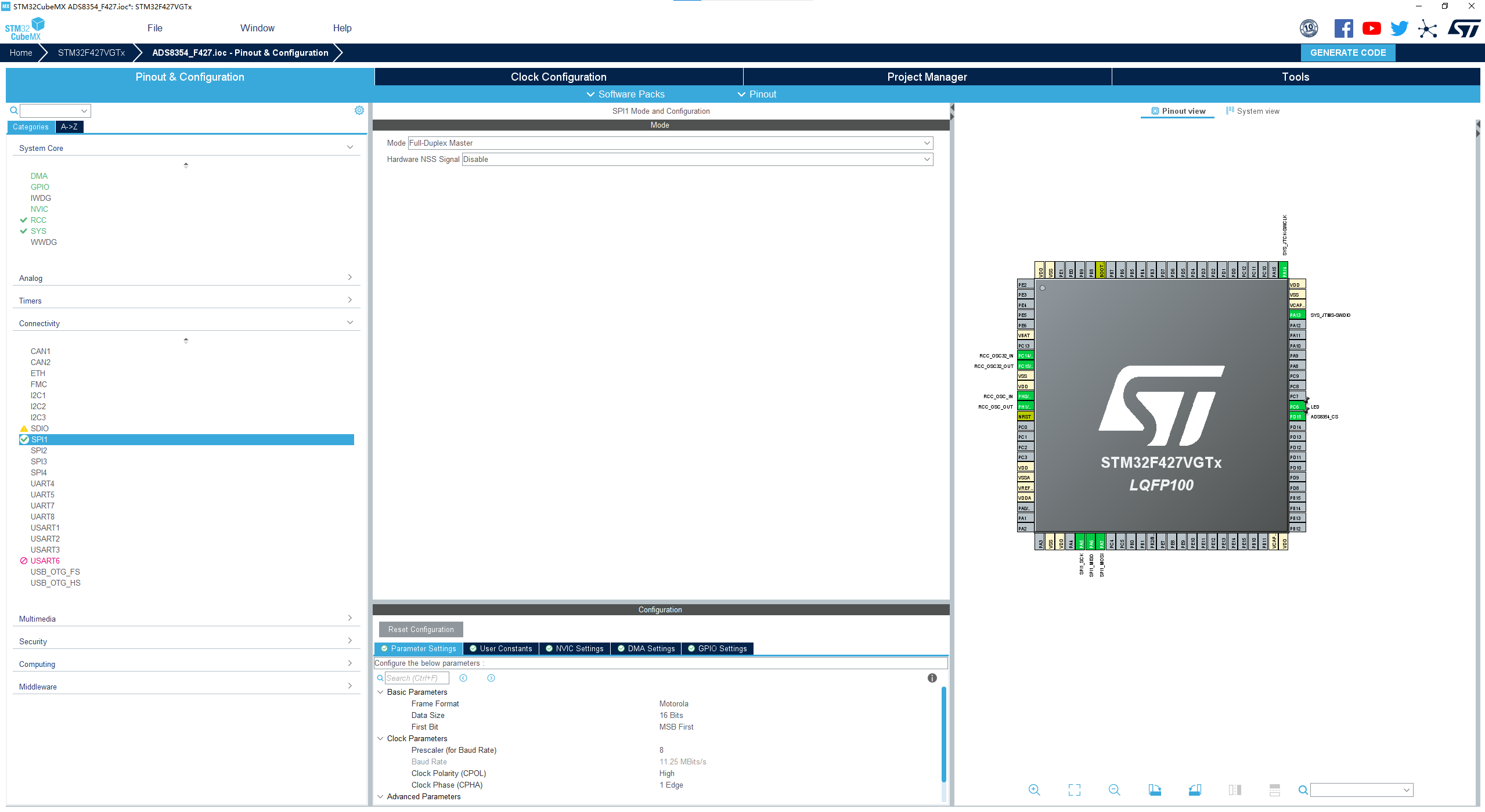

1>采用传统的cubemx帮我们生成一下底层代码,配置如下:

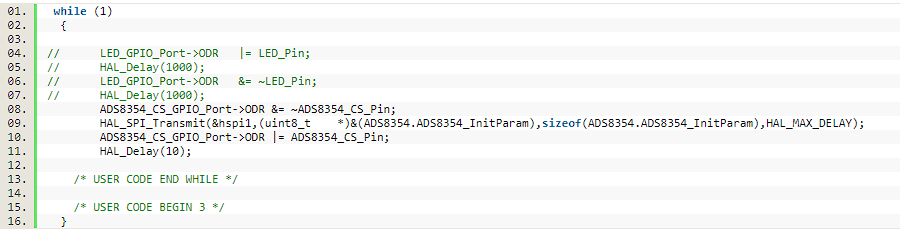

首先,在配置SPI时稍微注意一下,手册里写了是在每个时钟的下降沿读取数据,所以在这里SPI的时钟极性应该为高,时钟相位应该奇数读取(也就是为1),然后时钟分频应该选择大于四分频(此时为22.5Mhz,满足ADS的最大时钟输入);但是,由于本人手中逻辑分析仪最大支持四通道50M采样,为了观察协议,在这里进行了8分频。其次,选用了PD15脚作为CS引脚。写一段测试代码:

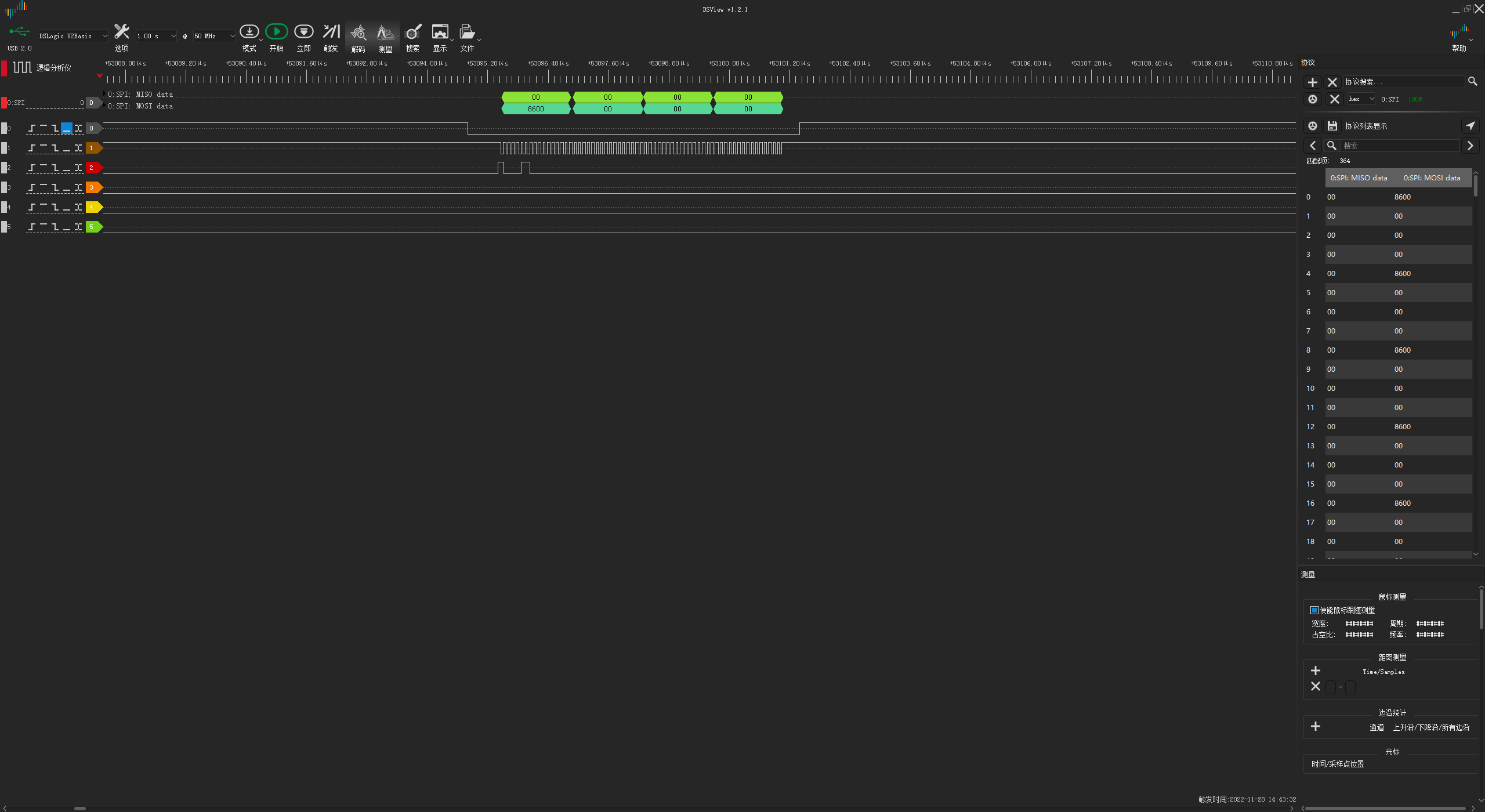

然后,用逻辑分析仪抓一下发送时序:

???????

what??

CS引脚拉低无效,中间跟着其他的引脚在跳动????

到了这里,我又去查阅了GD32的数据手册,并且go to define在HAL库中关于GPIO的封装结构体以及他们对应的地址偏移,是否有偏差,花了时间没多久,也就大概一个小时,确认了地址偏移等等都是一致的.那这问题就更大了呀!

没思路,出去吃个饭再回来考虑一下。

继续!观察CS的跳动,它只在CLK跳动的这段时间会发生跳动,很像是引脚之间的串扰,但是不应该呀,十几兆而已。算了再去看看,好吧,接地线松了。浪费一个小时。怪我自己,总有一个国产芯片可能会和ST的cortex-M4系列有差别的先入为主的印象。接地线插紧,再测:

完美!

那接着写一段接收的代码:

一边抓一下读取时序:

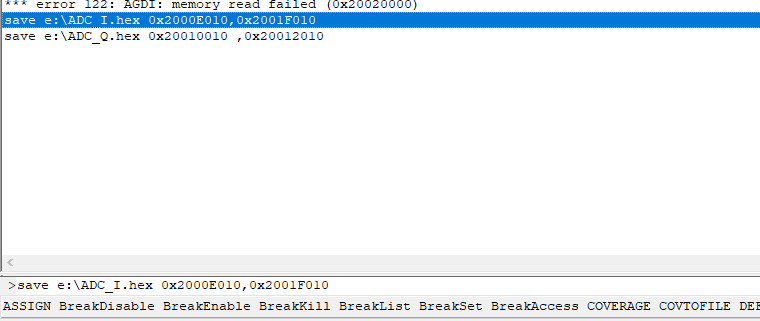

然后在debug模式下通过save指令保存内存中读到的ADC数据到本地

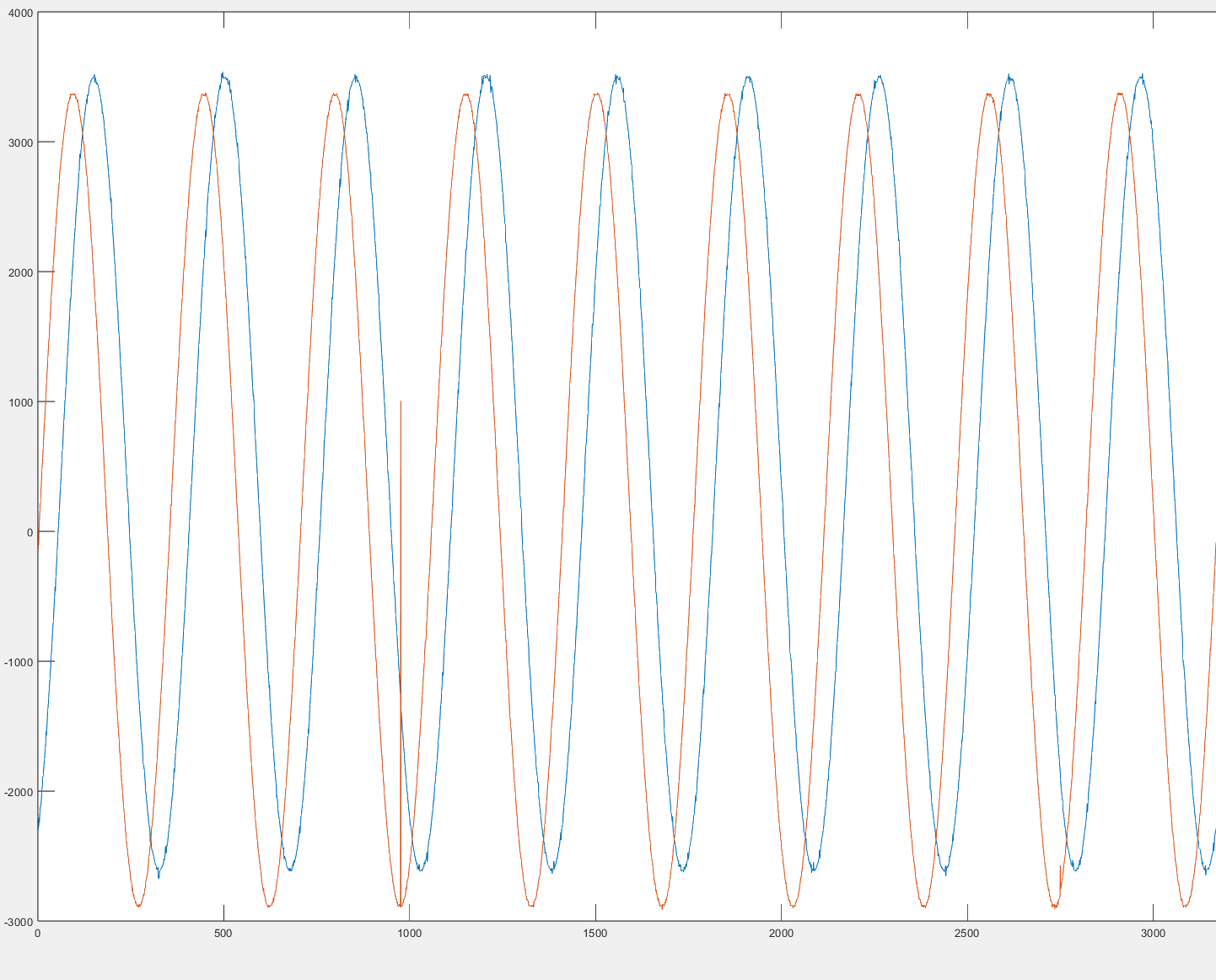

用matlab打印一下看一下读到的数据(DDS信号发生器产生的双路正弦波~1Khz、1Vpp、两者相位差为90°),最终结果如图:

可见读取成功,到这里就基本完事了。

补充说明:MDK保存的文件格式为HEX386格式,需要转为bin文件才能用matlab进行plot。

原作者:兆易创新GD32 MCU STY

/9

/9