首先来复习一个更加基础的概念:同步reset和异步reset。

同步reset(synchronous reset)是说,当reset信号为active的时候,寄存器在下一个时钟沿到来之后被复位,时钟沿到来之前寄存器还是保持其之前的值。

异步reset(asynchronous reset)是说,当reset信号为active的时候,寄存器立刻被复位,与时钟沿到来与否没有关系。

注意这里老李没有说reset信号为1的时候,而是说active,因为有的时候是为1能够使寄存器复位,这个时候我们说high active,而有的时候是0能够使寄存器复位,这个时候我们说low active。

同步reset和异步reset的区别算是数字芯片设计的入门知识点,一般第一轮面试就会考察。如果这个问题回答不好的话,那么你在面试官心里的印象一定是低于平均值的。老李在这里带大家简单复习一下,如果你对下面这些内容已经烂熟于心,就直接跳过吧。

首先同步reset和异步reset最主要的区别,从定义上就可以看得出,同步reset需要时钟,而异步reset不需要时钟。如果说你的模块需要在没有时钟的时候复位,那只有异步reset能够做到,这也是绝大多数芯片的上电复位信号(PowerOn Reset)以及一些PHY比如USB的内部需要异步reset的原因。

而在一些IP中,如果你可以等到时钟开始翻转之后再复位,时钟开始翻转之前内部即使没有复位也没有关系的话,那么就可以用同步reset。

其次一个差别,即同步reset信号在综合后,reset信号和其他的datapth信号一样,是一起算在两个寄存器之间的logic深度里,D寄存器本身是没有复位的pin的。而异步reset信号通常会综合出一个带有复位pin的D寄存器。

一般来说工艺厂家的standard cell library都会提供两种不同的寄存器,只要你的coding style正确,综合工具会选择适当的flop。

同步reset

上图是同步reset综合出来之后的netlist,可以看出reset_n使得两级寄存器之间的组合逻辑多加了一个AND门。

always_ff @(posedge clk) begin

对于异步reset,综合出来的flop自带reset pin,所以reset不参与中间的组合逻辑,如下图D2所示

异步reset

always_ff @(posedge clk or negedge reset_n) begin

从综合出来的逻辑可以看出,异步reset由于对寄存器之间的datapath没有贡献,所以在timing上面能够略微比同步reset好一些,特别是reset信号作为一个负载很大的信号,如果reset tree做得不好可能使得reset path的combo delay变得很大,反而限制了performance的提高。所以在对logic depth抠得很细的设计中,可以使用异步reset来避免引入更多的combo delay。

但是同步reset还有一个优势,由于reset信号会最终起作用在寄存器的D输入端,那么通过reset的组合逻辑都会被STA所约束,也就是说reset信号和其他datapath的信号一起要满足寄存器的setup time, hold time, min pulse等一系列check,在timing close的情况下我们可以拍着胸脯保证:寄存器不会因为reset信号的变化产生metastable。

(所以同步reset信号的跨时钟域咱们就不废话了)可以对于异步reset就没有这么简单了,既然是异步,那么就是在任何时候都可能变化。现在STA之所以叫static timing analysis,是因为工具是静态分析电路的:给定一个时钟沿的起始点,然后后面每一级的delay都是纯粹的累加,最后再和required time来进行比较,比required time早到,就是满足timing,晚到就是violation。

可是如果一个信号什么时候来都无法确定,那么就无法判断这个信号的datapath上最后能否满足required time。换句话说,纯粹的异步reset在当前的STA check中是没有办法检查的。

那么怎么办呢?难道对于异步reset信号就听之任之放任不管吗?当然不是,我们做IC的当然要对每一个细节都要研究清楚。我们这里要分两种情况:1. reset assertion; 2. reset release。老李直接上结论:

如果使用异步reset,reset assertion是异步的,但是reset release一定要和时钟同步!

因为对于reset assertion,reset active之后flop的值是稳定在reset value的,只要reset继续active,来多少个clock,其他datapath上的信号怎么变,flop的值都不会变化,所以reset 在什么时候assertion都没关系。

但是reset release就不一样了,一旦reset从active变为in-active,那么flop之后的值就得取决于其他信号输入和时钟沿的关系了,所以对于reset de-assertion,在STA里有两个专门的参数来check,叫做recovery time和removal time。

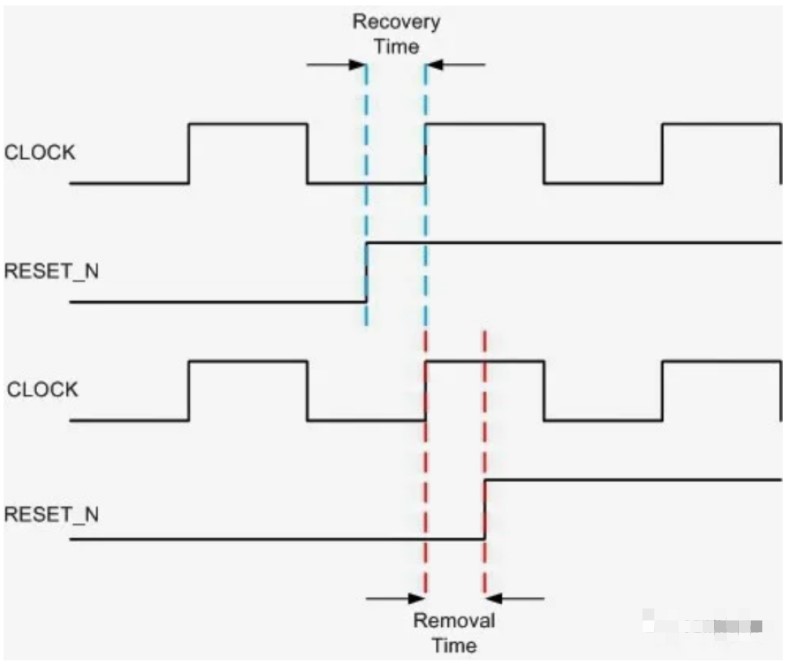

recovery time指的是reset release之后要求距离下一个时钟沿的最小间隔,可以类比于其他信号datapth上的setup time。

removal time指的是reset release之后要求距离上一个时钟沿的最小间隔,可以类比于其他信号datapth上的hold time。

换句话说,reset release必须在recovery time和removal time加起来这个窗口之外,这样才能保证寄存器不会产生metastable。

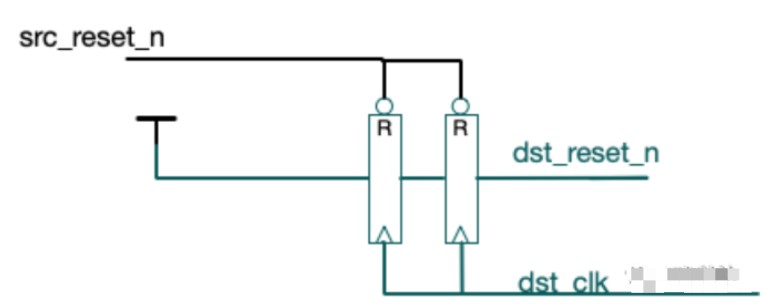

好,下面的问题就变成了,我们如何设计可以使得异步reset信号是异步assertion, 同步release呢? 终于要引出我们今天的主题,将一个异步的reset信号同步到一个时钟域,并且还要保证assertion是异步的,但是release是同步于这个时钟的,我们把这样的电路叫做reset synchronizer, 如下图所示。

可以看到,当src_reset_n assert时,两个flop被异步reset,它们的Q会经过reset-to-q的延时之后立刻发生变化,使得dst_reset_n assert。

而当src_reset_n release后,dst_reset_n并不是立刻发生变化,而是要等待dst_clk的时钟沿,并且打两拍之后才能将1传递到dst_reset_n。因为dst_reset_n是来自于flop的Q,而Q是经过dst_clk上的同步信号。那为什么要两级flop,还是为了减小产生metastable的概率。

注意,对于一个使用异步reset的模块,reset synchronizer是必须的,但是也不要对一个异步reset信号进行多次reset synchronizer,否则同样的会产生coherency的问题。

异步reset在设计中还有一些其他需要注意的点,特别是在DFT中要特殊对待,还有异步reset在STA中timing constraint要如何正确设置等等。老李以后抽时间再和大家聊。

原作者:硅谷老李

/6

/6