继 Cortex-A710之后, 作为最新的大内核,A715 支持与 ARMv9.0 ISA 大致相同的几项增强功能。更关键的是,A715的所有Exception Level都是仅支持AArch64(完全放弃了 32 位支持)。

A715 的设计原则与之前的大核心相似:以更高的比率提高性能,而不是影响功率和面积。在这次迭代中,性能重点放在了整体改进上,而没有显着拓宽pipeline 或extending its depth。最后,Arm 工程师引入了受早期 Cortex-X 设计启发的有针对性的改进,例如分支预测器和预取增强功能。

功耗性能

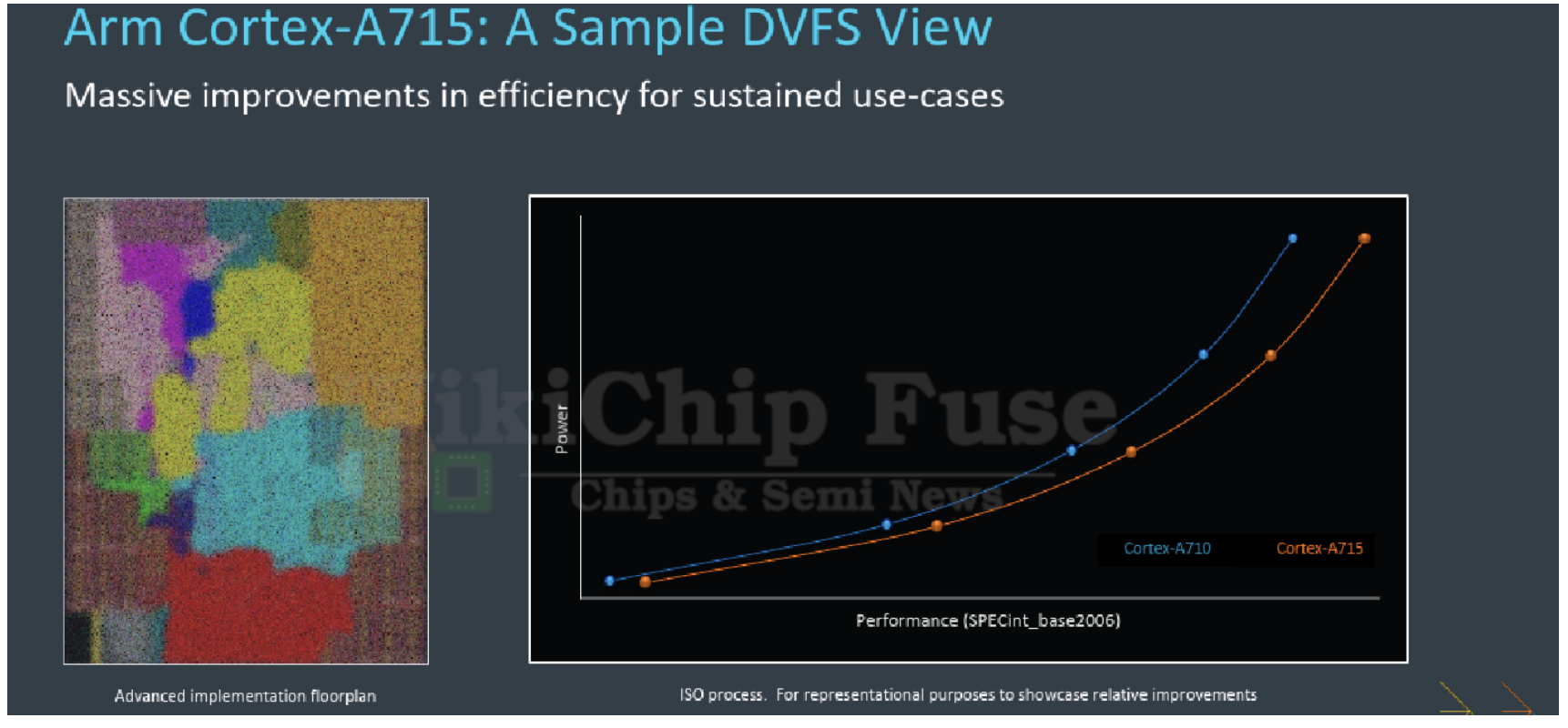

与 Cortex-A710 相比,据说新的 A715 在相同功耗情况下可提供 5% 的性能提升。同样,在与 A710 相同的性能水平下,A715 的功耗降低了 20%。两种比较都是在 iso-process 中完成的。换句话说,Arm 表示新的 Cortex-A715 可以提供与第一代 Cortex-X1 内核相同的性能。X1是Arm 在 2020 年的超大核处理器。

总体而言,很明显,在这一代中,降低功耗更为重要——尤其是在持续使用案例中。这个核心有点不寻常的是,性能提升似乎有点平淡无奇。Arm 在大幅提升性能和大幅降低功耗(以低得多的性能提升)之间切换并非闻所未闻,但在这种特殊情况下,鉴于他们 2020 年 Arm TechCon公告承诺单核性能比 Cortex-A78 高出 30%。与 A78 相比,就 IPC 而言,我们在 15% 左右。目前尚不清楚为什么差异如此之大。尽管如此,下面显示的 DVFS 曲线显示了在整个性能范围内的良好能效增益。

微架构

在一定时间里,技术背后发生了相当大的变化。绝大多数变化发生在内存子系统中。

Fetch

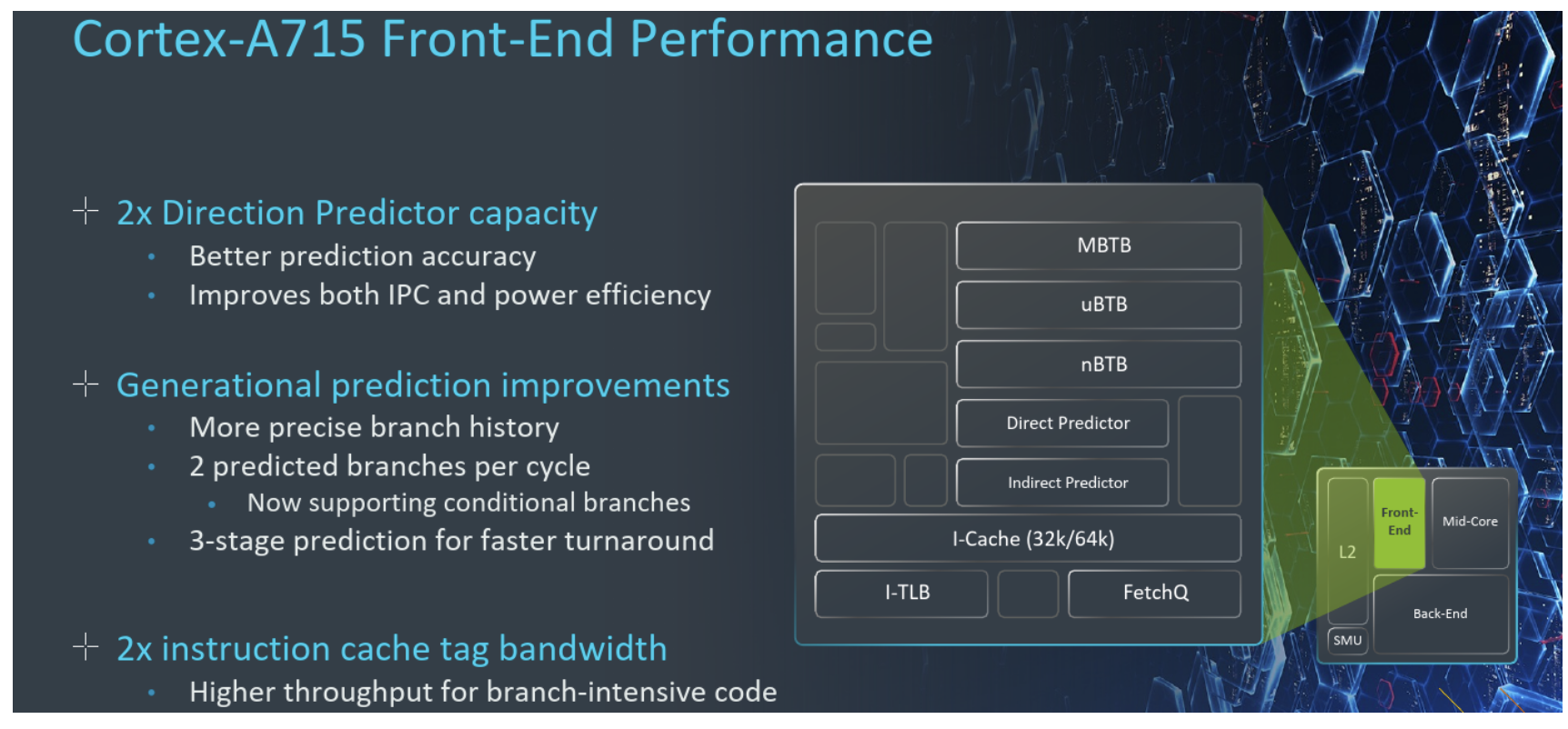

Arm 花费了大量时间来完善他们的预取器和分支预测器。这是他们可以保持相对较小的缓存大小的部分原因。在这次迭代中,他们将方向预测器的容量翻了一番,同时提高了其准确性。

在上一代 A710 中,内核能够在每个周期预测两个无条件分支。现在,在 A710 中,此功能进一步扩展为支持条件分支。换句话说,虽然 A710 可以执行一个无条件条件分支并且只执行一个条件分支,但它现在可以执行两个。

A715 的另一项改进是引入了 3 阶段预测方案以实现快速周转。以前,Arm 具有快速的 L0 0 周期预测和较慢的 2 周期预测结构,而在 A715 中,Arm 将其分解为三个阶段,采用新的 1 周期周转中间结构,从而减少了获得预测的延迟。

随着更高容量的分支预测器产生更高的分支请求带宽,可能会遇到更多获取两个单独指令流的实例。为了适应这一点,A715 现在支持更高的指令高速缓存查找带宽,最高可达标签/周期的两倍。

仅支持64位

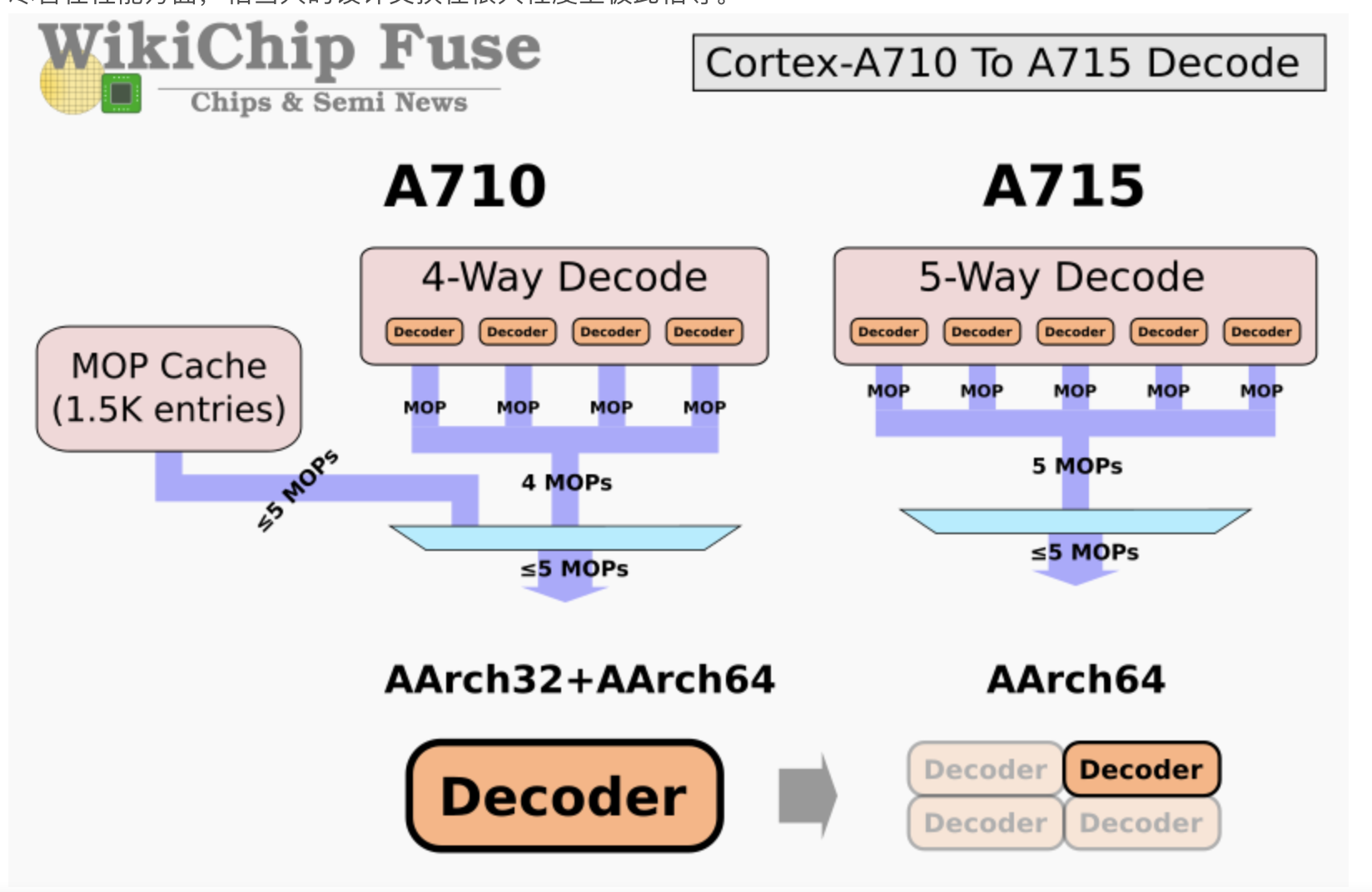

新的 Cortex-A715 是纯 AArch64 实现,这意味着设计团队可以摆脱 32 位架构带来的各种架构怪癖和低效率。Arm 表示,由于 AArch64 更正常的特性,新的解码器不仅可以更有效地设计和优化,而且它们的体积也要小得多。

事实上,Arm 表示,新的解码器实际上“比 Cortex-A710 中的解码器小 4 倍,并具有与之匹配的节能效果”,这非常了不起。

随着那些新的解码器发生了很多变化。首先,Arm采取了指令融合机制,直接移到指令缓存中。以前,A710 专门在 MOP 缓存中执行此操作。

这意味着,现在,所有应用程序都可以在提取级别利用融合指令(即受益于更高的有效指令吞吐量)。其次,以前,一些指令只能由特定的解码器处理。现在所有解码器都可以处理所有操作。

由于 AArch64 解码器尺寸更小,Arm 添加了第 5 个解码通道。换句话说,新的 A715 获取/解码带宽现在与 A710 MOP 带宽匹配,而指令缓存获得了 MOP 融合功能。

通过移动 MOP 缓存的许多优点以及新添加的解码通道,Arm 表示它能够在没有 MOP 缓存的情况下实现类似的性能。出于这个原因,它被删除了。移除缓存还提供了一些面积和功率增益,尽管在性能方面,相当大的设计交换在很大程度上彼此相等。

内存子系统

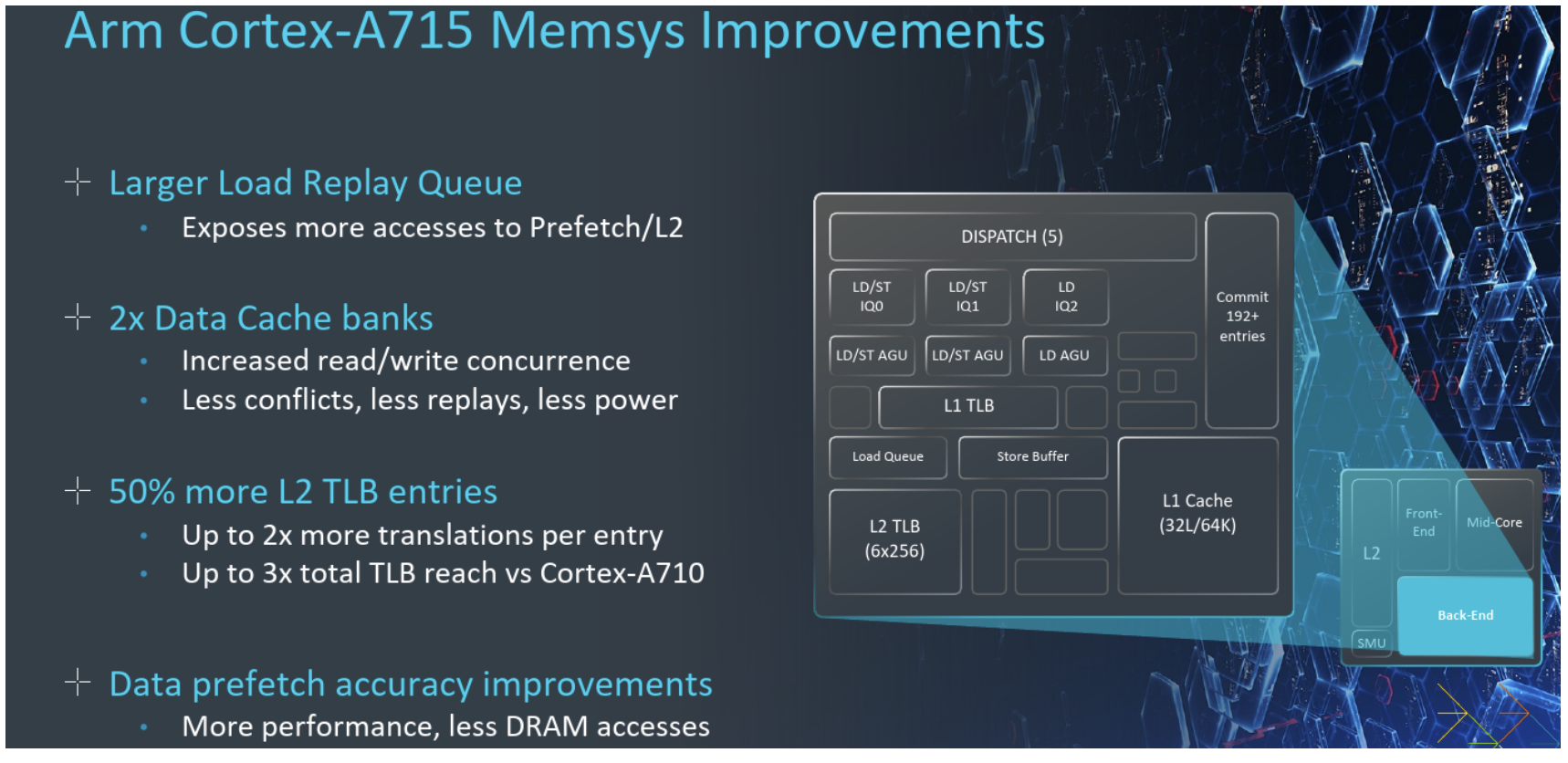

在内存子系统方面,Cortex-A715 增加了负载回复队列。这是持有已发布的加载访问权限的结构。Arm 将数据缓存组的数量增加了一倍。随着更多的银行,现在有更多的读/写端口,允许更多的数据访问并发。

A715 的最后一个变化是现在 L2 TLB 条目增加了 50%,并且 Arm 表示每个条目现在可以存储双倍的虚拟地址 (VA),这意味着在正确的条件下可以实现高达 3 倍有效的 TLB 覆盖 Cortex-A710。

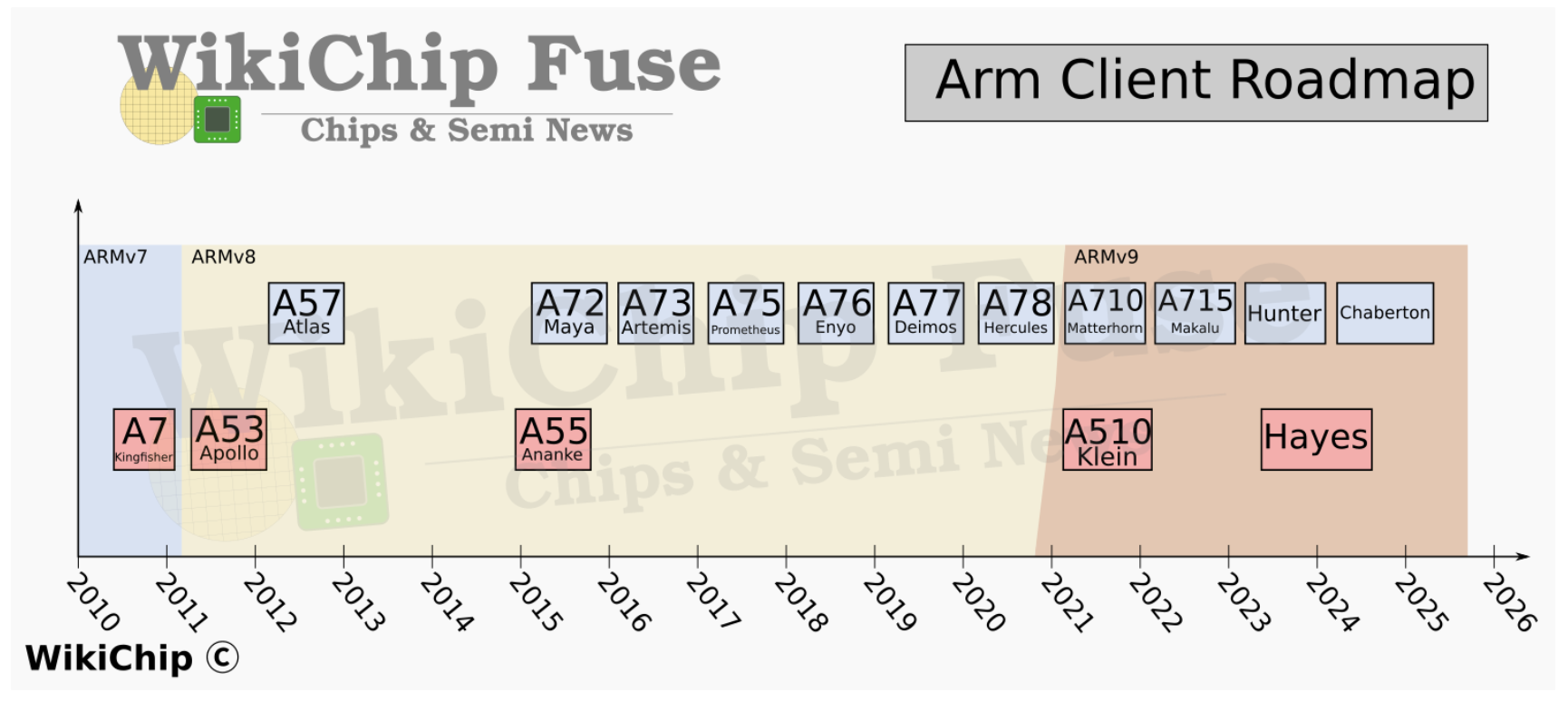

展望未来,Arm 披露了这两年的两个新核心——Hunter 和 Chaberton。Neoverse Demeter 和 Cortex Hunter & Hayes 的软件支持于去年年底开始推出。

原作者: 代码改变世界ctw

/6

/6