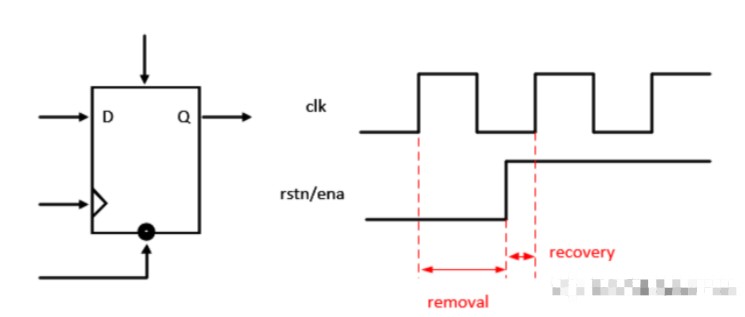

让我们从触发器开始,所有触发器都有一个围绕活动时钟沿的建立(setup time)和保持窗口(hold time),在此期间数据不得更改。如果该窗口中的数据实际发生了变化,则触发器的输出将进入不确定状态,这既不是逻辑 0 也不是逻辑 1。在定义的恢复时间(recovery time)后,触发器输出将恢复为逻辑 0 或逻辑 1。

每个系列器件的建立和保持时间以及恢复时间都是独一无二的,这些信息通常在数据表或应用说明中定义。一般来说,当我们设计 FPGA 满足时序约束时,我们不必过于担心它们,因为 Vivado 会尽量满足约束中定义的性能。

然而,当我们有异步信号进入到 FPGA 或多个彼此异步的时钟域时,我们就需要仔细考虑设计,以确保我们不会违反建立和保持时间并导致亚稳态。当然,无论哪种情况,我们都无法阻止亚稳态事件的发生,但我们可以确保我们的设计不会因为亚稳态事件的发生而出现不正确的数据。

当然,很明显的一个情况就是输入信号与内部时钟是异步的,在同一个时钟域中的构成还不是很清楚。我们可以使用一些简单的规则;如果时钟是公共时钟的整数除法,我们就在同一个时钟域中。如果时钟是非整数除法,它们不在同一个时钟域中,或者来自不同的源(即使它们具有相同的时钟频率)

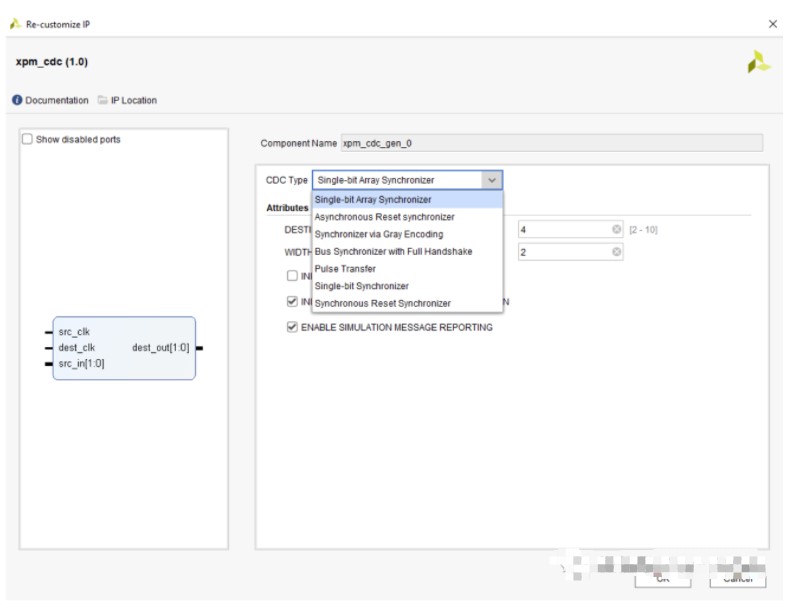

在将信号同步到 FPGA 或不同的时钟域时,有多种设计可供选择。在xilinx fpga中,最好的方法是使用xilinx参数化宏,创建这些宏的目的是解决 CDC / Synchronization问题。XPM 提供了一个范围宏,包括

- 单静态同步器(Single Static Synchroniser)——经典的单比特触发器同步器

- 脉冲数据同步器(Pulse Data Synchroniser)——将脉冲从一个域传输到下一个域

- 数据总线(Data Bus)——多路复用器、FIFO、握手和基于格雷码的传输

在 Vivado 中,我们现在很容易地在 IP Integrator 中实现 XPM 结构,以使 CDC crossing可见。

需要仔细考虑使用哪种结构,例如,不要尝试使用单个位同步器同步多个数据位,因为不能保证传输的数据对齐,从而导致数据损坏。还需要注意recombination,这是两个或多个静态信号跨越时钟域并在逻辑功能中重组的地方。由于亚稳态恢复,同步器中的延迟会导致下游逻辑受到影响。

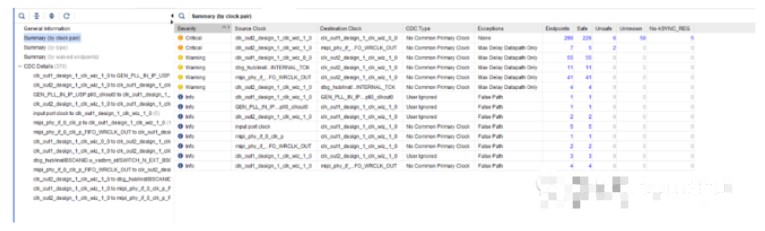

尽管我们在设计中尽最大努力减轻 CDC,但我们是人类,我们也会犯错,因此我们可以使用内置的 Vivado 选项来报告设计中出现的 CDC。

综合完成后,我们可以运行 CDC 报告,无需等待 place 和 root 完成。

在 TCL 控制台中运行命令 report_cdc – 有很多选项可用于写出文件、分析特定路径或创建豁免。

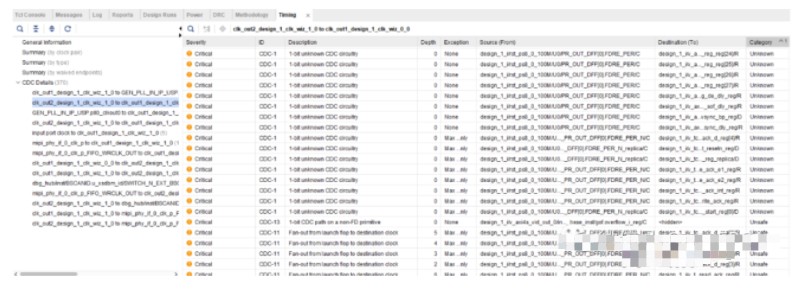

这将显示设计中的所有时钟域交叉以及是否存在任何不安全或未知的交叉。在上面的示例中,可以看到有 6 个不安全和几个未知。如果我们使用选项 -details 运行命令,我们将看到报告的所有路径。单击不安全或未知的路径将打开关注的路径以供我们检查。

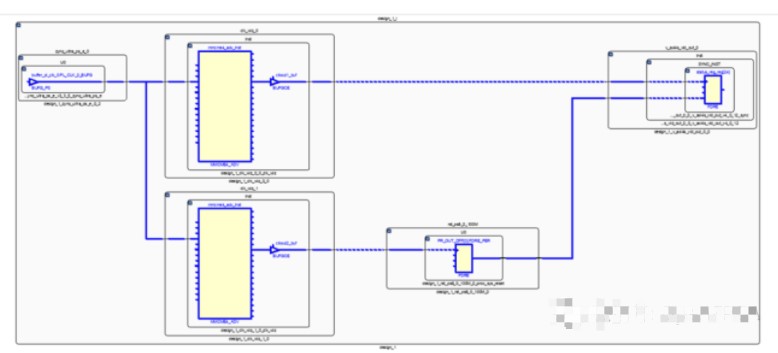

选择路径后,我们可以打开我们关注路径的示意图查看器。在这种情况下的问题是复位是由不同的时钟生成的。

知道这一点后,我们可以通过更新设计,例如:纠正错误、插入必要的同步结构或纠正约束以更新路径来纠正问题。

原作者:碎碎思

|  /9

/9