SpinalHDL中Bundle与SystemVerilog中的packed struct很像,在某些场景下,与普通数据类型之间的连接赋值可以通过asBits,assignFromBits来实现。

》Bundle—>Bits

在SpinalHDL中,无论是哪种数据类型都是可以转换成Bits类型,我们扩展Bundle类型定义的复杂数据类型也不例外,可以通过asBits函数将自定义的数据类型转换成Bits数据类型。以下面所定义的数据类型为例:

case class port() extends Bundle with IMasterSlave {

val data0=UInt(8 bits)

val data1=Bits(8 bits)

val last=Bool()

override def asMaster(): Unit = {

out(data0,data1,last)

}

}

我们完全可以通过调用asBits函数将其转换成Bits类型:

val portInst=port()

val data=portInst.asBits

生成的Verilog代码将对应:

assign data = {portInst_last,{portInst_data1,portInst_data0}};

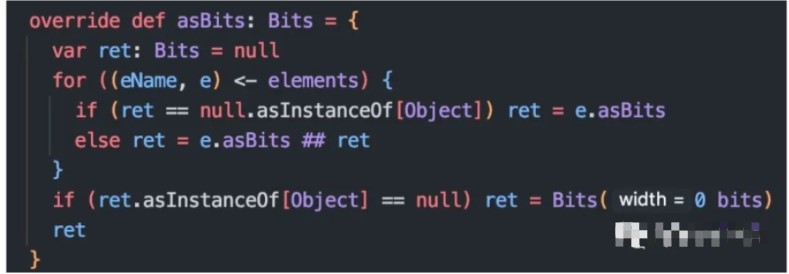

这里与SystemVerilog中的packed struct略不相同的是,在SystemVerilog中packed struct中先定义的元素排在最高位,而在SpinalHDL Bundle中先定义的元素在转换成Bits时则是排在最低位,这与asBits函数的实现有关:

》Bits—>Bundle

Bits—>Bundle的转换可以通过assignFromBits来实现。在SpinalHDL中针对Bundle类型,提供了三种不同的实现:

-

assignFromBits(bits:Bits)—将bits整个赋值给Bundle,当bits位宽大于Bundle定义的位宽时,高位将抹去。

-

assignFromBits(bits:Bits,hi:Int,lo:Int)—将bits整个赋值给Bundle对应Bits的(hi down to lo),多余的位将抹去

-

assignFromBits(bits:Bits,offset:Int,bitCount:BitCount)—等价于assignFromBits(bits,offset:Int+bitCount.value,offset)

在和已有的一些Verilog/SystemVerilog接口进行对接时这些API还是很有作用的,可以方便的实现接口转换以实现功能。

像下面的用法是等价的:

val dataIn=Bits(17 bits)

val portInst=port()

portInst.assignFromBits(dataIn)

等价于:

portInst.data0:=dataIn(7 downto 0)

portInst.data1:=dataIn(15 downto 8)

portInst.last:=dataIn(16)

val portData=Bits(16 bits)

val portLast=Bits(16 bits)

val portInst=port()

portInst.assignFromBits(portData,15,0)

portInst.last:=portLast

等价于

portInst.data0:=portData(7 downto 0)

portInst.data1:=portData(15 downto 8)

portInst.last:=portLast

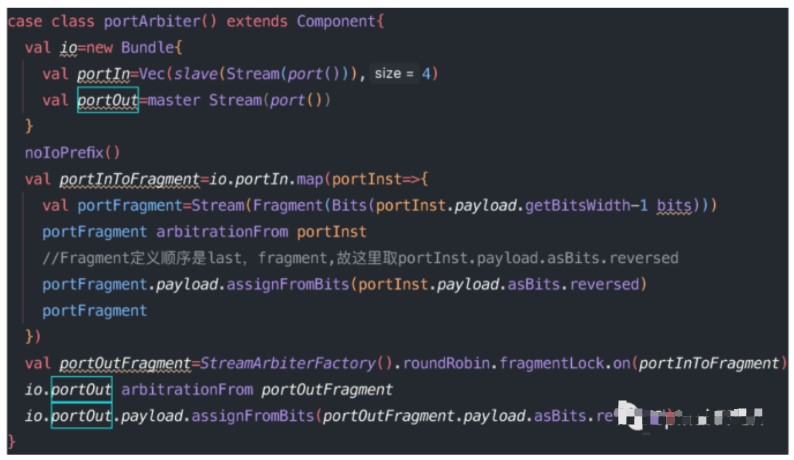

下面的这个例子展示了如果通过这些方法调用SpinalHDL中的StreamArbiter来实现两个port端口FragmentLock RR调度:

原作者:玉骐

|  /6

/6