完善资料让更多小伙伴认识你,还能领取20积分哦, 立即完善>

3天内不再提示

完善资料让更多小伙伴认识你,还能领取20积分哦, 立即完善>

|

超强PCB布线设计经验谈附原理图(5) 要解决信号完整性问题,最好有多个工具分析系统性能。如果在信号路径中有一个A/D转换器,那么当评估电路性能时,很容易发现三个基本问题:所有这三种方法都评估转换过程,以及转换过程与布线及电路其它部分的交互作用。三个关注的方面涉及到频域分析、时域分析和直流分析技术的使用。本文将探讨如何使用这些工具来确定与电路布线有关问题的根源。我们将研究如何决定找什么;到哪里找;如何通过测试检验问题;以及如何解决发现的问题等。

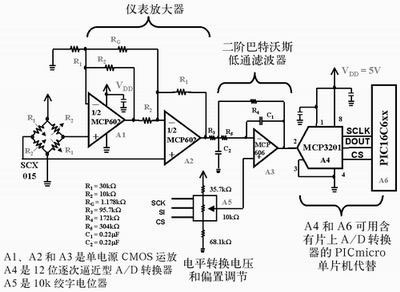

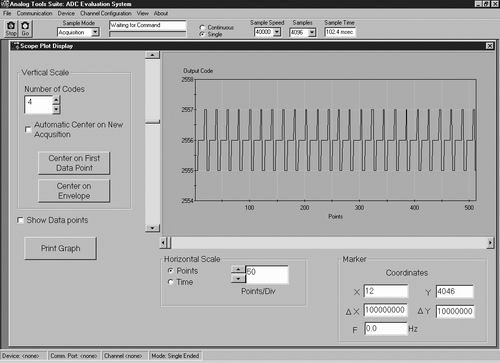

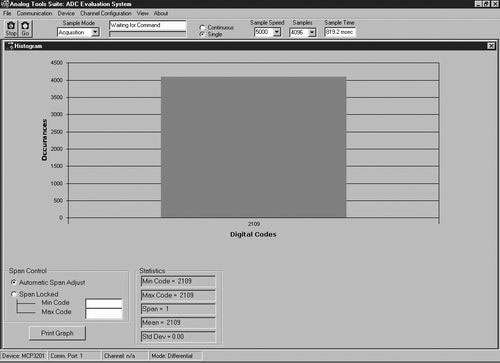

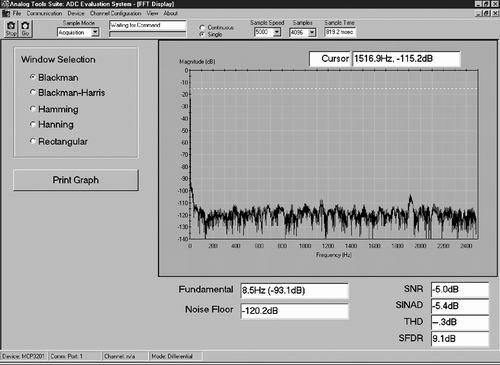

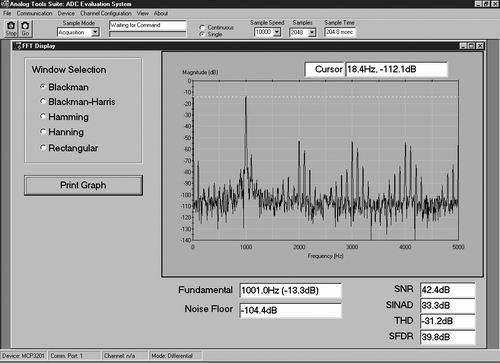

图1 SCX015压力传感器输出端的电压由仪表放大器(A1和A2)放大。在仪表放大器之后,添加了一个低通滤波器 (A3),以消除来自12位A/D转换器转换的混叠噪声  图2 来自于12位A/D转换器MCP3201的数据的时域表示,产生了有趣的周期信号。此信号源可追溯到电源。  图3 电源噪声充分降低后,MCP3201的输出码一直是一个码,2108。 本文要论述的电路如图1所示。 电源噪声 电路应用中的常见干扰源来自电源,这种干扰信号通常通过有源器件的电源引脚引入。例如,图1中A/D转换器输出的时序图如图2所示。在此图中,A/D转换器的采样速度是40ksps,进行了4096次采样。 在此例中,仪表放大器、参考电压源和A/D转换器上没有加旁路电容。另外,电路的输入都是以一个低噪声、2.5V的直流电压源作为基准。 对电路的深入研究表明,时序图上看到的噪声源来自于开关电源。电路中添加了旁路电容和扼流环。电源上加了一个10mF的电容,并且在尽可能靠近有源元件的电源引脚旁放置了三个0.1mF的电容。在产生的新时序图上可以看到,产生了稳定的直流输出,图3所示的柱状图可验证这一点。数据显示,电路的这些更改消除了来自电路信号路径的噪声源。 造成干扰的外部时钟 其它系统噪声源可能来自时钟源或电路中的数字开关。如果这种噪声与转换过程有关,它不会作为转换过程中的干扰出现。但是,如果这种噪声与转换过程无关,采用FFT(快速傅立叶变换)分析,可以很容易发现这种噪声。  图4 耦合到模拟走线的数字噪声有时被误解为宽带噪声。FFT图可以很容易识别这种所谓 “噪声”的频率,因此可识别出噪声源。  图5 放大器轻微过激励,会使信号产生失真。通过这种转换的FFT图,可以很快发现信号的失真。 时钟信号干扰的示例可参见图4所示的FFT图。此图使用了图1所示的电路,并添加了旁路电容。在图4所示的FFT图中看到的激励,由电路板上的19.84MHz时钟信号产生。在此例中,布线时几乎没有考虑走线之间的耦合作用,在FFT图中可以看到忽略此细节的结果。 这个问题可以通过修改布线来解决,将高阻抗模拟走线远离数字开关走线;或者在模拟信号路径中,在A/D转换器之前加抗混叠滤波器。走线之间的随机耦合在某种程度上更难以发现,在这种情况下,时域分析可能比较有效。 放大器使用不恰当 回到图1所示的电路,在仪表放大器的正相输入端施加一个1kHz的交流信号。此信号不是压力传感的特性,但是可以采用这个示例来说明模拟信号路径中器件的影响。 图5所示的FFT图显示了施加上述条件后的电路性能。注意基波看起来有失真,许多谐波也有同样的失真。失真是由于使放大器轻微过激励引起的。解决此问题的方法是降低放大器增益。 结语 解决信号完整性问题可能会花费很多时间,尤其是当工程师没有工具来解决棘手的问题时。在“窍门箱”中有三种最佳的分析工具:频域分析工具(FFT)、时域分析工具(示波器照片)和直流分析工具(柱状图)。工程师可以用这些工具来识别电源噪声、外部时钟源和过激励放大器失真。 |

|

相关推荐

11 个讨论

|

|

|

顶

|

|

|

|

|

|

|

|

|

版主很牛啊,向版主学习。

|

|

|

|

|

|

|

|

|

谢谢楼主 |

|

|

|

|

|

|

|

|

学习学习

|

|

|

|

|

|

|

|

|

学习学习

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

【Altium小课专题 第107篇】原理图中批量修改位号或网络标号属性值字体的大小?

12610 浏览 1 评论

【Altium小课专题 第103篇】原理图同一网络颜色进行了设置,但是无法进行显示是什么原因?

9214 浏览 0 评论

【Altium小课专题 第094篇】如何从PCB中直接生成PCB库呢?

9117 浏览 0 评论

【Altium小课专题 第071篇】什么是层次式电路设计?它的优点有哪些?

7879 浏览 0 评论

【Altium小课专题 第068篇】原理图的模板如何进行编辑信息更改?

14711 浏览 0 评论

/9

/9

小黑屋| 手机版| Archiver| 电子发烧友 ( 湘ICP备2023018690号 )

GMT+8, 2025-12-14 12:22 , Processed in 1.032343 second(s), Total 77, Slave 64 queries .

Powered by 电子发烧友网

© 2015 bbs.elecfans.com

关注我们的微信

下载发烧友APP

电子发烧友观察

版权所有 © 湖南华秋数字科技有限公司

电子发烧友 (电路图) 湘公网安备 43011202000918 号 电信与信息服务业务经营许可证:合字B2-20210191

淘帖

淘帖 33747

33747