完善资料让更多小伙伴认识你,还能领取20积分哦, 立即完善>

3天内不再提示

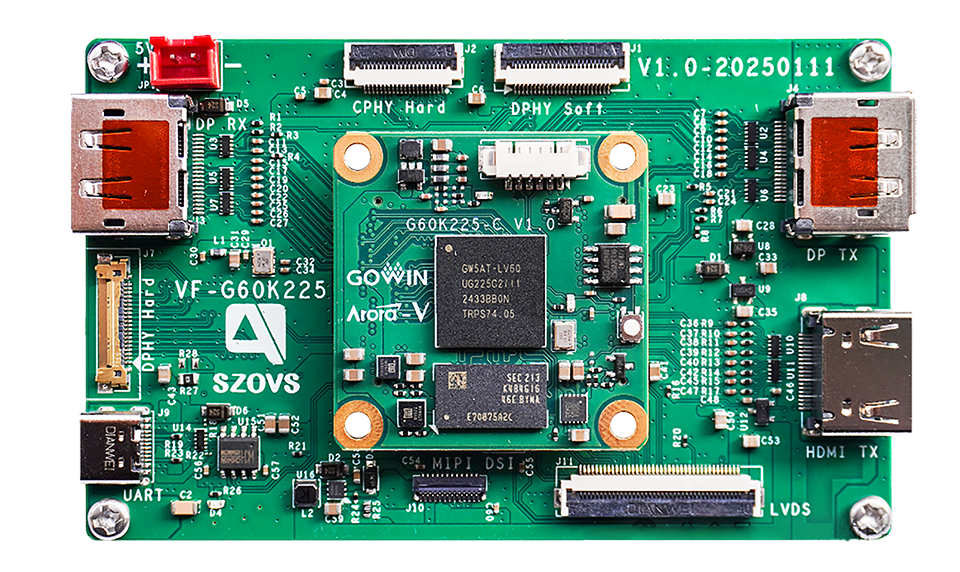

DK VIDEO GW5AT-LV60UG225 V1.0

一、开发板硬件介绍

(一)高云GW5AT-LV60主芯片介绍

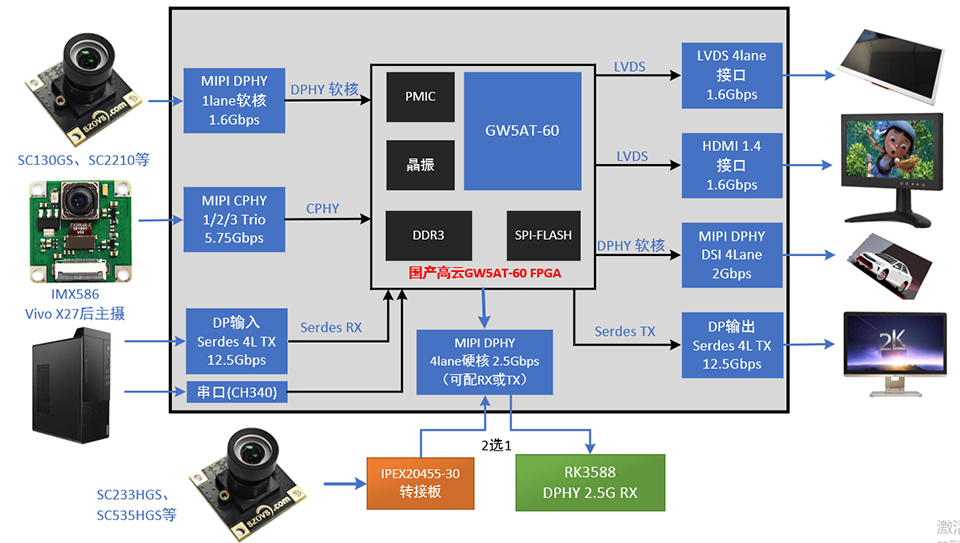

高云的Arora Ⅴ系列的GW5AT-LV60 FPGA ,是高云半导体晨熙家族第5代产品,其内部资源丰富,具有全新构架的高性能 DSP ,高速 LVDS 接口以及丰富的 BSRAM 存储器资源,同时集成自主研发的 DDR3(1333Mbps),MIPI DPHY 硬核(2.5Gbps),MIPI CPHY硬核(5.75Gbps),以及支持多种协议的12.5Gbps Serdes收发器等,提供多种管脚封装形式,适用于低功耗、高性能的视频图像应用开发领域。

产品型号:高云GW5AT-LV60UG225

特性:

22nm SRAM 工艺高性能FPGA

60K Luts 资源

集成MIPI CPHY硬核(RX,TX 可配置,速率达到5.75Gbps)

集成MIPI DPHY硬核(RX,TX 可配置,速率达到2.5Gbps)

集成4路高速SerDes (速率12.5Gbps)

支持eDP、DP、SLVS-EC、SDI、USB 3.0等多款协议

支持PCIe 2.0硬核(支持x1,x2,x3,x4通道,支持End Point模式)

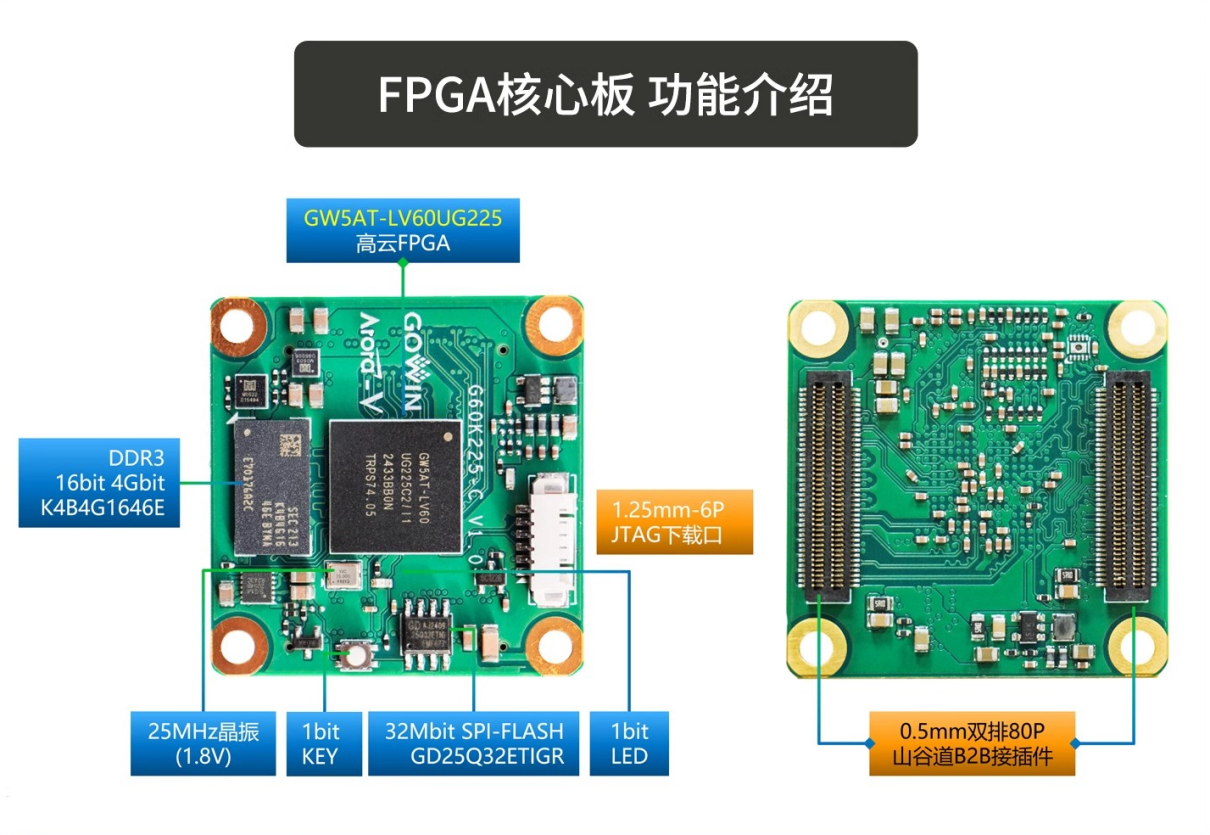

(二)高云GW5AT-LV60 核心板功能介绍

|

参数 |

描述 |

|

FPGA型号 |

高云GW5AT-LV60UG225 |

|

DDR3存储 |

DDR3 16bit 4Gbit:K4B4G1646E |

|

PCBA尺寸 |

长38mm * 宽38mm |

|

PCB工艺 |

6层 1.6mm 沉金 绿色 |

|

板载FLASH |

32Mbit SPI FLASH :GD25Q32ETIGR |

|

板载功能 |

• 1个LED灯 • 1个硬复位按键 |

|

其他接口 |

板载1.25mm-6P JTAG下载口 |

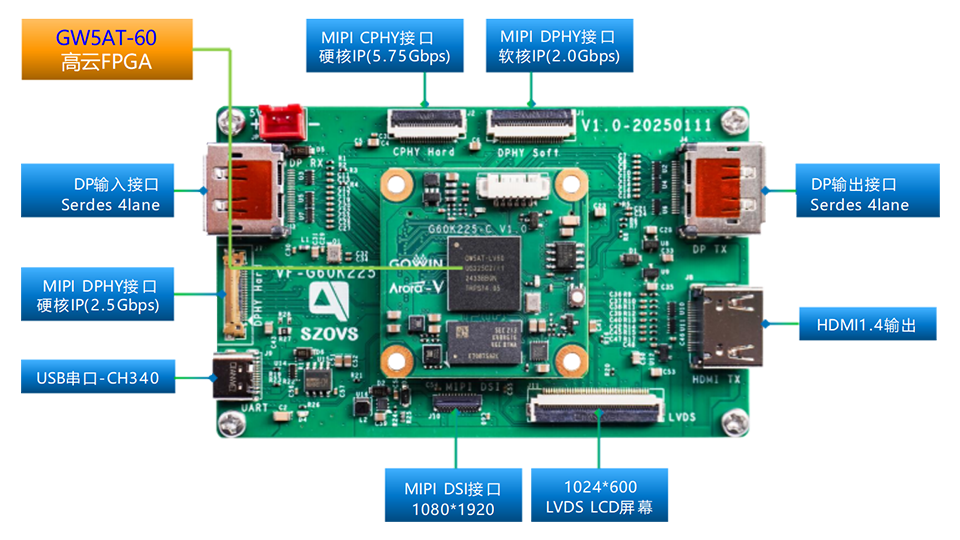

(三)高云GW5AT-LV60 开发板功能介绍

|

参数 |

描述 |

|

FPGA型号 |

高云GW5AT-LV60UG225 |

|

FPGA资源 |

• 60K逻辑单元,118个DSP • 2.0Gbps MIPI DPHY软核 • 2.5Gbps MIPI DPHY硬核(RX/TX) • 5.75Gbps MIPIP CPHY硬核 • 12.5Gbps Serdes RX+TX |

|

DDR3存储 |

DDR3 16bit 4Gbit:K4B4G1646E |

|

PCBA尺寸 |

长100mm * 宽60mm |

|

PCB工艺 |

6层 1.6mm 沉金 绿色 |

|

底板外设 |

1)1个USB串口 2)1路HDMI 1.4显示接口(FPGA驱动) 3)1路LVDS LCD接口(1024*600显示屏) 4)DP输入输出接口(4lane Serdes TX/RX) 5)1个MIPI DPHY 硬核/软核接口 6)1个MIPI CPHY硬核接口 7)1个MIPI_DSI_TX接口 8)PH2.0外部辅助5V/2A供电接口

|

(四)高云GW5AT-LV60 图像解决方案

|

开发套件 |

数量 |

备注 |

|

GW5AT-LV60 FPGA开发板(核心板+底板) |

1 |

主办方提供 |

|

思特威 SC2210 200万摄像头(MIPI卷帘彩色) |

1 |

根据项目情况主办方选择提供 |

|

思特威 SC130GS 130万摄像头(MIPI全局黑白/彩色) |

1 |

根据项目情况主办方选择提供 |

|

索尼IMX586 4800万 摄像头(CPHY卷帘彩色) |

1 |

根据项目情况主办方选择提供 |

|

1080*1920 MIPI液晶屏 |

1 |

根据项目情况主办方选择提供 |

|

1024*600 LVDS液晶屏 |

1 |

根据项目情况主办方选择提供 |

|

高云FPGA下载器 |

1 |

提供 |

(五)GW5AT-LV60 开发板配套资料

|

资料 |

数量 |

备注 |

|

开发板用户手册 |

1 |

主办方提供 |

|

FPGA原理图库 |

1 |

主办方提供 |

|

数据手册 |

1 |

主办方提供 |

详情点击:DK_VIDEO_GW5AT-LV60UG225_V1.0 - 广东高云半导体科技股份有限公司

二、开发板试用规则

(一)试用流程:

1. 试用申请(1个月):点击免费申请按钮即可报名。请认真填写申请理由,提交有创意的试用计划,大致的实现过程和应用场景,展示丰富的过往项目经验和网络影响力。

2. 试用名单审核及公布(1周):高云半导体(Gowin)官方会根据申请者填写的试用计划和论坛活跃度两个维度进行筛选。筛选完毕后将在活动页公布名单。

3. 试用通知:名单公布后工作人员将以短信 / 电话/ 邮件等方式通知申请成功者。

4. 产品寄送:电子发烧友工作人员联系到试用者,双方确认规则后,将产品快递给试用者,具体到货时间以实际物流为准。

5. 用户试用(2个月)&上传试用报告(4篇及以上):收到开发板后,需按要求定期上传评测报告(图文 / 视频)至电子发烧友社区可编程逻辑器件/FPGA论坛,试用报告要求100%原创,抄袭会被封杀哦。

6. 产品回收:请收到开发板的用户在规定时间内完成试用报告并上传至电子发烧友论坛,如发现未完成试用报告上传发布,将会要求您将开发板全套退回。

7. 优质试用帖评选(1周):将从试用报告的可读性、专业度、逻辑性、阅读量等方向综合评选。

注:试用开发板仅作为活动使用,“非赠送”,活动结束后试用者须退回板卡

(二)试用名单评审参考:项目创新性、开发难度、可落地性、市场前景等

(三)试用报告要求如下:

1. 试用报告需涵盖:项目概述、软件调试、硬件接入、功能演示、视频演示、关键代码分析、经验分享等等。

试用者完成4篇及以上评测报告方有资格参与奖项评选(每篇500字+3图以上,开箱报告也算做为一篇内容报告,但要求内容和步骤详尽),完成4篇及以上高质量试用报告方有入选“优质评测试用者”的资格。

(1)文字:描述字数500字以上,确保行文逻辑的严谨、准确和流畅,重点评测环节要有必要的文字说明进行阐述,以确保读者可以了解评测过程。

(2)图片:评测报告的配图需确保清晰,避免出现影响观感的“反光”、“曝光过度”和“暗部细节不清晰”等情况的发生。

2. 报告形式:标题格式示例:【高云GW5AT-LV60 开发套件试用体验】+自拟标题。

3. 试用周期内如无特殊原因,要求两周上传一篇试用报告至电子发烧友社区。

4. 如未按要求上传相应内容,开发板套件将被收回,并取消活动参与资格。

(四)试用时间安排

试用申请:3月20日-4月20日

试用审核:4月21日-4月27日

开发板邮寄:4月28日-4月30日

开发板试用/报告:5月1日-6月30日

优质试用评选:7月1日-7月7日

公布结果:7月8日

(五)优质评测试用者评选(5名)

l 最佳评测奖1名 —— 开发板赠送或500元京东E卡(开发板、500元京东卡二选一),试用报告质量高,数量4篇及以上

l 优秀评测奖3名 —— 200元京东E卡,试用报告质量一般,数量4篇及以上(需回收开发板)

l 完成评测奖4名 —— 100元京东E卡,试用报告4篇(需回收开发板)

注:试用获奖者的优质评测报告,高云半导体有权转载至官方媒体平台(会标注原作者)

(六)评选结果(以下为用户名):

l 最佳评测奖1名:yinxiangxv(尹**)

l 优秀评测奖3名:jf_75840292(王*)、jf_09115104(江**)、jf_88521721(刘**)

广东高云半导体科技股份有限公司成立于2014年,是一家专业从事现场可编程逻辑器件(FPGA)研发与设计的国产FPGA高科技公司,致力于向客户提供从芯片、EDA开发软件、IP、开发板到整体系统解决方案的一站式服务。经过多年的积累,高云半导体在FPGA芯片架构、SOC芯片设计、FPGA集成EDA开发环境、FPGA通用解决方案等整个生态链均有核心自主知识,以及国内外发明专利。 通过最新工艺的选择和设计优化,高云半导体已经取得与现有市场国际巨头同类产品媲美的高质量、高可靠性FPGA产品,并已经在汽车、工业控制、电力、通信、医疗、数据中心等应用领域实现规模量产。 高云官网:www.gowinsemi.com.cn