实验目标:

采用3.5GHz的参考时钟给AD9914提供参考,

FPGA程序控制AD9914输出300MHz~350MHz的频率,频率步进0.001Hz。

实验方法:

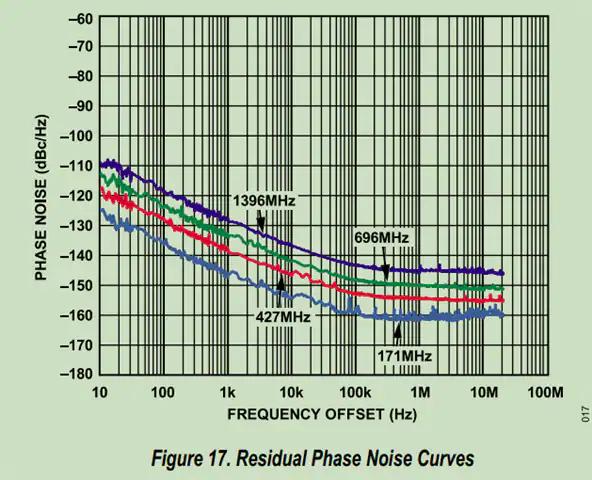

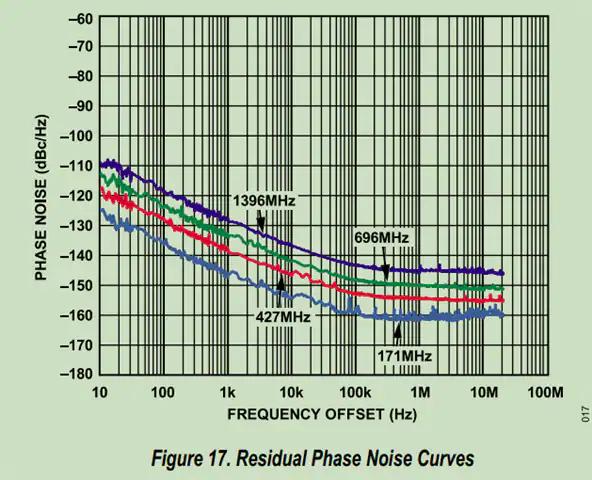

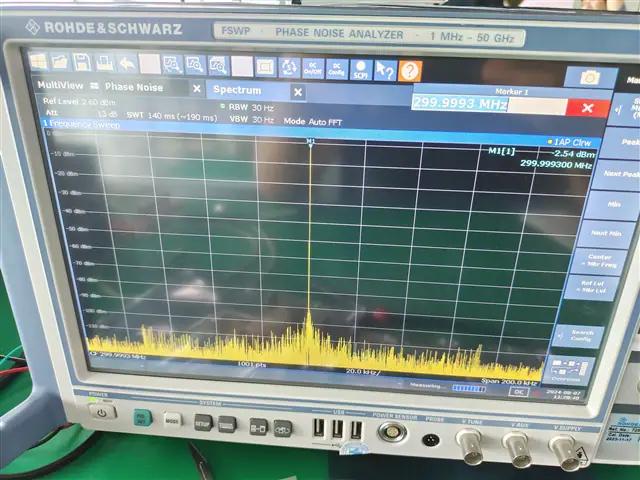

1.先不用实现0.001Hz的频率步进,采用手册中如下图1所示的计算方式控制AD9914的FTW,使AD9914输出300MHz;

图1

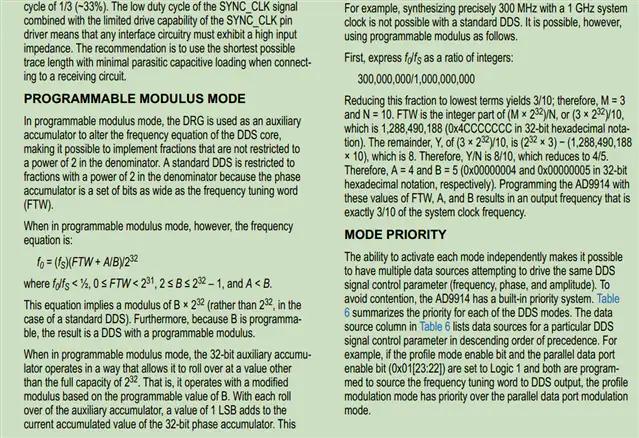

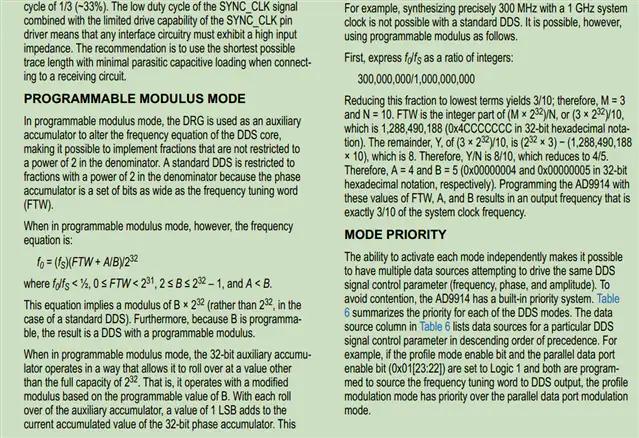

此实验方法输出的300MHz或者其它频率的相位噪声均比手册给出的相位噪声在1kHz频偏处差10dB。此时的实验条件如下:采用的参考3.5GHz的相位噪声如下图2所示:

图2

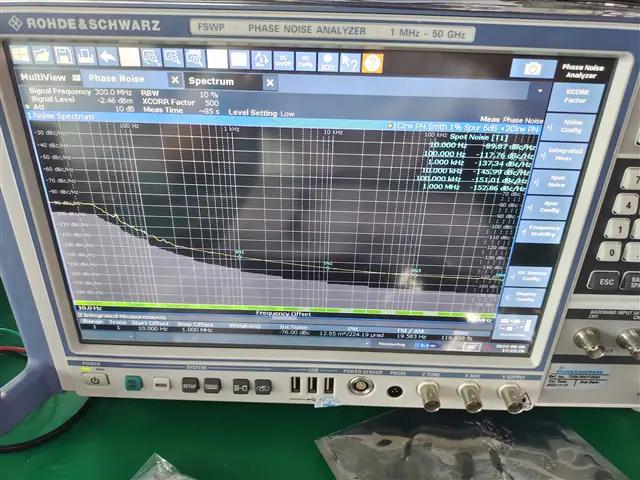

手册的残余相噪如图3:

图3

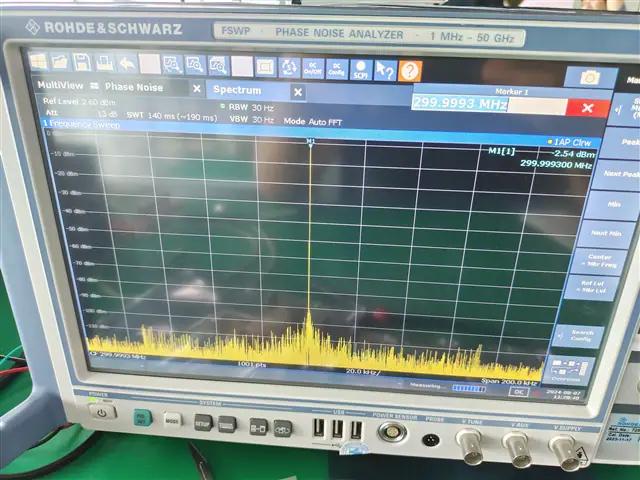

输出的300MHz相噪如图4:

图4

问题1:此时输出300MHz的相位噪声为啥与手册相比差了10dB,请问寄存器配置上有什么讲究可以解决这个问题,目前在ADI官网找到的资料,可能原因是因为相位截断造成的,但是没找到怎么解决的办法,因为手册给出的3.5GHz提供参考下输出475MHz也是可以做到-135dBc/Hz@1kHz左右。所以,这里实际做出来为什么只有-127dBc/Hz@1kHz呢,这里已经排除了

电源和射频硬件的其它原因,之所以说排除了,请见下面的实验方法2.

实验方法:

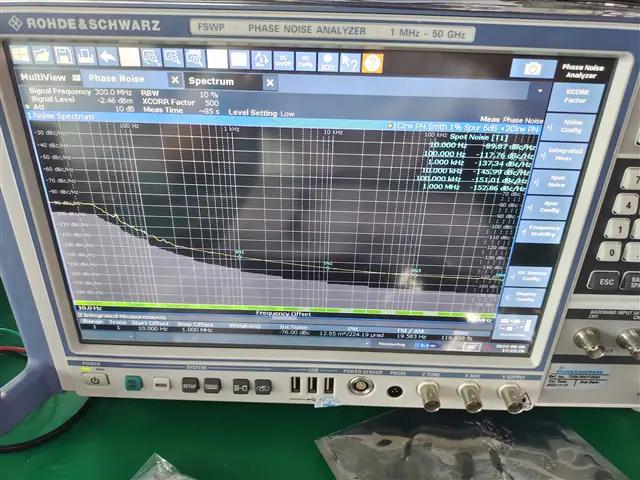

2.实验条件与上述一致,3.5GHz参考,3.5GHz的相噪与上述一致。此时采用手册中如下图5所示的方法控制AD9914输出300MHz,按此计算方式计算出FTW=368140053, A=33, B=35,将其分别写入0x04,0x05,0x06寄存器,此时输出300MHz的相位噪声如下图6所示:

图5

图6

此时的实验结果如图6所示,输出的300MHz的相位噪声与手册基本吻合。但是,在此时的控制下,重新计算300.000001MHz时的FTW和A,B;配置进寄存器后,输出的相位噪声与图4一致。

问题2:为啥实验方法2里输出300MHz的相位噪声可以,输出300.000001MHz不行。此时还没有试输出310MHz或者300MHz~350MHz的其它频率。

收集资料及理解:在ADI管网搜索到的AN-1396应用里面的介绍,以及结合网上描述DDS输出相位截断杂散对相位噪声的影响发现,在相位噪声差的情况下,其近端杂散如下图7所示:

图7

最后想请教ADI的技术支持工程师以及网友的问题是:如果真的是DDS原理中相位截断这个原因导致,那么手册既然给出了在3.5GHz的情况,输出475MHz的相位噪声可以达到如下图8所示(这个的3.5GHz相噪不如本实验中图2的相噪,按照理论分析,本实验输出的300MHz相噪应该与图3中的475MHz的相噪差不多。),就肯定是有解决因相位截断导致相噪变差的办法,目前本人就想请教这个方法。

图8

上述的实验方法2已成功输出过300MHz的相噪是OK的,因此排除电源及硬件或

PCB布局走线的影响,技术支持的朋友提供更多信息支持。

举报

举报