您是使用的CS

Mode 吗?DOUT是在SCLK的下降沿改变输出数据,主控端读取DOUT数据的话需在SCLK的上升沿读取,因为此时DOUT数据已稳定。

看上述波形,黄色应该是SCLK,蓝色是DOUT,DOUT在SCLK的下降沿改变输出状态,这没什么问题

。

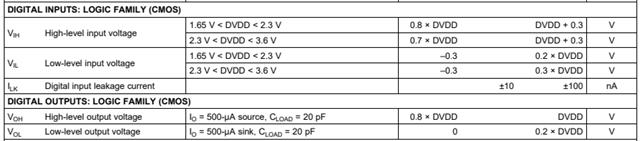

高低电平判断标准如下截图所示:

Chu Allen said:

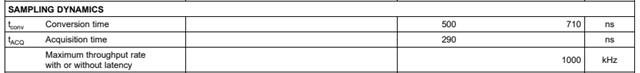

采样周期时间有没有具体的规定?或者说最小采样周期是多少?

采样周期包括tconv 和

tACQ ,如下截图所示,保证datasheet 性能参数的最小采样周期是1us,即710ns+290ns,也就是最大采样率是1MSPS

举报

举报

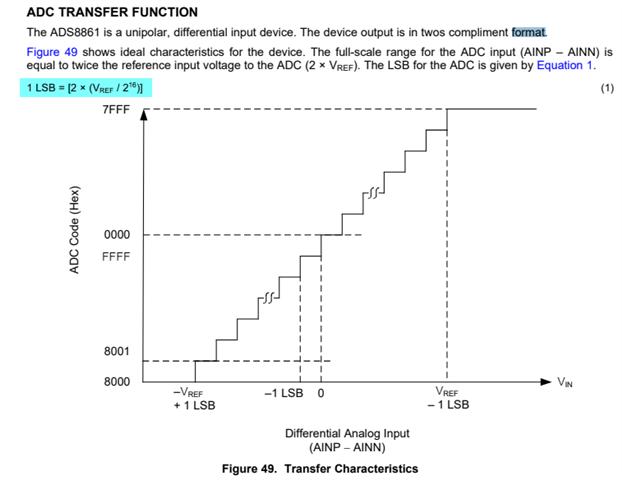

ADS8861的模拟输入与输出code的关系如下截图所示,1

LSB = [2 × (VREF / 2^16)]

您实际测量电压是多少?基准电压是多少?您读取的code是多少?,将读取code转换回输入电压的最直接的方法是将数据与0x8000进行逻辑“与”计算并测试MSB(最高有效位)。如果MSB等于0,只需将十进制等效值乘以LSB值。如果MSB=1,则必须首先从十进制等效值中减去2^n,然后乘以LSB值。“n”是ADC的分辨率。看下这个转换过程是否存在问题?

如果上述转换过程没有问题,那可能读取时序存在问题。ADS8861有两种接口模式,一种是CS模式,一种是Daisy-chain 模式。CS 模式还分3线和四线的,以及 With 或Without

a Busy Indicator,具体见 datasheet DIGITAL

INTERFACE 部分说明,datasheet 分别给出了不同模式下的时序图,建议您使用示波器或逻辑分析仪抓取读取的SPI波形以分析读取时序是否存在问题。

举报

举报

举报

举报

更多回帖