有一些任务在使用 Sys

tick 的 10ms 调度器上执行。 在这 10ms 执行期间,DMA 传输将被启动。

但是,每当 Systick 中断发生时,DMA 传输也会被抢占,并在下一个 10ms 周期中继续进行。

既然 DMA 必须并行运行,我为什么会遇到这个问题? 共享当前配置及其范围图像,以供参考。 如果需要更新配置,请告诉我。

问题情景:

Systick 调度程序,每 10 毫秒一次,其中 4.3 毫秒用于其他应用程序处理,之后使用 SPI 启动 1D DMA 传输(内存到 PDMA)。

由于缓冲区的传输限制为 128 字节。 因此,要传输 4096 字节的数据,我们需要传输 32 个周期。

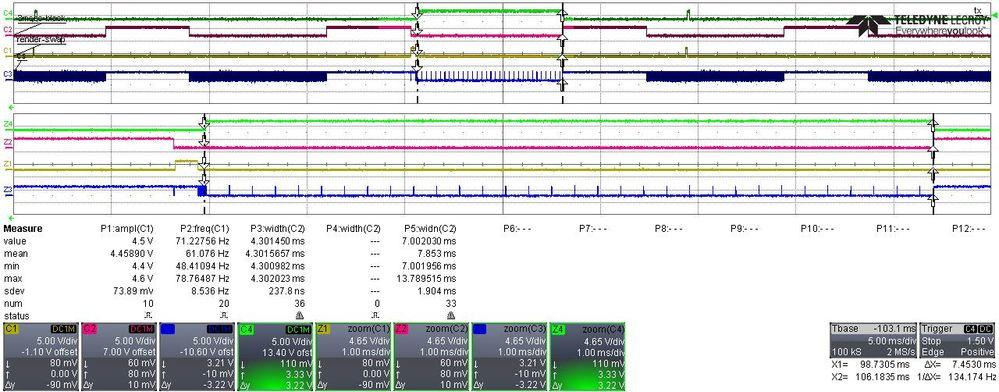

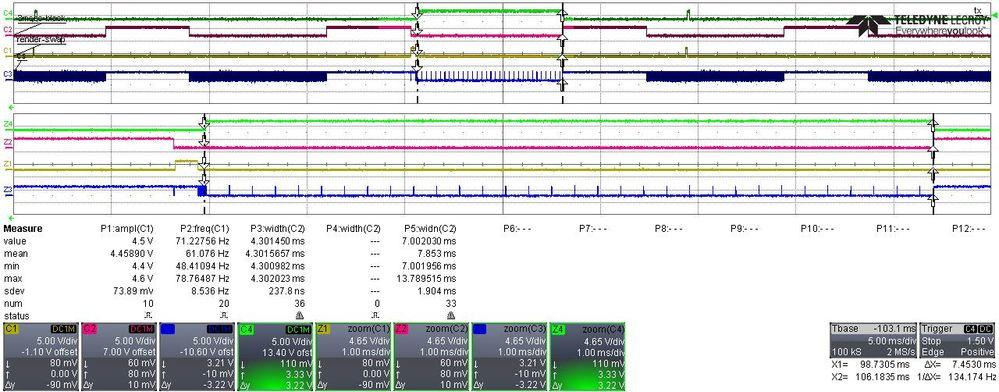

在下面的范围图像中,颜色编码如下

绿色 - GPIO,用于识别 4096 字节数据的 DMA 传输的开始和停止

黄色 - 为执行其他应用指令而封锁的区域。

粉红色--Systick 中断

蓝色--DMA 传输中断,每 128 个突发 32 个周期

如下图所示,每当发生 Systick 中断时,DMA 就会被抢占。

注意:我们甚至尝试将 DMA 的优先级设置为高,但调度却因此而延迟。

GPIO 配置

dma_transfer_data_t dma_transfer_data;

UI_8 DMA_Cfg_Init_Buff[1] = {0};

uint8_t Trigger_Recd=0;

const cy_stc_pdma_chnl_config_t chnl7Config = {

/* CURR_PTR */ .PDMA_Descriptor = stcDescr,

/* CH_CTL PREEMPTABLE */ .preemptable = 0u,

/* CH_CTL PRIO */ .priority = 0u,

/* CH_CTL ENABLED */ .enable = 1u, /* enabled after initialization */

};

static cy_stc_pdma_descr_config_t stcDw1DescrConfig = {

/* DESCR_CTL WAIT_FOR_DEACT */ .deact = 0u,

/* DESCR_CTL INTR_TYPE */ .intrType = CY_PDMA_INTR_1ELEMENT_CMPLT,

/* DESCR_CTL TR_OUT_TYPE */ .trigoutType = CY_PDMA_TRIGOUT_1ELEMENT_CMPLT,

/* DESCR_CTL CH_DISABLE */ .chStateAtCmplt = CY_PDMA_CH_ENABLED,

/* DESCR_CTL TR_IN_TYPE */ .triginType = CY_PDMA_TRIGIN_DESCR,

/* DESCR_CTL DATA_SIZE */ .dataSize = CY_PDMA_BYTE,

/* DESCR_CTL SRC_TRANSFER_SIZE */ .srcTxfrSize = 0u,

/* DESCR_CTL DST_TRANSFER_SIZE */ .destTxfrSize = 1u,

/* DESCR_CTL DESCR_TYPE */ .descrType = CY_PDMA_1D_TRANSFER,

/* DESCR_SRC */ .srcAddr = DMA_Cfg_Init_Buff[0],

/* DESCR_DST */ .destAddr = (uint32_t *) CY_SPI_SCB_TYPE->unTX_FIFO_WR.u32Register,

/* DESCR_X_CTL SRC_X_INCR */ .srcXincr = 1u,

/* DESCR_X_CTL DST_X_INCR */ .destXincr = 0u,

/* DESCR_X_CTL X_COUNT */ .xCount = HW_FIFO_SIZE,

/* DESCR_Y_CTL SRC_Y_INCR */ .srcYincr = 0u,

/* DESCR_Y_CTL DST_Y_INCR */ .destYincr = 0u,

/* DESCR_Y_CTL Y_COUNT */ .yCount = 0u,

/* DESCR_NEXT_PTR */ .descrNext = 0u

};

举报

举报