大家好,

我试图了解 EIM 总线相对于自由运行输入时钟的时钟。这个具体是怎么设置的。我想在可观察性 CLKO 1 或 2 上输出这个时钟信号。

意图:

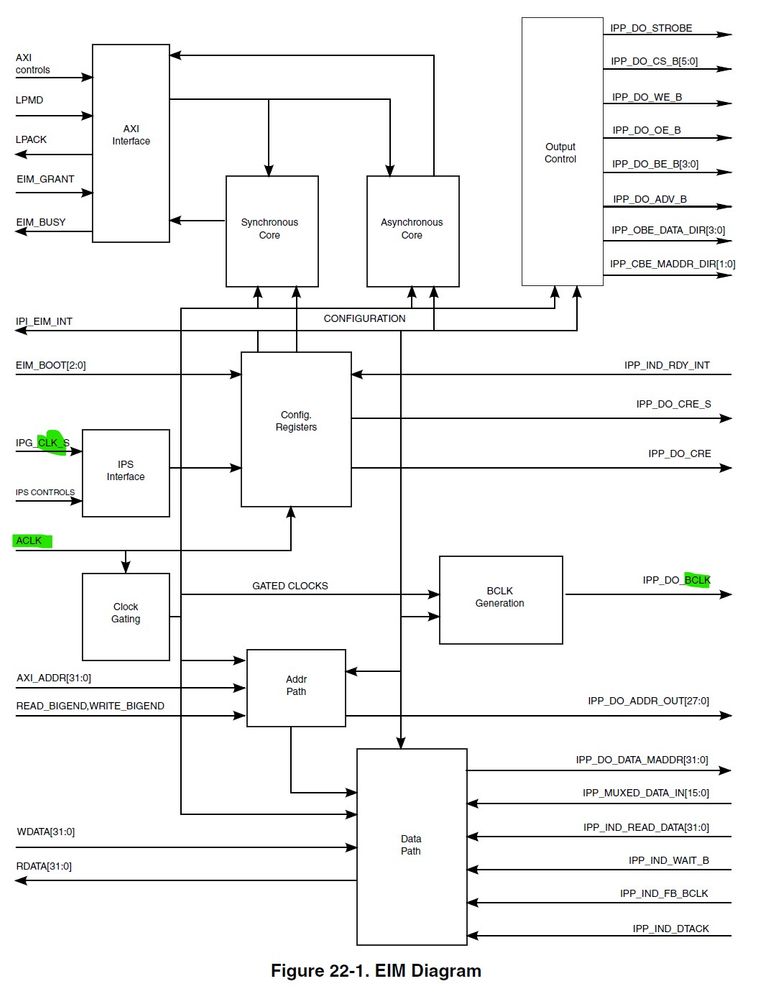

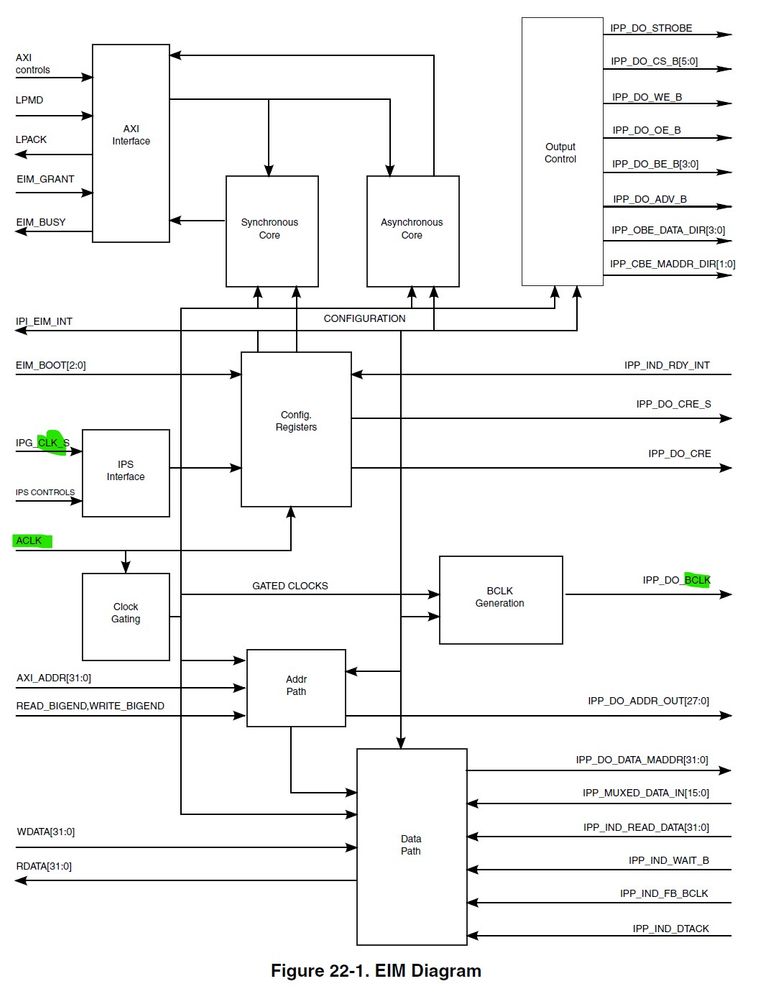

利用 EIM_ACLK_FREERUN 和连续突发与非多路复用地址/数据线一起工作到 CPLD 和

FPGA。这个时钟对于旧设备来说是 43.75 MHz,我想尽量减少对其他设备的影响。

EIM 的外部信号在“表 22-2 EIM 外部信号”EIM_ACLK_FREERUN 中定义,可以通过焊盘输入:EIM_A25、EIM_D31、EIM_EB3。

目前的理解:

最初我认为 PLL3 旁路将允许选择 FREERUN PIN。

然而这似乎并没有通过 CCM_ANALOG 模块传递到 CCM_CLK_SWITCHER。然后进入

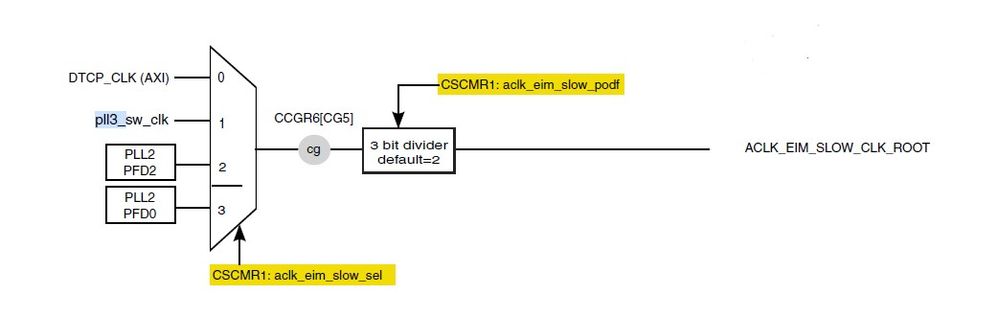

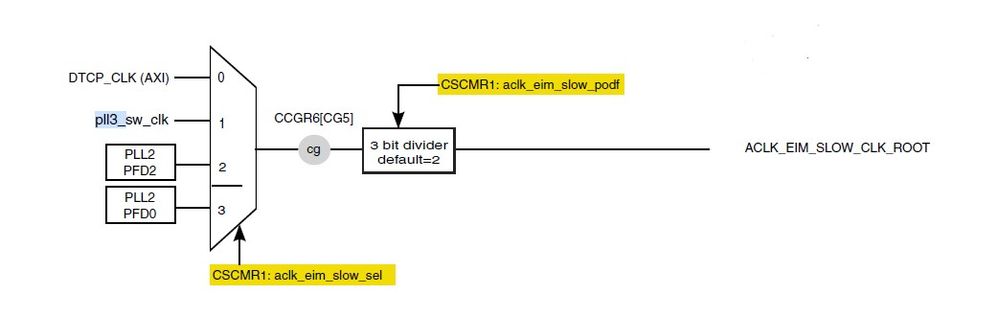

ACLK_EIM_SLOW_CLK_ROOT。

第 22.3 节时钟:EIM 的来源请参阅 CCM,表 22-4 显示了具有两个时钟根的 4 种可能性:aclk_eim_slow_clk_root 和 ipg_clk_root。

具有根的 aclk、aclk_slow 和 aclk_exsc EIM 时钟:aclk_eim_slow_clk_root。

表示 BCLK 不能配置为 aclk_exsc。只留下 aclk 和 aclk_slow。

好消息,它还表明 aclk_eim_slow_clk_root 可以在 CCM_CLKO 1 或 2 上输出。因此我们获得了 aclk_eim_slow_clk_root 的可观察性。

在这里,我看不到自由运行时钟如何作为输入来生成我正在寻找的 ACLK_EIM_SLOW_CLK_ROOT。

CCGR6[CG5] emi_slow_clk_enable

然而,EIM 模块清楚地显示可以选择 FREERUN CLOCK。这是否遵循通过 SoC 的其他路径?

然而在第 22.9.7 节中 EIM 配置寄存器 (EIM_WCR)

位 11:FRUN_ACLK_EN

启用:自由运行 ACLK 启用。

所以我的困惑是为什么没有记录 FRUN_ACLK_EN 和它可能通过 PLL3 旁路的路由 - 很难弄清楚信号的路由以及如何使其在 CLKO1/CLKO2 上可见。