1、纯粹的单时钟同步设计

纯粹的

单时钟同步设计是一种奢望。大部分的ASIC设计都由多个异步时钟驱动,并且对数据信号和控制信号都需要特殊的处理,以确保设计的鲁棒性。大多数学校的课程任务都是完全同步(单时钟)的逻辑。在真正的ASIC设计领域,单时钟设计非常少。

2、控制信号从快时钟域同步到慢时钟域

2、控制信号从快时钟域同步到慢时钟域

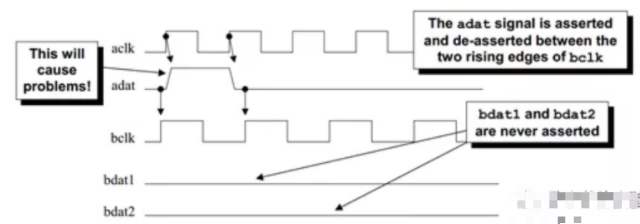

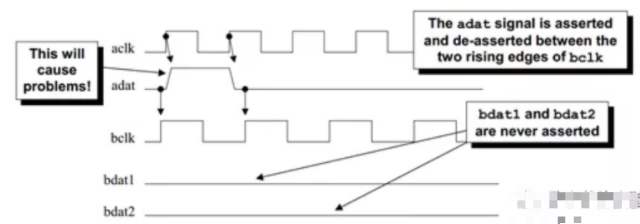

与同步器相关的一个问题是来自发送时钟域的信号可能在被慢时钟域采样之前变化。

将慢时钟域的控制信号同步到快时钟域通常不是问题,因为快时钟域将对慢时钟域的控制信号进行一次或多次采样。在异步时钟域之间传递一个控制信号时,简单的双触发器同步器通常就足够了。但是如果将控制信号从较快的时钟域传递到较慢的时钟域时,可能会出现问题,来自快时钟域的控制信号必须宽于较慢时钟的周期。否则如下图所示,快时钟域的控制信号无法被采样到慢时钟域。

3、在时钟域之间同步数据的两种常用方法

3、在时钟域之间同步数据的两种常用方法

将数据从一个时钟域传递到另一个时钟域类似于传递多个没有顺序关系的控制信号。但是不能使用同步器来同步数据信号,因为会采样到错误数据。

在时钟域之间同步数据的两种常用方法是:

(1)使用握手信号在时钟域之间传递数据

(2)使用FIFO(先进先出存储器)。