1 前言

用FPGA实现的嵌入式系统,均是在更大的芯片中嵌入的重复完成特定功能的计算系统,虽则是隐含嵌入,但实际上在各种常用的芯片中能够找到这些嵌入式系统。例如,消费类电子产品中的手机、寻呼机、数字相机、摄像机、录像机、个人数字助理等。

当今,以现场可编程门阵列(FPGA)来实现可配置的嵌入式系统已越来越广泛。其Spartan-3E FPGA成为实现各种低成本数字消费类系统的理想器件。这是从系统对上市时间的要求、可编程的特性以及集成度等方面考虑有其独特的优势。即采用90纳米工艺生产FPGA器件之后,FPGA器件进一步降低成本,减少功耗和提高性能,低成本使FPGA成为中小批量生产的应用器件,应用范围从早期的军事、通信系统等扩展到低成本消费电子类等产品。

目前,常用FPGA来实现DSP嵌入系统与嵌入微处理器系统,而本文主要介绍高性能、低成本的Spartan-3 FPGA实现的DSP嵌入系统及其Spartan-3系列器件在平板显示器中的应用。

2、关于用Spartan-3 FPG来实现的DSP嵌入系统

为什么利用Spartan-3 FPGA来实现DSP系统,这应首先了解Spartan-3 FPGA特性,即Spadan-3的各种功能及其在实现DSP时的用途。

2.1 Spartan-3 FPGA特性概述。

2.11成本较低的FPGA

*Spartan-3平台FPGA具有很高的性价比

经过优化的Spartan-3 FPGA架构,结合90纳米处理技术和300毫米晶圆技术,每片晶圆产出的完好芯片数足130纳米/200毫米技术的五倍,其每逻辑单元成本(CPL)最低。

*完整的密度范围

Spartan-3FPGA的密度范围是从50,000系统门到5,000,000系统门,这使得低成本FPGA与的密度范围得到了前所未有的扩展;326MHz的系统时钟率;三路电源干线内核电压1.2V、I/O电压1.2“3.3V、辅助设备电压2.5V.它为高容量,面向用户的设备提供了非常低的成本与高性能逻辑方案。

*独特的交错排列I/O引脚技术

Spartan-3FPGA结合了90纳米处理性术和交错排列引脚技术,可以提供、很低的每I/O成本(CPl)和最高的每门I/O数。

2.12 独特的功能

*XCITE技术(数字控制阻抗技术)使用

XCITE片上数字终端不再需要外部电阻器(见图1(a)所示),这提供了大量的优势。 减少系统组件;提高系统可靠性;简化电路板布局;降低制造成本;实现I/O最大带宽;消除短反射噪音。

*选择RAM分级存储(即BlockRAM总位数高达1872kb)与扩展内存

Spartan-3 FPGA具有两种类型的内存,可以满足不同的设计需求,即最大1.8Mb的真实双端口块RAM和最大520Kb的分布式RAM,其封装形式为16位深×1位宽,可用作移位寄存器和FIFO。

*系统时钟管理-具有4个DCM数字时钟管理器

先进的时钟管理为高性能电路的设计者提供了更大的灵活性和更强的控制能力, 见图1(b)所示。最多四个数字时钟管理器(DCM),并带有9个外部输出;8个预设的全球时钟网络,即8根全局时钟线路和丰富的寻址。

*嵌入式乘法器

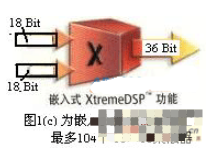

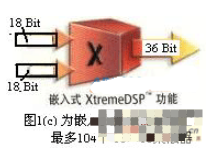

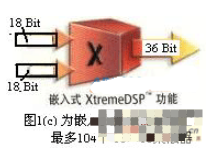

专用的硅资源允许充分地自定义数据路径,并获得最佳DSP性能,见图1(c)所示。 最多104个18×18乘法器,该乘法器模块允许两个18位二进制作为输入并计算输出36位结果,见图所示;而专用的进位逻辑和高效级联,可实现更多功能。

*SelectIO-超级连接

每个I/O针脚都支持24个通用I/O标准中的任意一个,所以Spanan-3 FPGA可以最低的成本提供最灵活的连接,即可编程I/O技术;支持PCI、HSTL、SSSL、超传送(HyperTransport)、LVDS、RSDS、LVPECL、LVPEL、LVCMOS及更多。

2.14逻辑资源

丰富的逻辑单元,寄存器具有移位能力;18X18乘法器;JTAG逻辑与IEEEll49.1/1532说明兼容。

2.15 可以被Xilinx ISE(系统内仿真器)开发系统支持。即综合、映射、替代和寻址。

Spartan-3设备以最低成本提供高密度的FPGA,这使得它们非常适合于数量大、注重成本、以DSP为核心的应用程序。

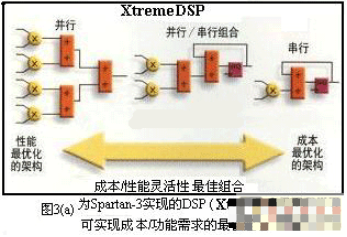

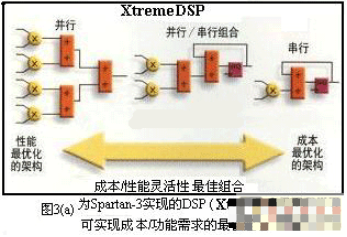

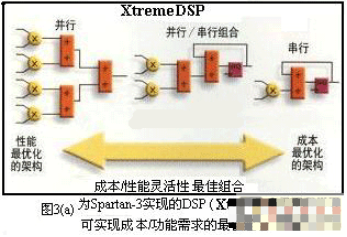

即嵌入式18×18乘法器(最多104个)、每秒最多3300亿次乘法和累加运算(MAC/s)、优秀的高速DSP功能的并行实现能力、灵活的串联架构,可实现成本/功能需求的最佳组合,见图所示最大的成本/性能灵活性。预验证的DSP算法和核心,即滤波器、检波、变换、算法、FEC、相关器。

2.2 Spartan-3独特的器件结构

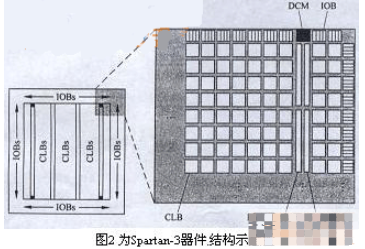

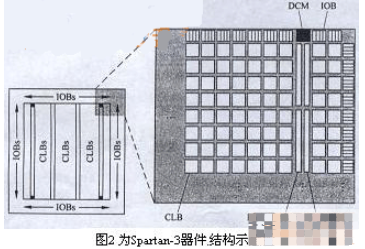

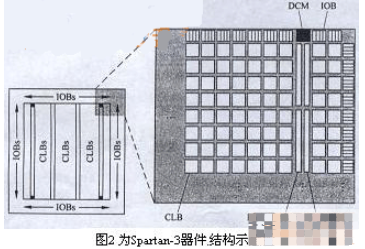

Spartan-3系列的结构可由5个基本的可编程功能模块组成,分别是可配置逻辑模块(CLB),输入/输出模块(IOB)、BlockRAM、乘法器模块和数字时钟管理器(DCM)。这些 小模块的组成如图2所示。一系列IOB模块沿芯片的边沿分布,围绕着一组按规则排列的CLB模块。如XC3S50型只有一个按列排列的BlockRAM嵌在阵列中,XC3S200型到XC3S2000小型有两个按列排列的BlockRAM,而XC3S4000和XC3S5000有4个BlockRAM。每个列状BLockRAM是由几个18kbRAM模块组成,每个模块与专用乘法器有受。。DCM放在BLockRAM的外端。

由上所见, FPGA解决方案的可编程特性降低了新系统设计的内在开发风险。由于拥有诸如多个I/O槽、片上数字时钟管理器、以及大量的Block存储器和分布式存储器等其它功能,Spartan-3也可以高效实现许多控制/胶合逻辑功能,有效减小了系统的尺寸、复杂度和成本。

2.3 Spartan-3 FPGA来实现的DSP嵌入系统

Spartan-3设备以最低成本提供高密度的FPGA,这使得它们非常适合于数量大、注重成本、以DSP为核心的应用程序。

其嵌入式18×18乘法器(最多104个)、每秒最多3300亿次乘法和累加运算(MAC/s)、优秀的高速DSP功能的并行实现能力、灵活的串联架构,可实现成本/功能需求的最佳组合,见图3(a)所示最大的DSP成本/性能灵活性。

预验证的DSP算法和核心,即滤波器、检波、变换、算法、FEC、相关器。而Spartan-3 FPGA 在高性能DSP应用中,有各种不同FIR滤波器技术的适用情况,而FIR滤波器的算法为:

公式中n个系数与n个相应的数据采样相乘,再对内积求和产生单个结果。系数数值将确定滤波器的低通/高通/带通特性,可以利用不同的架构和不同的方法来实现滤波器的功能。

由此可以说,因为FPGA是极高并行度的信号处理引擎,能够满足算法复杂度不断增加的应用要求,通过并行方式提供极高性能的信号处理能力。Xilinx的XtremeDSP模块,如图3(b)所示,使得Sparten3系列FPGA可以为高性能的数字信号处理提供理想的解决方案,达到传统上由ASIC或ASSP完成的高性能信号处理能力。可以针对数字通信和视频图象处理等应用开发高性能的DSP引擎,也可在可编程DSP系统中作为预处理器或协处理器等。

由于嵌入式18×18乘法器(最多104个)适应DSP应用中的众多的功能。提高了操作数输入、中间积和累加器输出的可编程流水线操作。

在复杂算法的数字处理系统中,系统要求的不断提高和集成规模的不断扩大,使得系统结构在设计的开始阶段是不明确的,不可能直接用RTL(寄存器转移级)设计方法进行描述,所以将系统集成到数字芯片中。

采用数字技术对复杂算法进行硬件实现时,首先遇到的问题是在结构上并没有预先的规定,因此需要首先对算法建模和仿真进行优化。与基于RTL针对结构清晰的设计方法不同,算法设计把焦点从针对结构的细节转移到对设计的整体要求和行为,在最高的算法层次上考虑如何进行设计,对系统的行为描述定义了设计要执行的算法,不涉及或很少涉及实现细节,因此行为描述比RTL描述要简洁的多。

图3(c)为易用的DSP设计流程所示, 糸统产生器的DSP设计环境,包含了系统数学建模、算法优化和改进、设计校验和诊断及HDL产生和仿真等。而综合DSP设计服务包括DSP设计等级、现埸工程服务。

3、Spartan-3系列器件在平板显示器中的应用

由于低成本和全功能的结合Spartan-3系列器件特别适合用于实现各种数字消费类系统。使Spartan3器件在平板显示器市场应用中极具吸引力,即Spadan-3器件得到广泛应用的一个市场就是平板显示器(FPD)市场,它是新潮流,值以此为例介绍。

首先要说明的是平板显示器是新型消费类电视中增长最快的部分,其市场上有三种平板显示器,即LCD、等离子和投影电视(DLP)。

3.1 Spartan-3芯片在平板显示器(FPD)应用中的价值

Spartan-3 FPGA提供了FPD系统设计人员非常有用的各种功能。包括能够高效实现DSP功能的嵌入式乘法器;在实现流水线或多通道功能时能够支持高性能并减少资源利用率的移位寄存器;大量的存储器资源;以及对显示器市场普遍使用的差分I/O标准的内在支持,那Spartan-3芯片功能在平板显示器(FPD)应用中的价值是什么,即Spartan-3的各种功能及其在实现DSP时的用途。

*Spartan-3芯片功能在平板显示器(FPD)应用中的价值:

嵌入式乘法器,能有效实现MAC(媒体存储控制) FIR滤波器和其它DSP功能;

移位寄存器逻辑,能有效实现多通道功能;

BlockRAM和分布式RAM,为视频线缓冲器,高速缓存标志存储器,用于DSP系数的便笺式存储器、数据包、缓冲器、FIFO;

对RSDS的内置支持,为无终端电阻的RSDS支持及其它特殊设计考虑之用。

*只有了解FPGA在FPD系统中究竟有是那些典型应用(见图所示4),才能将Spartan-3芯片可以以各种方式应用于FPD设计之中。

3.2 FPGA在FPD系统中典型应用分析(由图所示4可知):

3.21前端预处理

在数字RGB信号馈入到主图像处理引擎之前,通常需要进行某种预外珲。这种预处埋可以是离散余弦变换、解密、或者是交叉/解交叉。通常FPGA呈与客户的图像处理ASIC或ASSP结合使用,一个普遍用途是在图像缩放和解交叉过程中辅助ASSP。

3.22核心处理

尽管核心图像处埋通常是由标准ASSP或定制ASIC完成,但有时也使用FPGA进行定制处理。这些功能实例包括:Y校正、图像缩放、边缘检测、尖锐度、对比度和帧缓冲器。有了Spartan-3器件提供的这些性能,可以在最小的芯片面积上实现多种功能。可以使用的某些专项技术,包括:色空间转换器、JPEG多媒体数字***、离散余弦变换器及MPEG视频编码器/解码器。

可以多次使用FPGA与屏幕或者外部存储器进行接口.Spartan-3支持小摆幅差分I/O标准(如RSDS) ,也支持其它单端标准(如SSTL/HSTL) ,因而它可以在这些应用中进行使用。

FPGA也可以用于实现时序控制单元(TCON,见图5所示),来控制水平和垂直像素显示格式。TCON多少有点象一个垂直和水平显示器计数器。Spartan-3架构中的大量触发器和内置进位链可以有效实现这个功能。同样,由于具有充足的差分I/O通道,Spartan-3FPGA成为I/O密集型设计的有效架构。图5显示了即使一个很小的Spartan-3E器件也具有足够的差分I/O资源来驱动较大的LCD/等离子体屏幕。

4、结束语

Spartan-3E FPGA成为实现各种低成本数字消费类系统的理想器件。该DSP嵌入式系统具有几个共同的特性,即单一功能、软硬件共存、实时反应及严紧的限制。 目前Spartan-3E FPGA生产厂商己有Xilinx、Altera、Lattice等公司,本文仅以Xilinx公司的Spartan-3 FPGA为例作一说明。

在平板显示器系统中,由于仅占用竞争FPGA所需面积的一小部分就能实现高性能DSP,Spartan-3E架构更加高效有用。

到目前为止,Spartan-3 FPGA已成功地应用于平板显示器系统中来实现以下功能:

*SD/HD色空间转换;

*4:4:4 to 4:2:2缩减像素采样;

*数字RGB到USB读卡器功能;

*时序控制和板RSDS驱动器;

*图像压缩/解压缩

除上述之外,只要引入高性能、低成本的Spartan-3FPGA,就可以设计出用在大量数字消费品中的可编程逻辑,例如视讯转接盒、电缆调制解调器、HDTV、DVD-RW播放器、LCDTV、家庭多媒体服务器、家用网关及更多。

1 前言

用FPGA实现的嵌入式系统,均是在更大的芯片中嵌入的重复完成特定功能的计算系统,虽则是隐含嵌入,但实际上在各种常用的芯片中能够找到这些嵌入式系统。例如,消费类电子产品中的手机、寻呼机、数字相机、摄像机、录像机、个人数字助理等。

当今,以现场可编程门阵列(FPGA)来实现可配置的嵌入式系统已越来越广泛。其Spartan-3E FPGA成为实现各种低成本数字消费类系统的理想器件。这是从系统对上市时间的要求、可编程的特性以及集成度等方面考虑有其独特的优势。即采用90纳米工艺生产FPGA器件之后,FPGA器件进一步降低成本,减少功耗和提高性能,低成本使FPGA成为中小批量生产的应用器件,应用范围从早期的军事、通信系统等扩展到低成本消费电子类等产品。

目前,常用FPGA来实现DSP嵌入系统与嵌入微处理器系统,而本文主要介绍高性能、低成本的Spartan-3 FPGA实现的DSP嵌入系统及其Spartan-3系列器件在平板显示器中的应用。

2、关于用Spartan-3 FPG来实现的DSP嵌入系统

为什么利用Spartan-3 FPGA来实现DSP系统,这应首先了解Spartan-3 FPGA特性,即Spadan-3的各种功能及其在实现DSP时的用途。

2.1 Spartan-3 FPGA特性概述。

2.11成本较低的FPGA

*Spartan-3平台FPGA具有很高的性价比

经过优化的Spartan-3 FPGA架构,结合90纳米处理技术和300毫米晶圆技术,每片晶圆产出的完好芯片数足130纳米/200毫米技术的五倍,其每逻辑单元成本(CPL)最低。

*完整的密度范围

Spartan-3FPGA的密度范围是从50,000系统门到5,000,000系统门,这使得低成本FPGA与的密度范围得到了前所未有的扩展;326MHz的系统时钟率;三路电源干线内核电压1.2V、I/O电压1.2“3.3V、辅助设备电压2.5V.它为高容量,面向用户的设备提供了非常低的成本与高性能逻辑方案。

*独特的交错排列I/O引脚技术

Spartan-3FPGA结合了90纳米处理性术和交错排列引脚技术,可以提供、很低的每I/O成本(CPl)和最高的每门I/O数。

2.12 独特的功能

*XCITE技术(数字控制阻抗技术)使用

XCITE片上数字终端不再需要外部电阻器(见图1(a)所示),这提供了大量的优势。 减少系统组件;提高系统可靠性;简化电路板布局;降低制造成本;实现I/O最大带宽;消除短反射噪音。

*选择RAM分级存储(即BlockRAM总位数高达1872kb)与扩展内存

Spartan-3 FPGA具有两种类型的内存,可以满足不同的设计需求,即最大1.8Mb的真实双端口块RAM和最大520Kb的分布式RAM,其封装形式为16位深×1位宽,可用作移位寄存器和FIFO。

*系统时钟管理-具有4个DCM数字时钟管理器

先进的时钟管理为高性能电路的设计者提供了更大的灵活性和更强的控制能力, 见图1(b)所示。最多四个数字时钟管理器(DCM),并带有9个外部输出;8个预设的全球时钟网络,即8根全局时钟线路和丰富的寻址。

*嵌入式乘法器

专用的硅资源允许充分地自定义数据路径,并获得最佳DSP性能,见图1(c)所示。 最多104个18×18乘法器,该乘法器模块允许两个18位二进制作为输入并计算输出36位结果,见图所示;而专用的进位逻辑和高效级联,可实现更多功能。

*SelectIO-超级连接

每个I/O针脚都支持24个通用I/O标准中的任意一个,所以Spanan-3 FPGA可以最低的成本提供最灵活的连接,即可编程I/O技术;支持PCI、HSTL、SSSL、超传送(HyperTransport)、LVDS、RSDS、LVPECL、LVPEL、LVCMOS及更多。

2.14逻辑资源

丰富的逻辑单元,寄存器具有移位能力;18X18乘法器;JTAG逻辑与IEEEll49.1/1532说明兼容。

2.15 可以被Xilinx ISE(系统内仿真器)开发系统支持。即综合、映射、替代和寻址。

Spartan-3设备以最低成本提供高密度的FPGA,这使得它们非常适合于数量大、注重成本、以DSP为核心的应用程序。

即嵌入式18×18乘法器(最多104个)、每秒最多3300亿次乘法和累加运算(MAC/s)、优秀的高速DSP功能的并行实现能力、灵活的串联架构,可实现成本/功能需求的最佳组合,见图所示最大的成本/性能灵活性。预验证的DSP算法和核心,即滤波器、检波、变换、算法、FEC、相关器。

2.2 Spartan-3独特的器件结构

Spartan-3系列的结构可由5个基本的可编程功能模块组成,分别是可配置逻辑模块(CLB),输入/输出模块(IOB)、BlockRAM、乘法器模块和数字时钟管理器(DCM)。这些 小模块的组成如图2所示。一系列IOB模块沿芯片的边沿分布,围绕着一组按规则排列的CLB模块。如XC3S50型只有一个按列排列的BlockRAM嵌在阵列中,XC3S200型到XC3S2000小型有两个按列排列的BlockRAM,而XC3S4000和XC3S5000有4个BlockRAM。每个列状BLockRAM是由几个18kbRAM模块组成,每个模块与专用乘法器有受。。DCM放在BLockRAM的外端。

由上所见, FPGA解决方案的可编程特性降低了新系统设计的内在开发风险。由于拥有诸如多个I/O槽、片上数字时钟管理器、以及大量的Block存储器和分布式存储器等其它功能,Spartan-3也可以高效实现许多控制/胶合逻辑功能,有效减小了系统的尺寸、复杂度和成本。

2.3 Spartan-3 FPGA来实现的DSP嵌入系统

Spartan-3设备以最低成本提供高密度的FPGA,这使得它们非常适合于数量大、注重成本、以DSP为核心的应用程序。

其嵌入式18×18乘法器(最多104个)、每秒最多3300亿次乘法和累加运算(MAC/s)、优秀的高速DSP功能的并行实现能力、灵活的串联架构,可实现成本/功能需求的最佳组合,见图3(a)所示最大的DSP成本/性能灵活性。

预验证的DSP算法和核心,即滤波器、检波、变换、算法、FEC、相关器。而Spartan-3 FPGA 在高性能DSP应用中,有各种不同FIR滤波器技术的适用情况,而FIR滤波器的算法为:

公式中n个系数与n个相应的数据采样相乘,再对内积求和产生单个结果。系数数值将确定滤波器的低通/高通/带通特性,可以利用不同的架构和不同的方法来实现滤波器的功能。

由此可以说,因为FPGA是极高并行度的信号处理引擎,能够满足算法复杂度不断增加的应用要求,通过并行方式提供极高性能的信号处理能力。Xilinx的XtremeDSP模块,如图3(b)所示,使得Sparten3系列FPGA可以为高性能的数字信号处理提供理想的解决方案,达到传统上由ASIC或ASSP完成的高性能信号处理能力。可以针对数字通信和视频图象处理等应用开发高性能的DSP引擎,也可在可编程DSP系统中作为预处理器或协处理器等。

由于嵌入式18×18乘法器(最多104个)适应DSP应用中的众多的功能。提高了操作数输入、中间积和累加器输出的可编程流水线操作。

在复杂算法的数字处理系统中,系统要求的不断提高和集成规模的不断扩大,使得系统结构在设计的开始阶段是不明确的,不可能直接用RTL(寄存器转移级)设计方法进行描述,所以将系统集成到数字芯片中。

采用数字技术对复杂算法进行硬件实现时,首先遇到的问题是在结构上并没有预先的规定,因此需要首先对算法建模和仿真进行优化。与基于RTL针对结构清晰的设计方法不同,算法设计把焦点从针对结构的细节转移到对设计的整体要求和行为,在最高的算法层次上考虑如何进行设计,对系统的行为描述定义了设计要执行的算法,不涉及或很少涉及实现细节,因此行为描述比RTL描述要简洁的多。

图3(c)为易用的DSP设计流程所示, 糸统产生器的DSP设计环境,包含了系统数学建模、算法优化和改进、设计校验和诊断及HDL产生和仿真等。而综合DSP设计服务包括DSP设计等级、现埸工程服务。

3、Spartan-3系列器件在平板显示器中的应用

由于低成本和全功能的结合Spartan-3系列器件特别适合用于实现各种数字消费类系统。使Spartan3器件在平板显示器市场应用中极具吸引力,即Spadan-3器件得到广泛应用的一个市场就是平板显示器(FPD)市场,它是新潮流,值以此为例介绍。

首先要说明的是平板显示器是新型消费类电视中增长最快的部分,其市场上有三种平板显示器,即LCD、等离子和投影电视(DLP)。

3.1 Spartan-3芯片在平板显示器(FPD)应用中的价值

Spartan-3 FPGA提供了FPD系统设计人员非常有用的各种功能。包括能够高效实现DSP功能的嵌入式乘法器;在实现流水线或多通道功能时能够支持高性能并减少资源利用率的移位寄存器;大量的存储器资源;以及对显示器市场普遍使用的差分I/O标准的内在支持,那Spartan-3芯片功能在平板显示器(FPD)应用中的价值是什么,即Spartan-3的各种功能及其在实现DSP时的用途。

*Spartan-3芯片功能在平板显示器(FPD)应用中的价值:

嵌入式乘法器,能有效实现MAC(媒体存储控制) FIR滤波器和其它DSP功能;

移位寄存器逻辑,能有效实现多通道功能;

BlockRAM和分布式RAM,为视频线缓冲器,高速缓存标志存储器,用于DSP系数的便笺式存储器、数据包、缓冲器、FIFO;

对RSDS的内置支持,为无终端电阻的RSDS支持及其它特殊设计考虑之用。

*只有了解FPGA在FPD系统中究竟有是那些典型应用(见图所示4),才能将Spartan-3芯片可以以各种方式应用于FPD设计之中。

3.2 FPGA在FPD系统中典型应用分析(由图所示4可知):

3.21前端预处理

在数字RGB信号馈入到主图像处理引擎之前,通常需要进行某种预外珲。这种预处埋可以是离散余弦变换、解密、或者是交叉/解交叉。通常FPGA呈与客户的图像处理ASIC或ASSP结合使用,一个普遍用途是在图像缩放和解交叉过程中辅助ASSP。

3.22核心处理

尽管核心图像处埋通常是由标准ASSP或定制ASIC完成,但有时也使用FPGA进行定制处理。这些功能实例包括:Y校正、图像缩放、边缘检测、尖锐度、对比度和帧缓冲器。有了Spartan-3器件提供的这些性能,可以在最小的芯片面积上实现多种功能。可以使用的某些专项技术,包括:色空间转换器、JPEG多媒体数字***、离散余弦变换器及MPEG视频编码器/解码器。

可以多次使用FPGA与屏幕或者外部存储器进行接口.Spartan-3支持小摆幅差分I/O标准(如RSDS) ,也支持其它单端标准(如SSTL/HSTL) ,因而它可以在这些应用中进行使用。

FPGA也可以用于实现时序控制单元(TCON,见图5所示),来控制水平和垂直像素显示格式。TCON多少有点象一个垂直和水平显示器计数器。Spartan-3架构中的大量触发器和内置进位链可以有效实现这个功能。同样,由于具有充足的差分I/O通道,Spartan-3FPGA成为I/O密集型设计的有效架构。图5显示了即使一个很小的Spartan-3E器件也具有足够的差分I/O资源来驱动较大的LCD/等离子体屏幕。

4、结束语

Spartan-3E FPGA成为实现各种低成本数字消费类系统的理想器件。该DSP嵌入式系统具有几个共同的特性,即单一功能、软硬件共存、实时反应及严紧的限制。 目前Spartan-3E FPGA生产厂商己有Xilinx、Altera、Lattice等公司,本文仅以Xilinx公司的Spartan-3 FPGA为例作一说明。

在平板显示器系统中,由于仅占用竞争FPGA所需面积的一小部分就能实现高性能DSP,Spartan-3E架构更加高效有用。

到目前为止,Spartan-3 FPGA已成功地应用于平板显示器系统中来实现以下功能:

*SD/HD色空间转换;

*4:4:4 to 4:2:2缩减像素采样;

*数字RGB到USB读卡器功能;

*时序控制和板RSDS驱动器;

*图像压缩/解压缩

除上述之外,只要引入高性能、低成本的Spartan-3FPGA,就可以设计出用在大量数字消费品中的可编程逻辑,例如视讯转接盒、电缆调制解调器、HDTV、DVD-RW播放器、LCDTV、家庭多媒体服务器、家用网关及更多。

举报

举报

举报

举报