高速

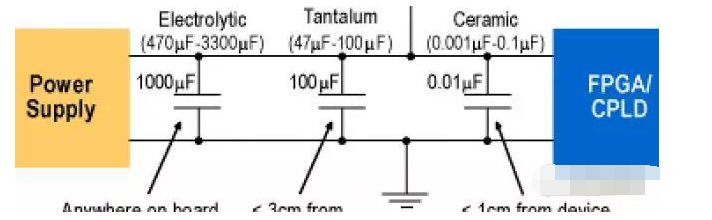

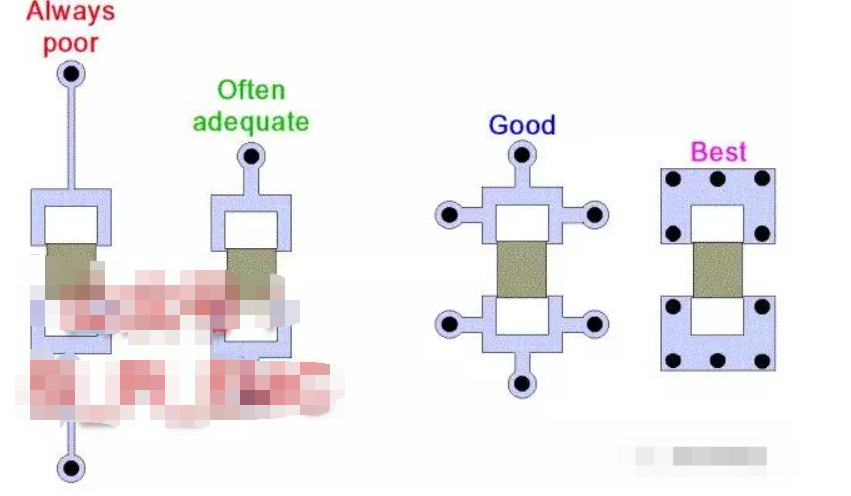

PCB设计有很多比较考究的点,包括常规的设计要求、信号完整性的要求、

电源完整性的要求、EMC的要求、特殊设计要求等等。本文主要是针对高速

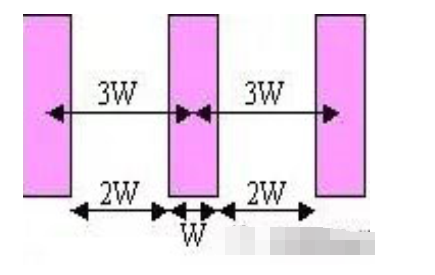

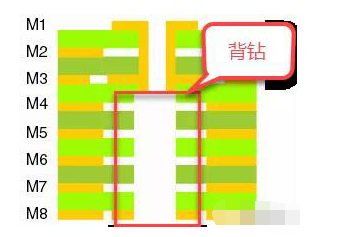

电路信号总线做了一些比较常规的要求列举了一些检查要点,其实还可以进一步的细化,比如针对1.6mm板厚的设计,使用的diff-end via的结构是8mil的drill,16mil的pad,40mil的an

ti-pad,36mil的via间距。这都需要根据实际的情况而定。所以网上很多经验法则都是仅供参考的,包括本文也是如此。

随着信号速率的提升,

电子产品设计也是越来越复杂。无论设计的能力有多强、设计经验多丰富,总会出现一些意向不到的问题。所以很多公司,都会有一些设计规则,让大家在设计中有据可依,也可以在设计完成之后作为checklist,一步一步的检查。下面列举了一些在信号完整性以及电源完整性中需要检查的点

举报

举报

举报

举报

举报

举报