GreenPAK 设计

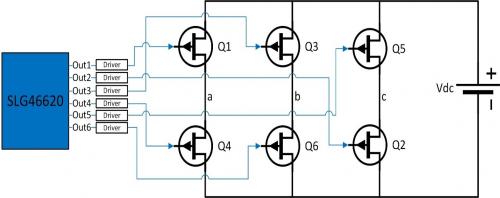

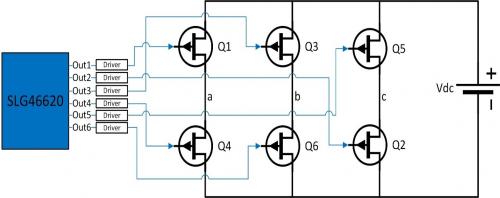

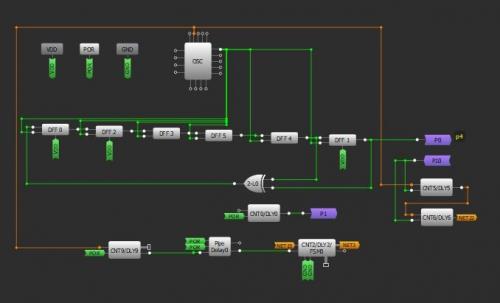

图 5:

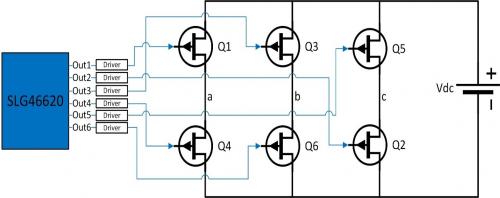

SLG46620 在 RPWM 方案中的角色

图 5 显示了 Dialog CMIC SLG46620 如何在整个方案中发挥功能。CMIC 的基本操作是生成随机 PWM 调制信号,该信号施加在逆变器功率级中使用的开关装置的栅极端子处。

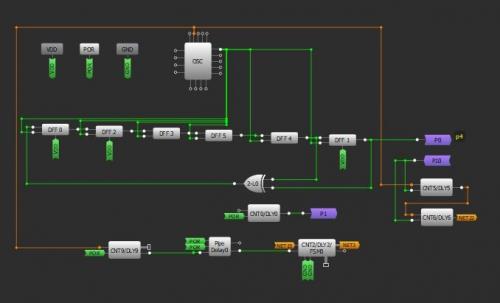

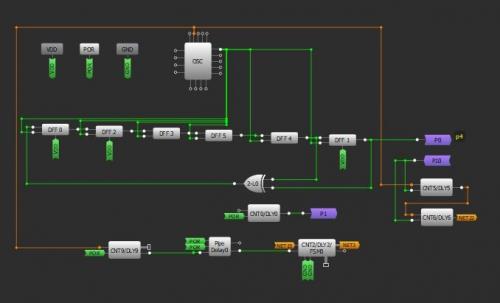

图 6:设计矩阵 0

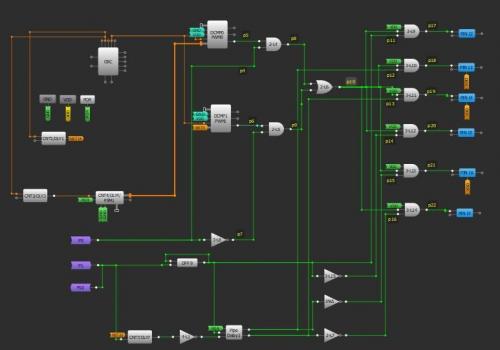

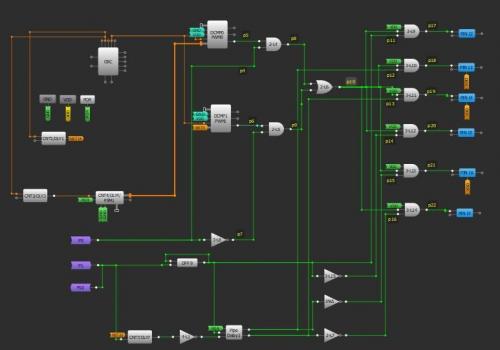

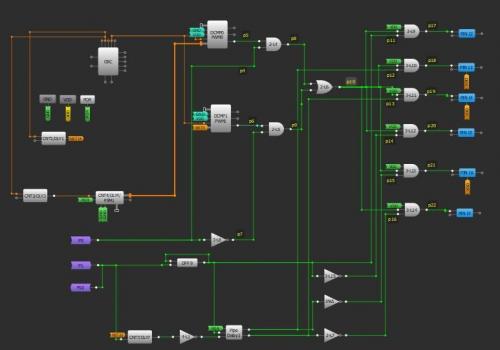

图 7:设计矩阵 1

逆变器输出电压的基频选择为 50 Hz。选择 SLG46220 是因为它提供了足够的资源来执行预期的设计。矩阵 0 和 1 设计分别如图 6 和图 7 所示。在矩阵 0 中,通过以级联(concatenated)方式连接 DFF,并在反馈环路中使用异或门生成伪随机信号(PBRS)P0,如图 6 所示。DFF 由来自振荡器模块 OUT0 的 12.5kHz 时钟信号驱动。

对于锯齿载波信号的生成,建议使用 FSM 块。在 UP = 0 的设定模式下配置的 FSM0 和 FSM1 分别由计数器 CNT1/DLY1 和 CNT3/DLY3 馈送,生成频率为 1.6875MHz 的脉冲。两个 FSM 中的计数器值设置为 134(输出周期 80 us),以实现所需的 12.5 kHz 分立锯齿信号。为了在两个锯齿信号之间实现 180 °C 相移,在 FSM1 使用由 CNT9/DLY9 馈送的管道延迟 40μs 后,启用 FSM0。

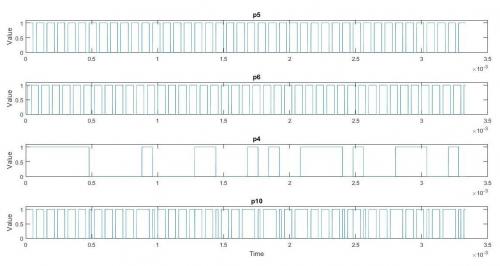

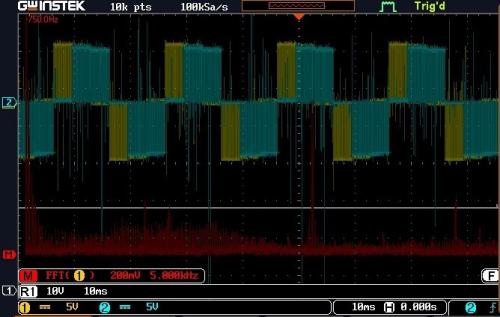

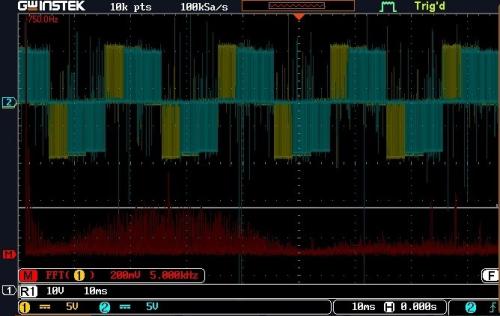

两个锯齿波载波信号通过 FSM0 和 FSM1 的 Q 字节输出端口馈入 DCMP0 和 DCMP1,与恒定参考信号(在寄存器 DCMP0 和 DCMP1 内配置)进行比较,如图 7 所示。由于计数器运行达到值 134,参考值相对于 134 给出,例如 67 等于 0.5(67/134)的值。两个 DCMP(p5 和 p6)的输出进一步与来自 LFSR(p4)的输出信号及其反相值(p7)一起传递到两个 AND 门。向或门馈入这些 AND 门的输出,以随机获得 DCMP 的两个输出之一。或门的输出(p10)还进一步用于调制逆变器的驱动信号。

计数器 CNT0 / DLY0 被配置为生成周期为 10ms 的脉冲,以便生成 50Hz 频率(基波)的输出电压。这些脉冲被馈送到以反相模式配置的 DFF,输出反馈到输入,以生成 50Hz 方波脉冲序列。为确保标记为 p11 至 p16 的输出脉冲相位相差 60 °C,建议使用管道延迟模块。将计数器 CNT5/DLY5、CNT6/DLY6 和 CNT7/DLY7 级联以提供周期为 3.33ms 的脉冲。这些脉冲通过非门馈入管道延迟,因为管道延迟通过计算输入上升沿的数量产生延迟,而计数器通过复位输入复位为 0,生成重复的下降沿,周期为 3.33 ms。输出 0 和 1 的管道延迟分别为输入脉冲提供 3.33 ms 和 6.66 ms 的时间延迟。三个信号,即管道延迟的输入和两个延迟输出,被进一步反相,以提供彼此相移 60°的共 6 个脉冲(p11-p16)。这些 50 Hz、60˚C 相移脉冲与随机脉冲序列(p10)一起进一步被传递到 AND 门,为 3 相逆变器提供最终驱动信号。

GreenPAK 设计

图 5:

SLG46620 在 RPWM 方案中的角色

图 5 显示了 Dialog CMIC SLG46620 如何在整个方案中发挥功能。CMIC 的基本操作是生成随机 PWM 调制信号,该信号施加在逆变器功率级中使用的开关装置的栅极端子处。

图 6:设计矩阵 0

图 7:设计矩阵 1

逆变器输出电压的基频选择为 50 Hz。选择 SLG46220 是因为它提供了足够的资源来执行预期的设计。矩阵 0 和 1 设计分别如图 6 和图 7 所示。在矩阵 0 中,通过以级联(concatenated)方式连接 DFF,并在反馈环路中使用异或门生成伪随机信号(PBRS)P0,如图 6 所示。DFF 由来自振荡器模块 OUT0 的 12.5kHz 时钟信号驱动。

对于锯齿载波信号的生成,建议使用 FSM 块。在 UP = 0 的设定模式下配置的 FSM0 和 FSM1 分别由计数器 CNT1/DLY1 和 CNT3/DLY3 馈送,生成频率为 1.6875MHz 的脉冲。两个 FSM 中的计数器值设置为 134(输出周期 80 us),以实现所需的 12.5 kHz 分立锯齿信号。为了在两个锯齿信号之间实现 180 °C 相移,在 FSM1 使用由 CNT9/DLY9 馈送的管道延迟 40μs 后,启用 FSM0。

两个锯齿波载波信号通过 FSM0 和 FSM1 的 Q 字节输出端口馈入 DCMP0 和 DCMP1,与恒定参考信号(在寄存器 DCMP0 和 DCMP1 内配置)进行比较,如图 7 所示。由于计数器运行达到值 134,参考值相对于 134 给出,例如 67 等于 0.5(67/134)的值。两个 DCMP(p5 和 p6)的输出进一步与来自 LFSR(p4)的输出信号及其反相值(p7)一起传递到两个 AND 门。向或门馈入这些 AND 门的输出,以随机获得 DCMP 的两个输出之一。或门的输出(p10)还进一步用于调制逆变器的驱动信号。

计数器 CNT0 / DLY0 被配置为生成周期为 10ms 的脉冲,以便生成 50Hz 频率(基波)的输出电压。这些脉冲被馈送到以反相模式配置的 DFF,输出反馈到输入,以生成 50Hz 方波脉冲序列。为确保标记为 p11 至 p16 的输出脉冲相位相差 60 °C,建议使用管道延迟模块。将计数器 CNT5/DLY5、CNT6/DLY6 和 CNT7/DLY7 级联以提供周期为 3.33ms 的脉冲。这些脉冲通过非门馈入管道延迟,因为管道延迟通过计算输入上升沿的数量产生延迟,而计数器通过复位输入复位为 0,生成重复的下降沿,周期为 3.33 ms。输出 0 和 1 的管道延迟分别为输入脉冲提供 3.33 ms 和 6.66 ms 的时间延迟。三个信号,即管道延迟的输入和两个延迟输出,被进一步反相,以提供彼此相移 60°的共 6 个脉冲(p11-p16)。这些 50 Hz、60˚C 相移脉冲与随机脉冲序列(p10)一起进一步被传递到 AND 门,为 3 相逆变器提供最终驱动信号。

举报

举报

举报

举报

举报

举报

举报

举报