Applica

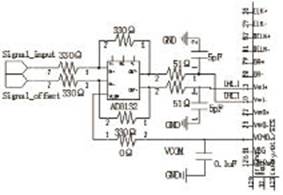

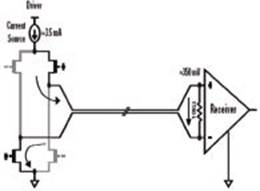

tion of ADC ADC08D1000 in High-speed Signal Acquisition System

成都

电子科技大学 赵昆 黄建国 邱渡裕

引言

目前高速高分辨率采样实现有两种有效方法:等效采样技术,该方法只适用于周期信号的采集;并行交替采样技术,该方法可以较大提高采样速率。但是第二种方法有两个缺点:一是各路数据延时不等引起的采样点偏移,二是各路之间增益不一致。近年来,NS、Atmel等公司都开发出了高速ADC,比如ADC08D1000、AT84AS003TP等,它们都是经采样后分多路降速进行传输。目前,多路并行数据传输存储成为高速信号采集系统的主流趋势。

举报

举报

举报

举报

举报

举报

举报

举报