输入:DCM的CLKIN = 50MHz晶体振荡器(PIN B8)

输出:DCM的CLK0 = 50MHz,是A / D模块的时钟,FIR通带,FIR通道(由IP Core生成)

DCM = 18MHz的CLKFX是分频输入(但输出不是18MHz)

除法输出= 18MHz / 20 = 900MHz(但它是1.69MHz !!!这很奇怪。)但它在仿真(测试平台)上运行良好。

900MHz是块A / D的输入信号。

我想说当与A / D块等的时钟链接时,DCM的输出有问题而我没有解决。没有理由!

谢谢!

以上来自于谷歌翻译

以下为原文

Input: CLKIN of DCM=50MHz crystal oscillator(PIN B8)

Output: CLK0 of DCM =50MHz ,is the clock of A/D block , FIR pass band ,FIR pass bas(generate by IP Core)

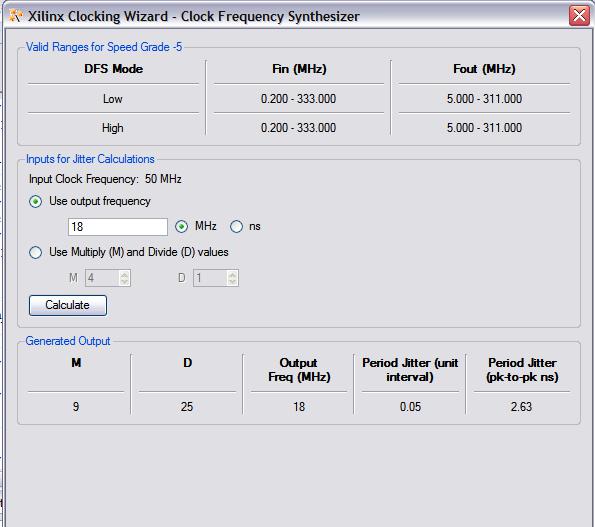

CLKFX of DCM = 18MHz is the input of block division.(but the output isn't 18MHz)

Output of division=18MHz/20=900MHz(but it is 1.69MHz !!! it is strange.) But it works well on simulation(test bench).

900MHz is a input signal of block A/D.

I want to say that there is problem at output of DCM when it links with clock of A/D block etc. and I don't unstand.There is no reason!

thank you!

输入:DCM的CLKIN = 50MHz晶体振荡器(PIN B8)

输出:DCM的CLK0 = 50MHz,是A / D模块的时钟,FIR通带,FIR通道(由IP Core生成)

DCM = 18MHz的CLKFX是分频输入(但输出不是18MHz)

除法输出= 18MHz / 20 = 900MHz(但它是1.69MHz !!!这很奇怪。)但它在仿真(测试平台)上运行良好。

900MHz是块A / D的输入信号。

我想说当与A / D块等的时钟链接时,DCM的输出有问题而我没有解决。没有理由!

谢谢!

以上来自于谷歌翻译

以下为原文

Input: CLKIN of DCM=50MHz crystal oscillator(PIN B8)

Output: CLK0 of DCM =50MHz ,is the clock of A/D block , FIR pass band ,FIR pass bas(generate by IP Core)

CLKFX of DCM = 18MHz is the input of block division.(but the output isn't 18MHz)

Output of division=18MHz/20=900MHz(but it is 1.69MHz !!! it is strange.) But it works well on simulation(test bench).

900MHz is a input signal of block A/D.

I want to say that there is problem at output of DCM when it links with clock of A/D block etc. and I don't unstand.There is no reason!

thank you!

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报