嗨,

我想设计一个

电路来输出16位数据的0的前导数。

我使用Spartan 6 EDK板和ISE 13.4。

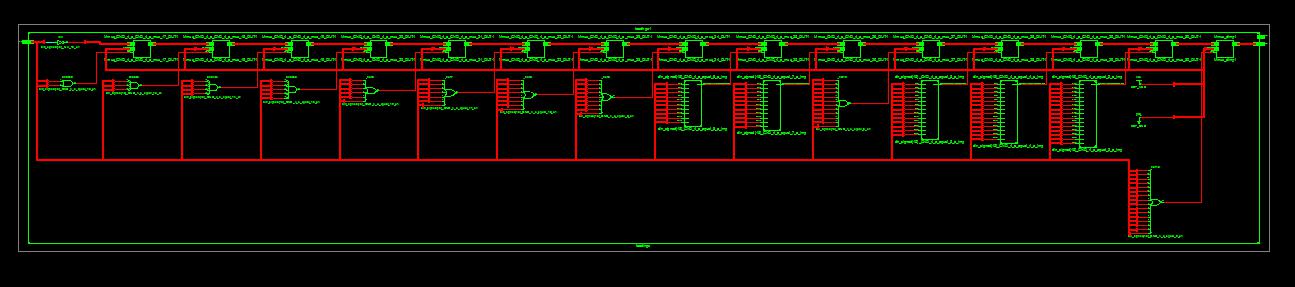

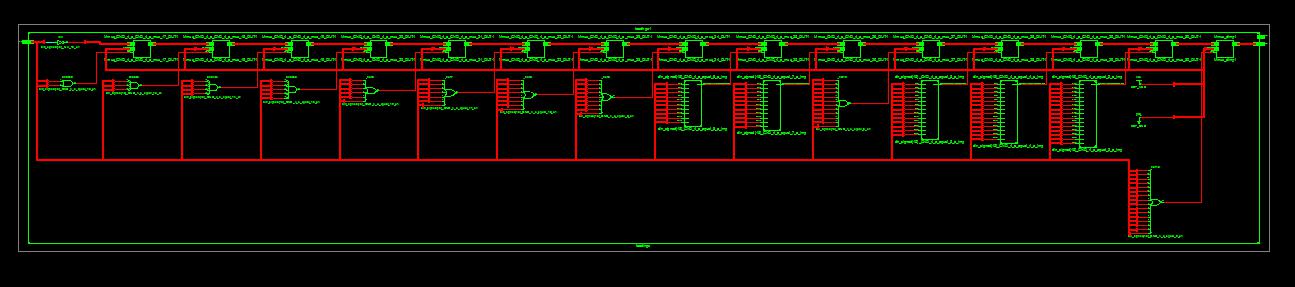

对我来说,RTL视图显示来自此行的16个级联逻辑并不奇怪:

开始

din_signed

num0 to_signed(15,5)when(din_signed(15 DOWNTO 1)=“000000000000000”)否则to_signed(14,5)when(din_signed(15 DOWNTO 2)=“00000000000000”)否则to_signed(13,5)when(din_signed

(15 DOWNTO 3)=“0000000000000”)否则to_signed(12,5)当(din_signed(15 DOWNTO 4)=“000000000000”)否则to_signed(11,5)当(din_signed(15 DOWNTO 5)=“00000000000”)

否则to_signed(10,5)当(din_signed(15 DOWNTO 6)=“0000000000”)否则to_signed(9,5)当(din_signed(15 DOWNTO 7)=“000000000”)否则to_signed(8,5)当(din_signed)

(15 DOWNTO 8)=“00000000”)否则to_signed(7,5)当(din_signed(15 DOWNTO 9)=“0000000”)否则to_signed(6,5)when(din_signed(15 DOWNTO 10)=“000000”)

否则to_signed(5,5)当(din_signed(15 DOWNTO 11)=“00000”)否则to_signed(4,5)当(din_signed(15 DOWNTO 12)=“0000”)否则to_signed(3,5)当(din_signed)

(15 DOWNTO 13)=“000”)否则to_signed(2,5)当(din_signed(15 DOWNTO 14)=“00”)否则to_signed(1,5)当(din_signed(15)='0')否则to_signed

(0,5);

我希望项目运行得更快。

我想应该用更多的逻辑来完成,但我不知道该怎么做。

有办法到达那里吗?

附加了vhdl文件和RTL视图文件。

谢谢,

leadingz.vhd 3 KB

以上来自于谷歌翻译

以下为原文

Hi,

I want to design a circuit to output the leading the number of 0's of a 16 bit data. I use Spartan 6 EDK board with ISE 13.4. It is not surprise to me that the RTL view shows 16 cascaded logic from this line:

begin

din_signed <= signed(din);

num0 <= to_signed(16, 5) when (din_signed(15 DOWNTO 0) = "0000000000000000") else

to_signed(15, 5) when (din_signed(15 DOWNTO 1) = "000000000000000") else

to_signed(14, 5) when (din_signed(15 DOWNTO 2) = "00000000000000") else

to_signed(13, 5) when (din_signed(15 DOWNTO 3) = "0000000000000") else

to_signed(12, 5) when (din_signed(15 DOWNTO 4) = "000000000000") else

to_signed(11, 5) when (din_signed(15 DOWNTO 5) = "00000000000") else

to_signed(10, 5) when (din_signed(15 DOWNTO 6) = "0000000000") else

to_signed( 9, 5) when (din_signed(15 DOWNTO 7) = "000000000") else

to_signed( 8, 5) when (din_signed(15 DOWNTO 8) = "00000000") else

to_signed( 7, 5) when (din_signed(15 DOWNTO 9) = "0000000") else

to_signed( 6, 5) when (din_signed(15 DOWNTO 10) = "000000") else

to_signed( 5, 5) when (din_signed(15 DOWNTO 11) = "00000") else

to_signed( 4, 5) when (din_signed(15 DOWNTO 12) = "0000") else

to_signed( 3, 5) when (din_signed(15 DOWNTO 13) = "000") else

to_signed( 2, 5) when (din_signed(15 DOWNTO 14) = "00") else

to_signed( 1, 5) when (din_signed(15) = '0') else

to_signed( 0, 5);

I want the project runs faster. I guess it should be done with more logic, but I don't know how to do that. Is there a way to get there?

The vhdl file and the RTL view file are attached.

Thanks,

leadingz.vhd 3 KB

举报

举报

举报

举报

举报

举报

举报

举报