引用: yweyerwq 发表于 2019-3-4 11:23

如果您的写时序是正确的,没有做“reset”操作,没有掉电,DAC内部的寄存器里会一值保持写入的值。您是否能详细的描述一下,您是如何判断必须“一直写入才能有输出“。CLR管脚是如果操作的?是否误写了软件的reset功能?最好能把一个完整的写时序波形上传一下,以便准确的定位问题。 ...

AD5663

的电压调试程序如下:

module AD5663(

input clk_50M,

output clk_10M,

output SYNC,

output DataOut,

output clr,

output ldac,

output wire tps_79633_en,

output wire REF196_EN

);

assign tps_79633_en = 1;

assign REF196_EN = 1;

clk_div clk_div_1

(// Clock in ports

.CLK_IN1(clk_50M), // IN

// Clock out ports

.CLK_OUT1(clk_10M)); // OUT

reg [23:0] data;

reg [4:0] cnt = 0;

reg [4:0] data_cnt = 0;

reg SYNC = 0;

reg [1:0] sync_num = 0;//

只配置一次

// reg sync_num = 0;//

不断配置

reg DataOut = 0;

reg clr = 1;

reg ldac = 0;

always @(posedge clk_10M)

begin

if(cnt == 5'd27)

begin

cnt <= 0;

end

else

begin

cnt <= cnt + 1;

end

end

always @(negedge clk_10M)

begin

if(cnt == 5'd1)

begin

SYNC <= 1;

end

else if(cnt == 5'd3)

begin

SYNC <= 0;

end

else

begin

SYNC <= SYNC;

end

end

always @(negedge clk_10M)

begin

if(cnt == 5'd1)

begin

if(sync_num < 2'd3)

begin

sync_num <= sync_num + 1;

end

else

begin

sync_num <= sync_num;

end

end

else

begin

sync_num <= sync_num;

end

end

always @ (negedge clk_10M)

begin

if(cnt == 27)

begin

begin

ldac <= 0;

end

end

else

begin

ldac <= 1;

end

end

always @(negedge clk_10M)

begin

if(cnt == 5'd2)

begin

data_cnt <= 5'd23;

end

else

begin

data_cnt <= data_cnt - 1;

end

end

always @(negedge clk_10M)

begin

case(sync_num)

3'd1: data <= 24'h0064D8;

3'd2: data <= 24'h0064D8;

// 3'd3: data <= 24'h0064D8;

default: data <= 24'h19E8B9;

endcase

end

always @(negedge clk_10M)

begin

DataOut <= data[data_cnt];

end

endmodule

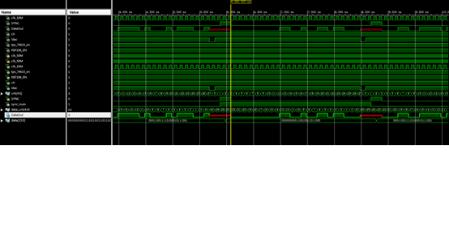

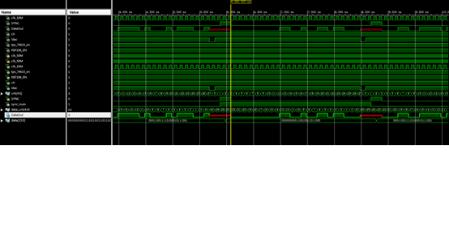

波形图为:

不断配置的波形图:

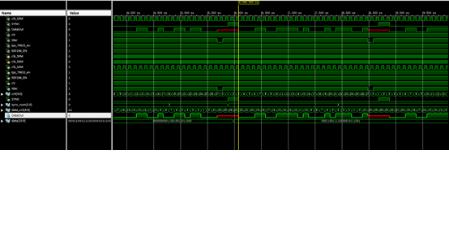

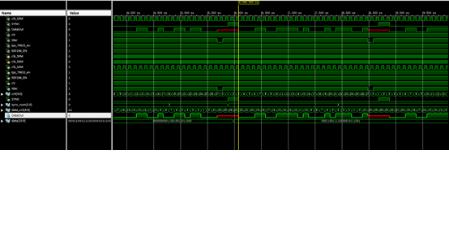

只配置一次的波形图:

只配置一次的波形图:

只有不断重复写入指令,才能测出电压,如果只写入一次的话,则没有电压显示,请问这是什么原因?是我程序哪里出了问题?请指教,急求,谢谢。

引用: yweyerwq 发表于 2019-3-4 11:23

如果您的写时序是正确的,没有做“reset”操作,没有掉电,DAC内部的寄存器里会一值保持写入的值。您是否能详细的描述一下,您是如何判断必须“一直写入才能有输出“。CLR管脚是如果操作的?是否误写了软件的reset功能?最好能把一个完整的写时序波形上传一下,以便准确的定位问题。 ...

AD5663

的电压调试程序如下:

module AD5663(

input clk_50M,

output clk_10M,

output SYNC,

output DataOut,

output clr,

output ldac,

output wire tps_79633_en,

output wire REF196_EN

);

assign tps_79633_en = 1;

assign REF196_EN = 1;

clk_div clk_div_1

(// Clock in ports

.CLK_IN1(clk_50M), // IN

// Clock out ports

.CLK_OUT1(clk_10M)); // OUT

reg [23:0] data;

reg [4:0] cnt = 0;

reg [4:0] data_cnt = 0;

reg SYNC = 0;

reg [1:0] sync_num = 0;//

只配置一次

// reg sync_num = 0;//

不断配置

reg DataOut = 0;

reg clr = 1;

reg ldac = 0;

always @(posedge clk_10M)

begin

if(cnt == 5'd27)

begin

cnt <= 0;

end

else

begin

cnt <= cnt + 1;

end

end

always @(negedge clk_10M)

begin

if(cnt == 5'd1)

begin

SYNC <= 1;

end

else if(cnt == 5'd3)

begin

SYNC <= 0;

end

else

begin

SYNC <= SYNC;

end

end

always @(negedge clk_10M)

begin

if(cnt == 5'd1)

begin

if(sync_num < 2'd3)

begin

sync_num <= sync_num + 1;

end

else

begin

sync_num <= sync_num;

end

end

else

begin

sync_num <= sync_num;

end

end

always @ (negedge clk_10M)

begin

if(cnt == 27)

begin

begin

ldac <= 0;

end

end

else

begin

ldac <= 1;

end

end

always @(negedge clk_10M)

begin

if(cnt == 5'd2)

begin

data_cnt <= 5'd23;

end

else

begin

data_cnt <= data_cnt - 1;

end

end

always @(negedge clk_10M)

begin

case(sync_num)

3'd1: data <= 24'h0064D8;

3'd2: data <= 24'h0064D8;

// 3'd3: data <= 24'h0064D8;

default: data <= 24'h19E8B9;

endcase

end

always @(negedge clk_10M)

begin

DataOut <= data[data_cnt];

end

endmodule

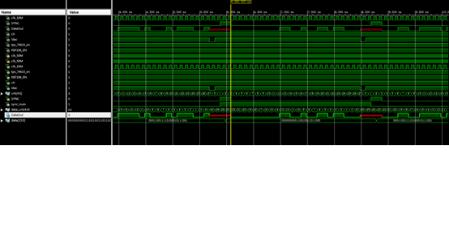

波形图为:

不断配置的波形图:

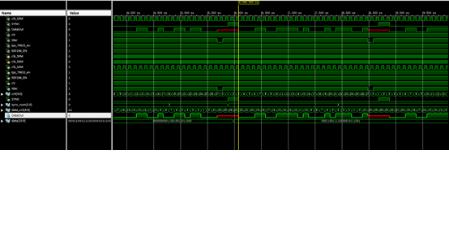

只配置一次的波形图:

只配置一次的波形图:

只有不断重复写入指令,才能测出电压,如果只写入一次的话,则没有电压显示,请问这是什么原因?是我程序哪里出了问题?请指教,急求,谢谢。

举报

举报

举报

举报

举报

举报

举报

举报