举报

举报

引用: wyywerw2 发表于 2019-1-15 13:48

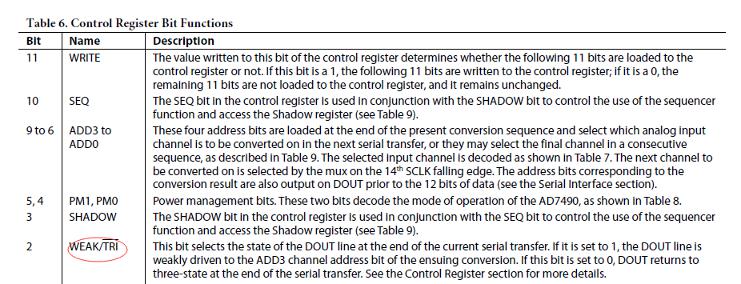

1. ADD3这个位是有的,在CS拉低以后,延时超过20ns,这个位就可以出来。在这段时间内SCLK为高,并且不能跳变。

2. 这个B点的含义就是ADC内部的采保电路在这个时刻从保持状态转换为跟踪状态,前提是这个时候是非shadow Register操作。

3. 这个时序图含义是SCLK下降沿来了以后,经过最多60ns,DOUT的数据就会输出来,除了最开 ...

举报

举报

引用: chiaho168 发表于 2019-1-15 14:04

谢谢大神的答复,你的描述非常的简洁明了。实际上理解了ADD3在什么时候出现其他的问题就迎刃而解了。其实只要在CS拉低之后,SCLK的第一个下降沿之前把ADD3读出来即可。不过这种类型的时序确实以前没碰到过,才疏学浅了

后面的底点的波形等我出差回去的时候再测试上传下。

举报

举报

更多回帖