你好,我对环路滤波器进行了设置。

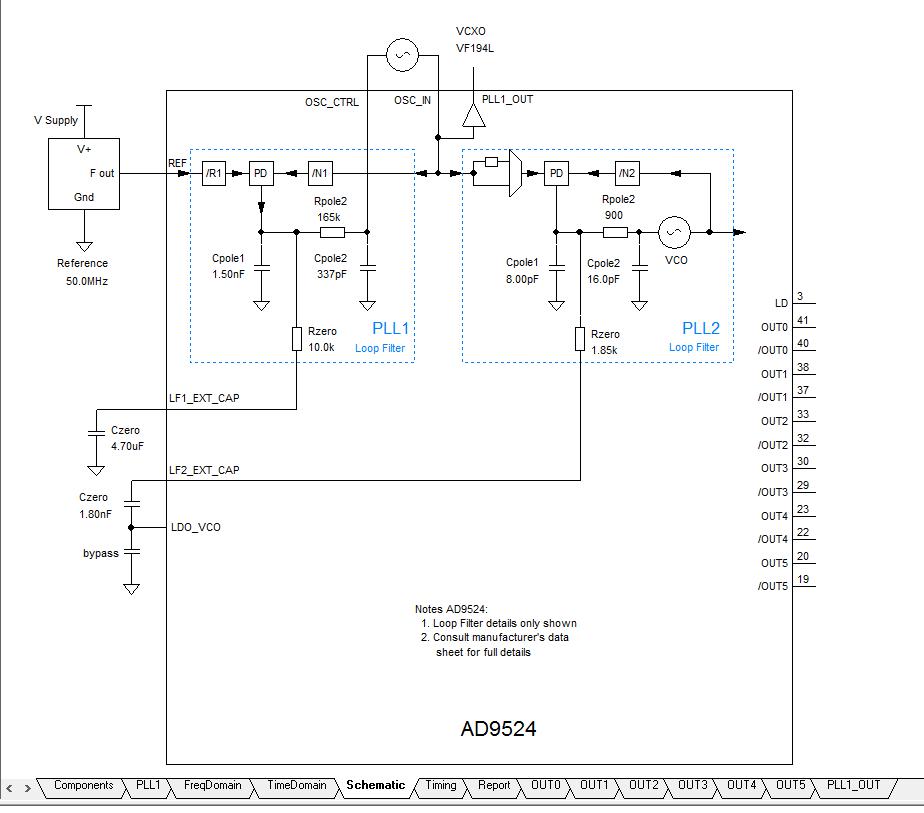

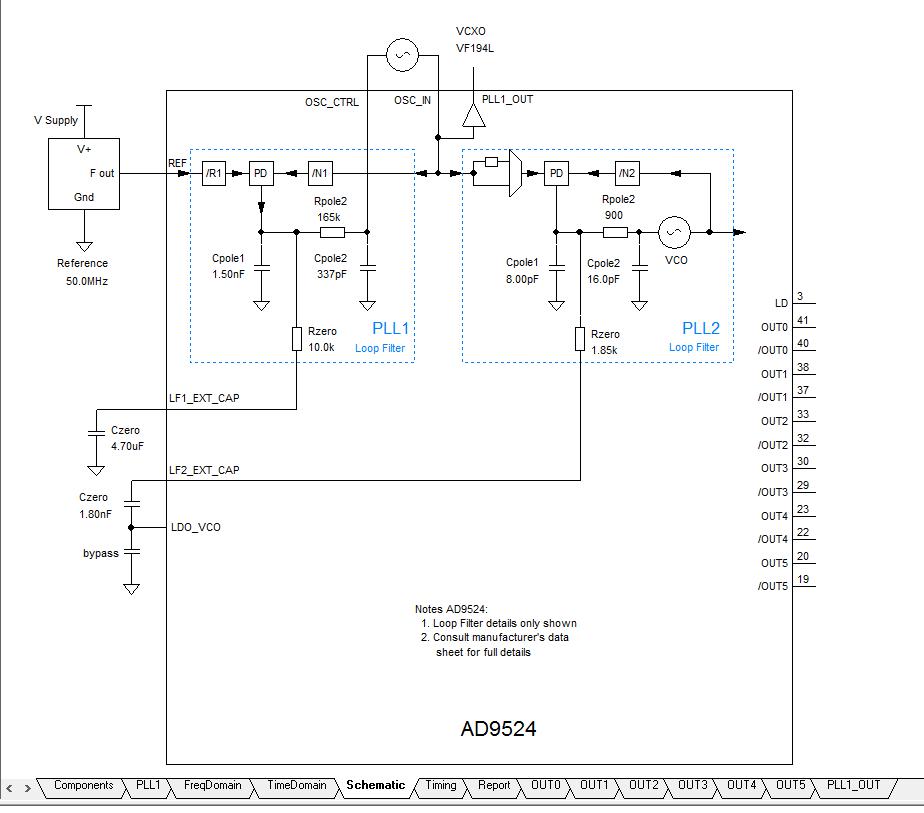

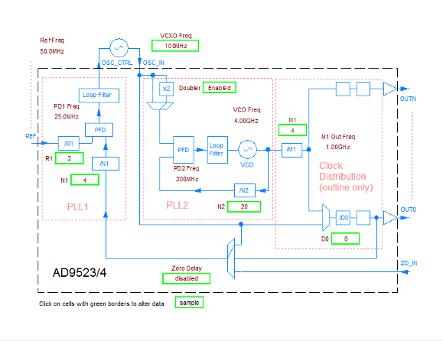

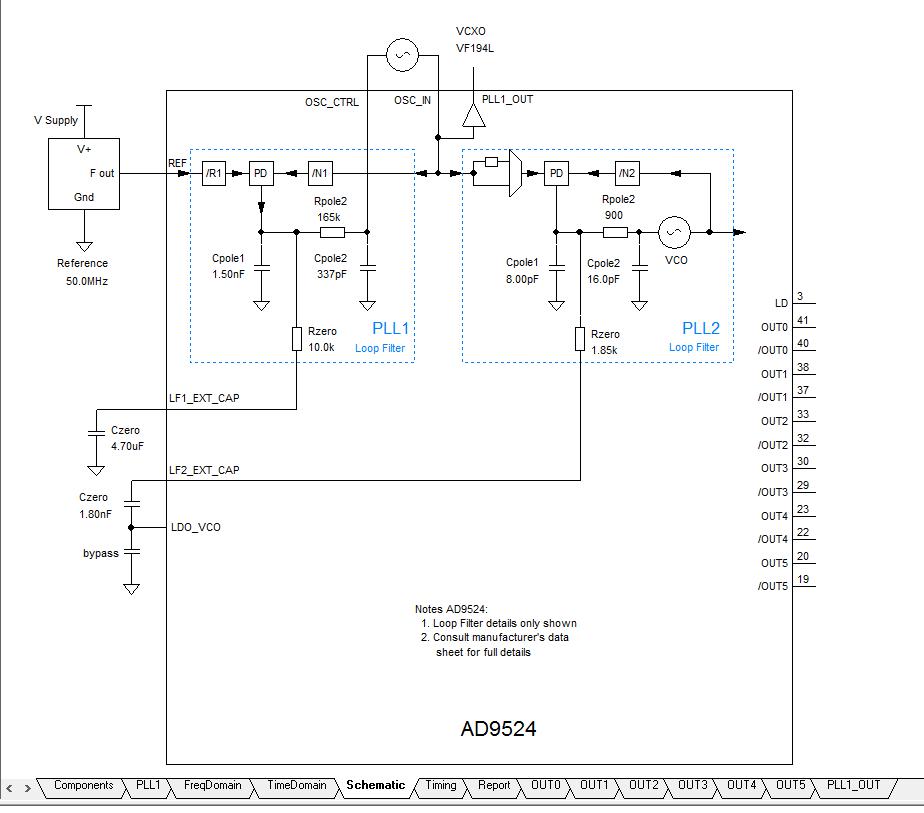

其中,根据 ADIsimCLK1.70 确定了环路滤波器PLL1和PLL2的各项参数:

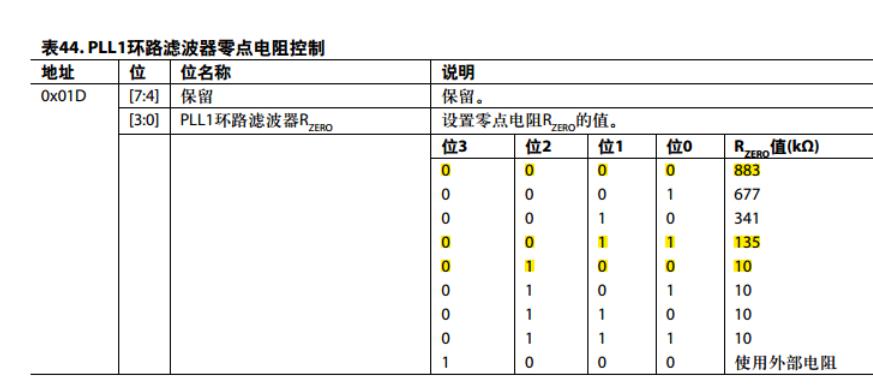

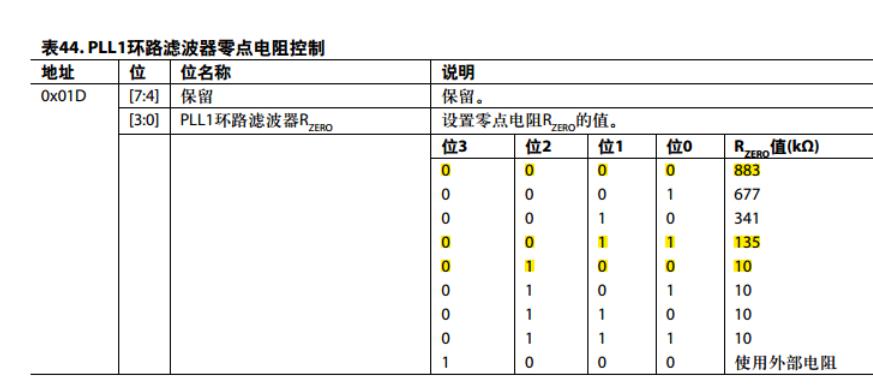

根据图中的PLL1和PLL2环路滤波器系数,去配置相应的寄存器:0x0F5: 0x39和0x01D: 0x04

然后当回读0x22c寄存器为0xe7时:

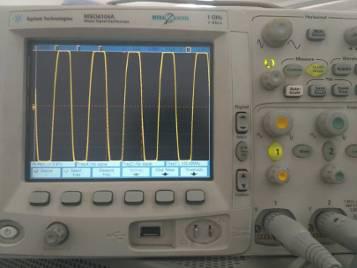

可以知道回读的状态是正确的,然后用示波器差分探头去测四路时钟输出情况,均是无规则的无周期性质的信号,类似于白噪声。

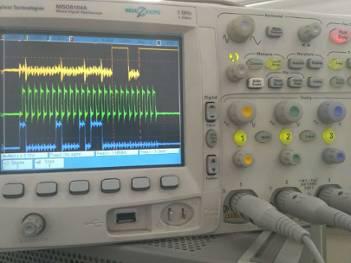

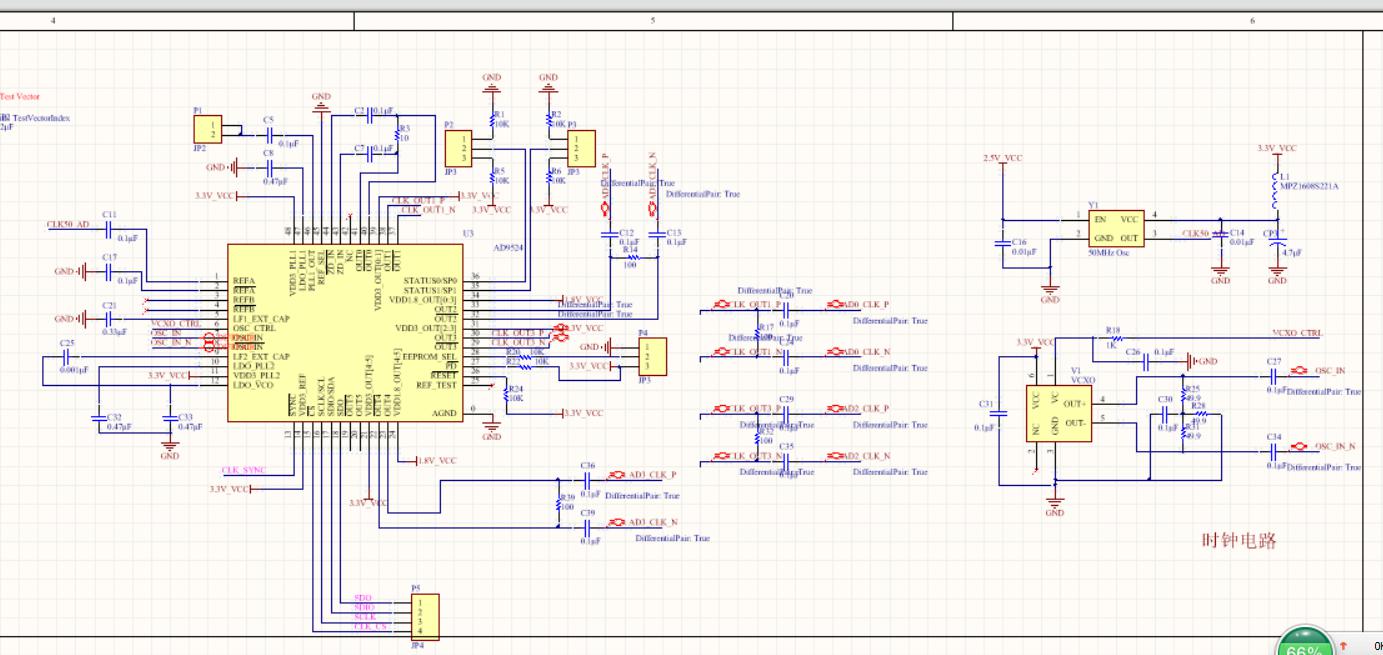

然后我也测了引脚9 (LF2_EXT_CAP) 和 引脚12 (LDO_VCO)两个引脚的电平情况,根据我原理图设计中可以看出,就是电容C25两测的信号:

但是靠近引脚9 (LF2_EXT_CAP)的信号是1.2V稳定电平,靠近 引脚12 (LDO_VCO)的信号是2.5V稳定电平,用示波器测的时候两个引脚处的电平虽然稳定,但带有噪声。

你好,我对环路滤波器进行了设置。

其中,根据 ADIsimCLK1.70 确定了环路滤波器PLL1和PLL2的各项参数:

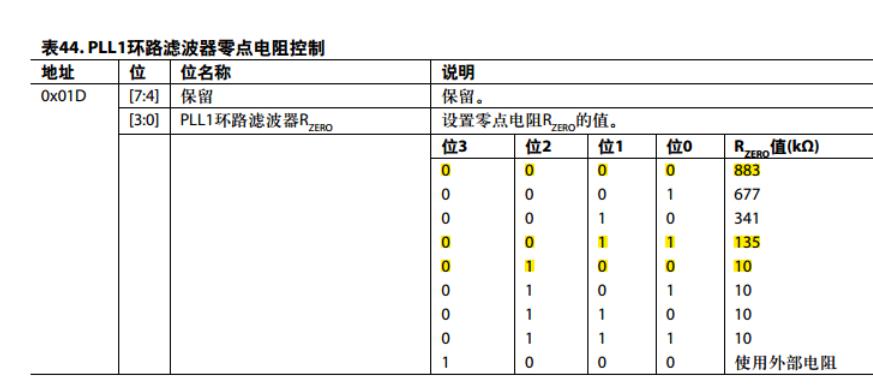

根据图中的PLL1和PLL2环路滤波器系数,去配置相应的寄存器:0x0F5: 0x39和0x01D: 0x04

然后当回读0x22c寄存器为0xe7时:

可以知道回读的状态是正确的,然后用示波器差分探头去测四路时钟输出情况,均是无规则的无周期性质的信号,类似于白噪声。

然后我也测了引脚9 (LF2_EXT_CAP) 和 引脚12 (LDO_VCO)两个引脚的电平情况,根据我原理图设计中可以看出,就是电容C25两测的信号:

但是靠近引脚9 (LF2_EXT_CAP)的信号是1.2V稳定电平,靠近 引脚12 (LDO_VCO)的信号是2.5V稳定电平,用示波器测的时候两个引脚处的电平虽然稳定,但带有噪声。

举报

举报

举报

举报

举报

举报