FPGA开发过程中,对设计好的模块进行仿真可以更详细地了解模块运行时的时序逻辑,帮助开发者更好地了解模块的运行,为后续的模块调试和优化提供依据。Lattice的FPGA开发工具Diamond配套有ModelSim软件用于FPGA的模块仿真

软件安装

ModelSim仿真软件随着Diamond一同安装,软件的安装和证书申请流程很简单可以参考电子森林Lattice Diamond教程

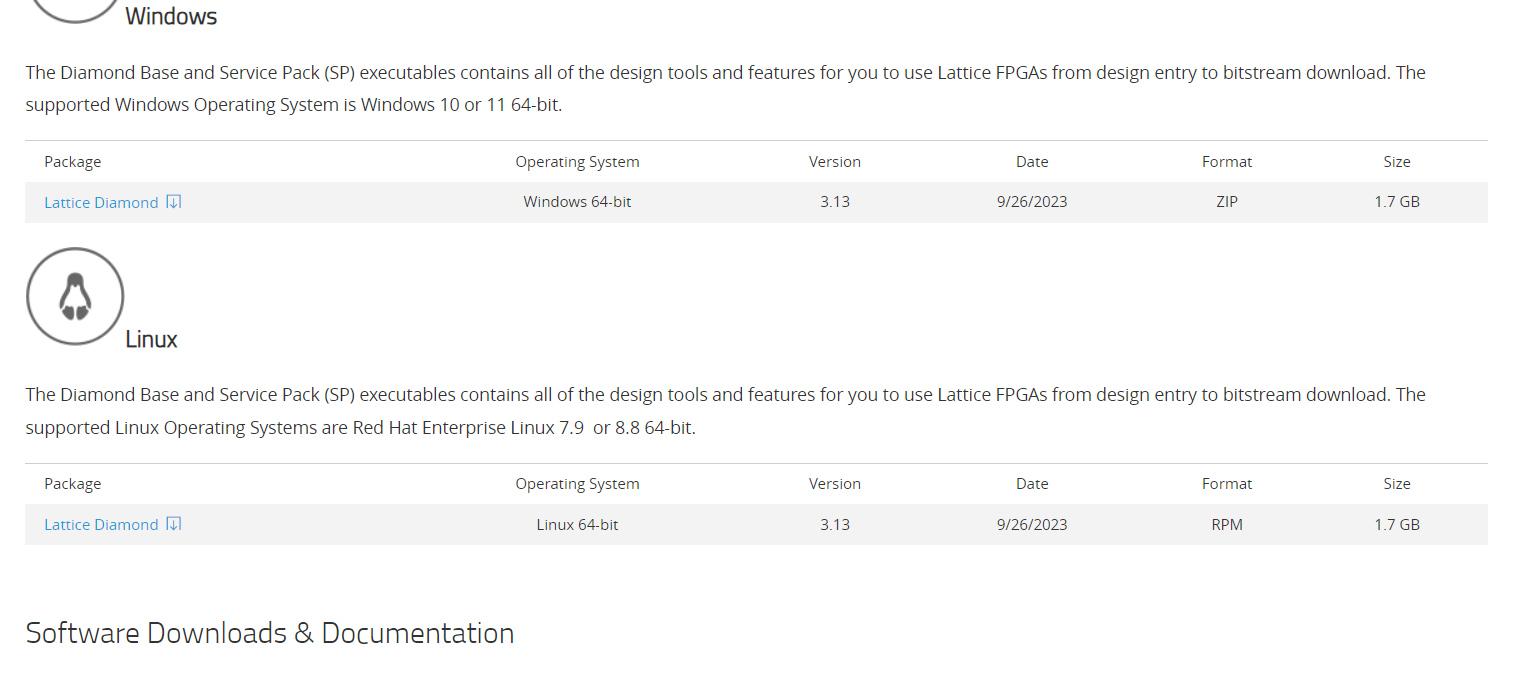

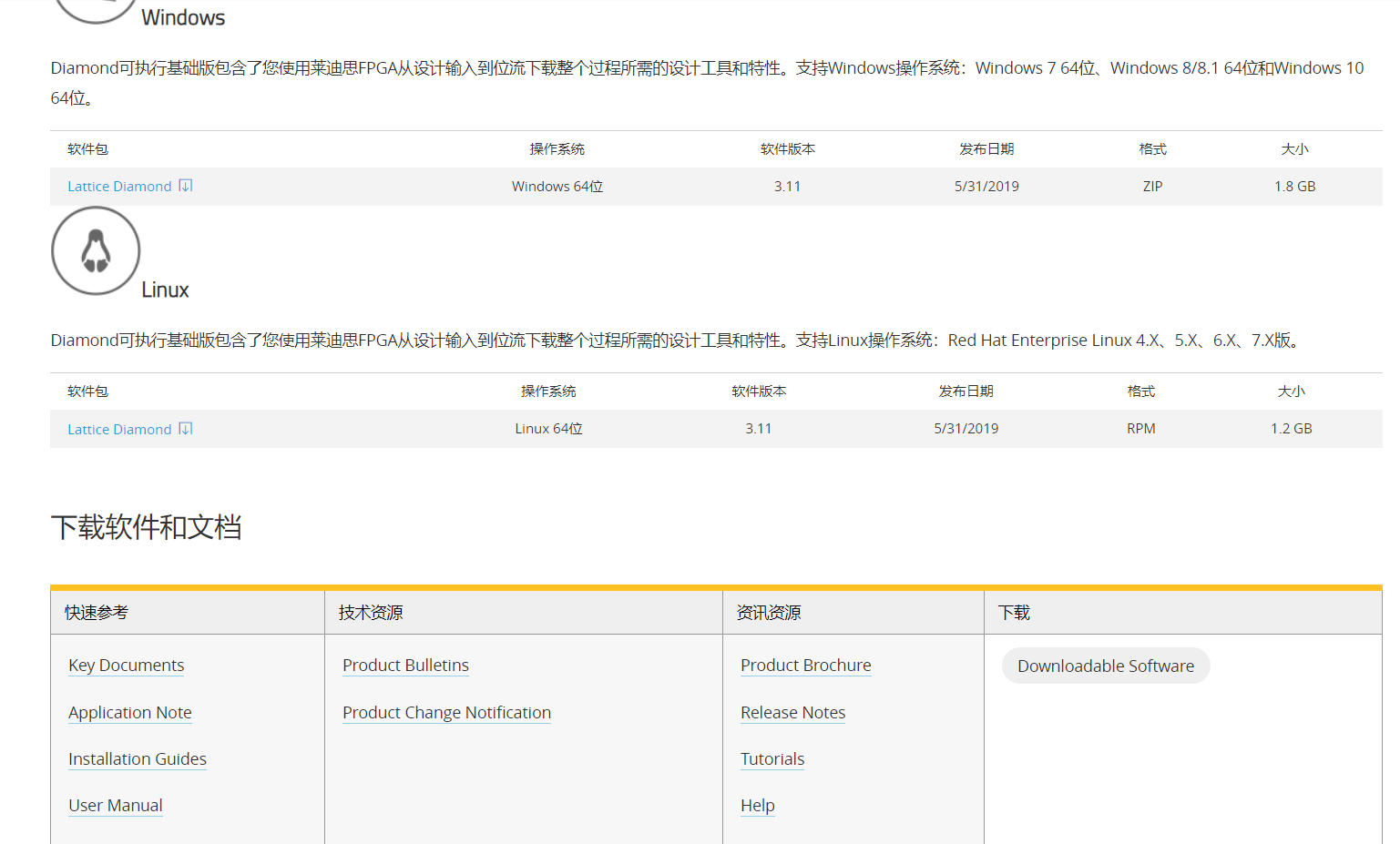

注意:使用仿真功能时需要使用Lattice的3.13版本,3.10版本使用的仿真工具为Active HDL,在申请的证书中包含的仿真工具为ModelSim,这会导致使用3.10时由于没有Active HDL的证书而无法进行仿真。值得一提的是,在中文官网和英文官网,Diamond提供的版本号不同,下载时要选择正确的软件版本。

模块仿真的基础步骤

参考Lattice创建FPGA工程,创建一个0.5s翻转LED的控制模块,实现LED闪烁的功能。模块的设计代码如下

module LED_Shining (

input clk,

input rst_n,

output led1,

output led2

);

parameter CNT_1S = 12_000_000 - 1;

parameter CNT_05S = CNT_1S >> 1;

reg [23:0] cnt;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) cnt <= 1'b0;

else if (cnt >= CNT_1S) cnt <= 1'b0;

else cnt <= cnt + 1'b1;

end

wire clk_div = (cnt>CNT_05S)? 1'b1 : 1'b0;

assign led1 = clk_div;

assign led2 = ~clk_div;

endmodule

接下来设计仿真使用到的Test Bench模块,其设计代码如下

`timescale 1ns / 100ps

module LED_shining_tb;

parameter CLK_PERIOD = 10;

reg clk;

initial clk = 1'b0;

always

reg rst_n; //active low

initial begin

rst_n = 1'b0;

rst_n = 1'b1;

end

wire led1,led2;

LED_Shining

.clk ( clk ),

.rst_n ( rst_n ),

.led1 ( led1 ),

.led2 ( led2 )

);

endmodule

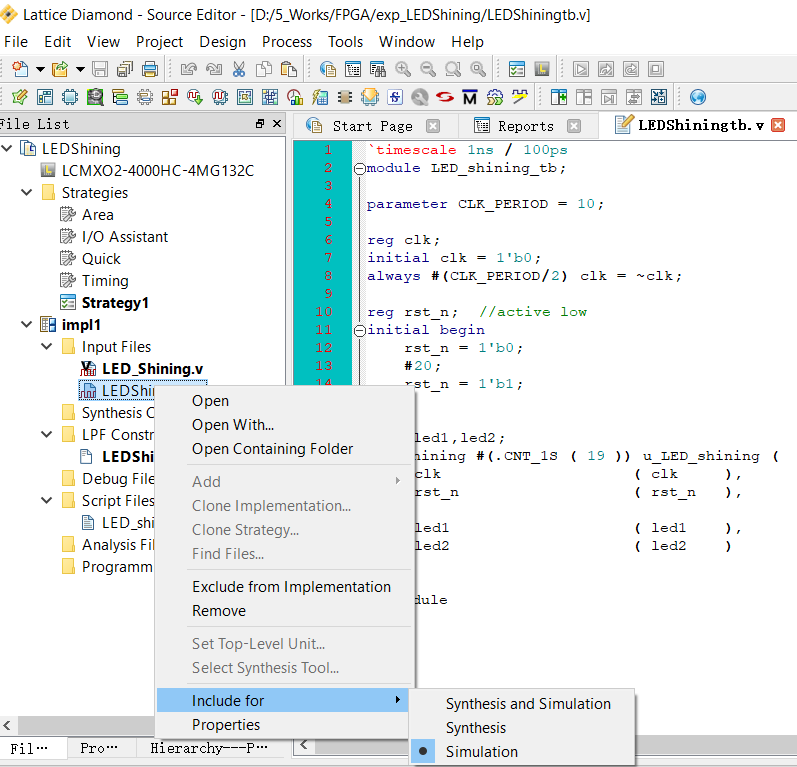

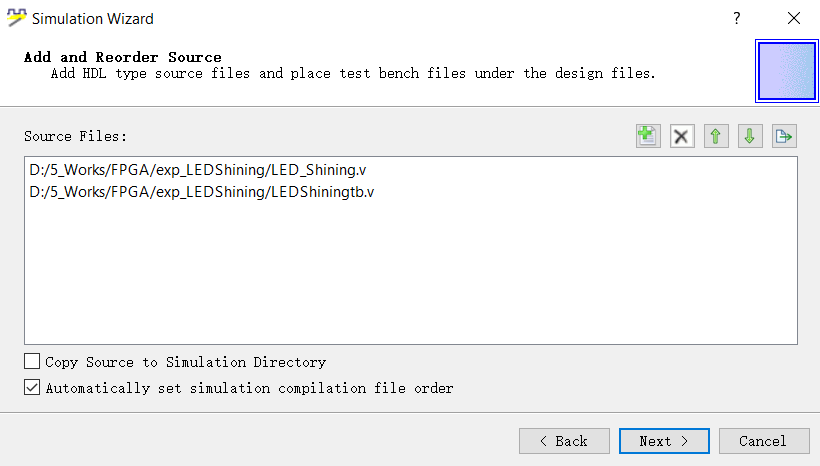

保存后,在工程的文件树中选择设计的测试模块(这里为LED_shining_tb.v),将其包含在“Simulation”选项中。

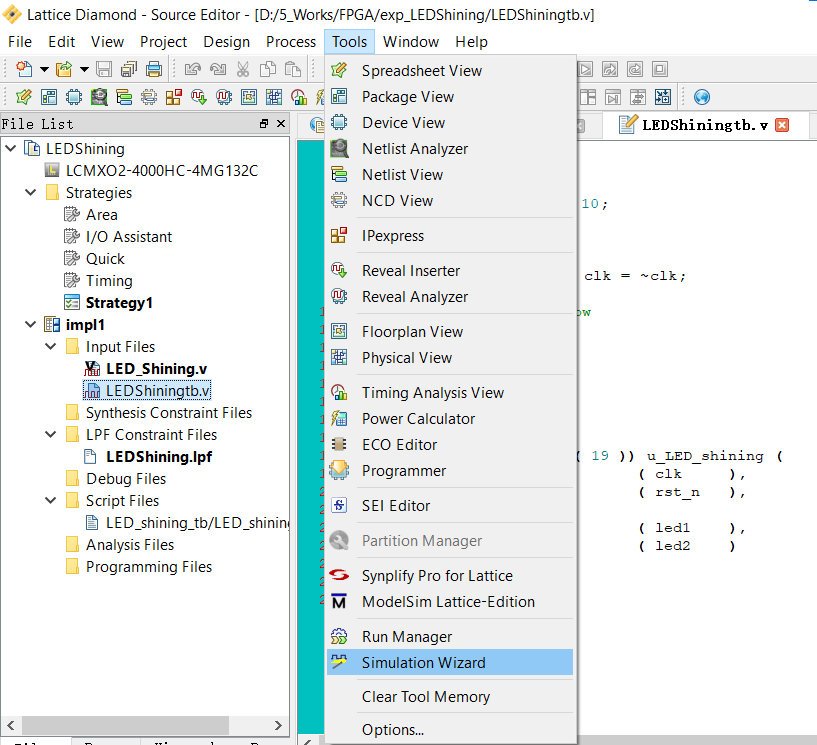

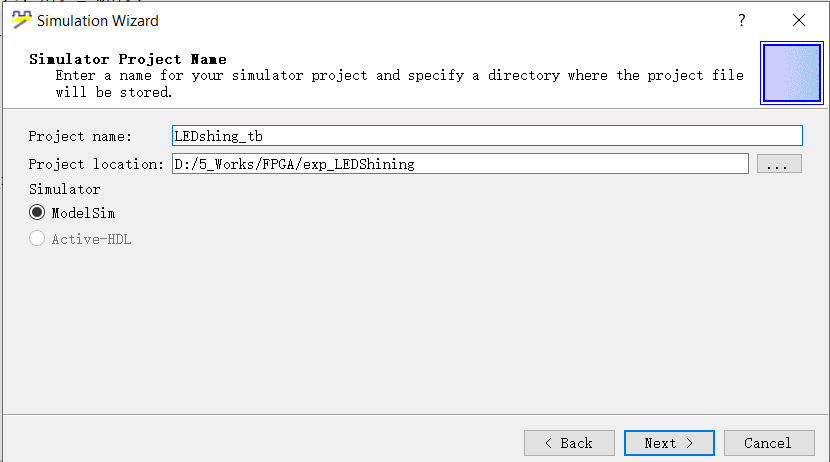

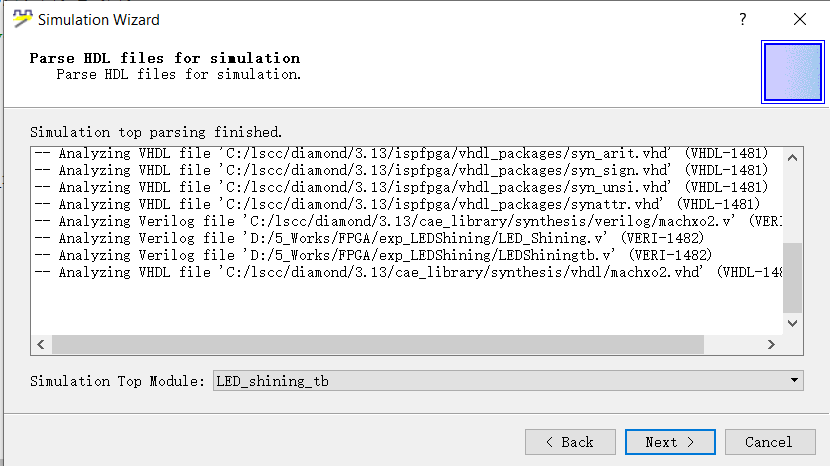

在Diamond的Tool->Simulation Wizard进入仿真配置界面。

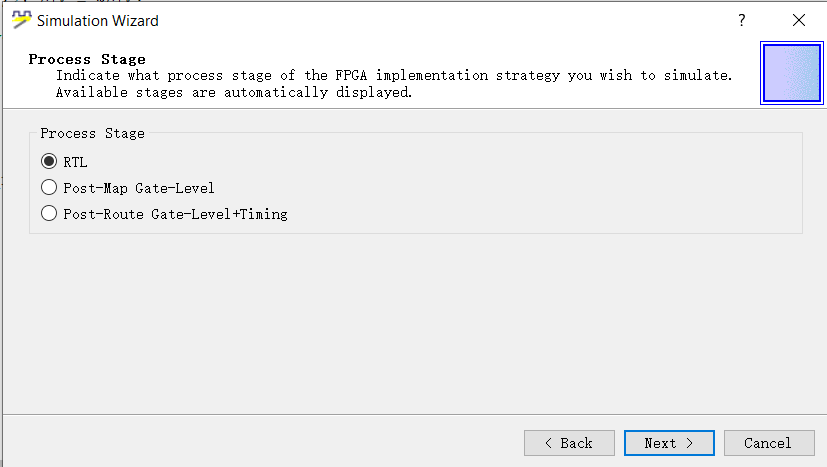

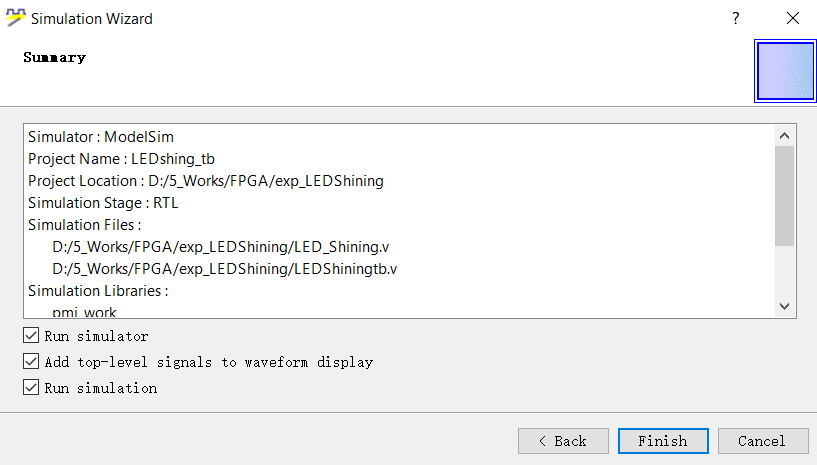

打开配置工具后,根据页面提示,设定仿真的工程名、仿真顶层模块等信息。

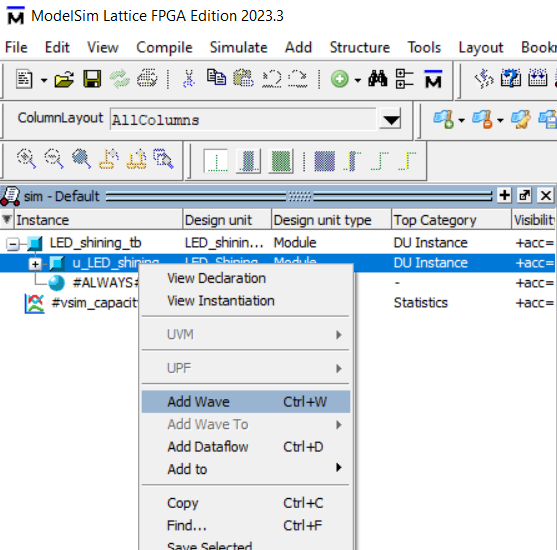

保存后,会在工程的文件树中产生一个.spf文件,其中保存了相关的配置参数,可以用于之后的重复仿真。在配置完成的界面点击Finish后,会自动进入ModelSim软件中进行模块仿真。在仿真界面中,可以将模块的输入输出添加到监视界面,便于进行模块的程序逻辑分析。

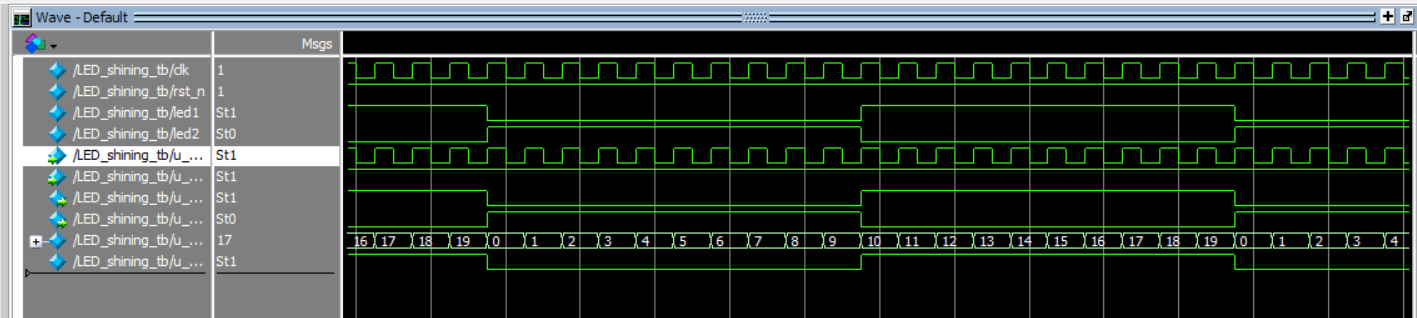

设定仿真的运行时间后,点击运行,可以得到模块的仿真结果。

从仿真结果中可以看到控制LED1和LED2的引脚以20个时钟为周期,周期性地进行翻转,从而实现LED的闪烁。