本文介绍使用盘古1KFPGA开发板的按键、拨码开关以及数码管实现密码锁实验。

实验的要求为:

- 利用拨码开关设置密码,使用按键输入开锁密码。当开锁密码与设定密码相同时开锁成功,数码管显示8888,密码错误时显示7777。

- SW1- SW4 设置2 位数密码,每两位设置一位密码,BM[0:1]设置第一位对应BM1 和BM2,BM[2:3]设置第二位。所以密码是由0,1,2,3 组成的四位数。

- KEY1-KEY2 作为密码输入,按键按一下数字加1,数字由数码管显示,数字在0,1,2,3 中循环。

- K4 作为确认按键,按下K4,输入的密码与设置的密码比对,如相同则显示8888,若不同则显示7777。按下K3 清零,按下后数码管显示0000,可以重新输密码。

硬件介绍

本实验中使用到外设的原理和基本使用方法在下面的帖子中做了详细的介绍

Verilog设计

本次实验要实现的一个核心功能是实现密码的比较功能,在开发板上的拨码开关可以作为一个密码来源,一个拨码开关有两种状态,在数字电路中可以表示为0或1,四个拨码开关最多可以表示16中不同的状态。这里以两个拨码开关的状态决定一个密码的数字(0,1,2,3)。拨码开关的状态的判断与按键的状态读取相同。数码管上显示的数字可以根据按键模块的计数值来决定。

可以设计比较模块如下

`timescale 1ns / 1ps

`define UD #1

module compare(

input clk,

input [3:0] sw,

input [3:0] ctrl,

input enter_trig,

output com_result

);

reg [3:0] ctrl_1d;

always @(posedge clk)

begin

if(enter_trig)

ctrl_1d <= `UD ctrl;

end

assign com_result = (ctrl_1d == sw);

endmodule

通过对比按键计数模块的计数值和拨码开关的状态,相同则控制数码管显示为8888,不同则显示7777。

上述设计中由于数码管智能处在显示输入密码的状态,显示比较结果状态,可以通过一个状态位来控制数码管的显示状态,结合数码管的显示模块,可以设计数码管的显示模块如下:

`timescale 1ns / 1ps

`define UD #1

module seq_display(

input clk,

input enter_trig,

input init_trig,

input com_result,

input [3:0] ctrl,

output reg [7:0] smg,

output reg [3:0] dig

);

//============================================================================

//显示状态区分

reg seq_status= 1'b0;

always @(posedge clk)

begin

if(enter_trig)

seq_status <= `UD 1'b1; else if(init_trig) seq_status <= `UD 1'b0;

end

//============================================================================

//数码管显示荣控制

reg [3:0] key0_cnt=4'd0,key1_cnt=4'd0,key2_cnt=4'd0,key3_cnt=4'd0;

always @(posedge clk)

begin

if(seq_status)

begin

if(com_result)

begin

key0_cnt <= `UD 4'd8; key1_cnt <= `UD 4'd8;

key2_cnt <= `UD 4'd8; key3_cnt <= `UD 4'd8;

end

else

begin

key0_cnt <= `UD 4'd7; key1_cnt <= `UD 4'd7;

key2_cnt <= `UD 4'd7; key3_cnt <= `UD 4'd7;

end

end

else

begin

key0_cnt <= `UD {2'd0,ctrl[1:0]}; key1_cnt <= `UD {2'd0,ctrl[3:2]};

key2_cnt <= `UD 4'd0; key3_cnt <= `UD 4'd0;

end

end

/*===================================================

时钟分频

===================================================*/

wire clk_1khz;

div_clk div_clk

(

.clk (clk),

.clk_1khz (clk_1khz)

);

/*===================================================

数码管显示

===================================================*/

reg [1:0]sel=0;

wire [3:0]dig0,dig1,dig2,dig3;

wire [7:0]smg0,smg1,smg2,smg3;

always @(posedge clk_1khz)

begin

sel <= `UD sel+1'b1;

end

seq_control seq_control_0

(

.sel(2'd3),

.key(key0_cnt),

.dig(dig0),

.smg(smg0)

);

seq_control seq_control_1

(

.sel(2'd2),

.key(key1_cnt),

.dig(dig1),

.smg(smg1)

);

seq_control seq_control_2

(

.sel(2'd1),

.key(key2_cnt),

.dig(dig2),

.smg(smg2)

);

seq_control seq_control_3

(

.sel(2'd0),

.key(key3_cnt),

.dig(dig3),

.smg(smg3)

);

always @(posedge clk_1khz)

begin

if(sel==2'b00)

dig <= `UD dig0; else if(sel==2'b01) dig <= `UD dig1;

else if(sel==2'b10)

dig <= `UD dig2; else if(sel==2'b11) dig <= `UD dig3;

end

always @(posedge clk_1khz)

begin

if(sel==2'b00)

smg <= `UD smg0; else if(sel==2'b01) smg <= `UD smg1;

else if(sel==2'b10)

smg <= `UD smg2; else if(sel==2'b11) smg <= `UD smg3;

end

endmodule

综上,设计顶层模块如下:

`timescale 1ns / 1ps

`define UD #1

module lock_top(

input clk,

input [1:0] key,

input enter,

input init,

input [3:0] sw,

output [7:0] smg,

output [3:0] dig

);

wire enter_trig;

wire init_trig;

wire [3:0] ctrl;

wire com_result;

key_ctl key_ctl(

.clk ( clk ),//input clk,

.key ( key ),//input [1:0] key,

.enter ( enter ),//input enter,

.init ( init ),//input init,

.enter_trig ( enter_trig ),//output enter_trig,

.init_trig ( init_trig ),//output init_trig,

.ctrl ( ctrl ) //output [3:0] ctrl

);

compare compare(

.clk ( clk ),//input clk,

.sw ( sw ),//input [3:0] sw,

.ctrl ( ctrl ),//input [3:0] ctrl,

.enter_trig ( enter_trig ),//input enter_trig,

.com_result ( com_result ) //output com_result

);

seq_display seq_display(

.clk ( clk ),//input clk,

.enter_trig ( enter_trig ),//input enter_trig,

.init_trig ( init_trig ),//input init_trig,

.com_result ( com_result ),//input com_result,

.ctrl ( ctrl ),//input [3:0] ctrl,

.smg ( smg ),//output reg [7:0] smg,

.dig ( dig ) //output reg [3:0] dig

);

endmodule

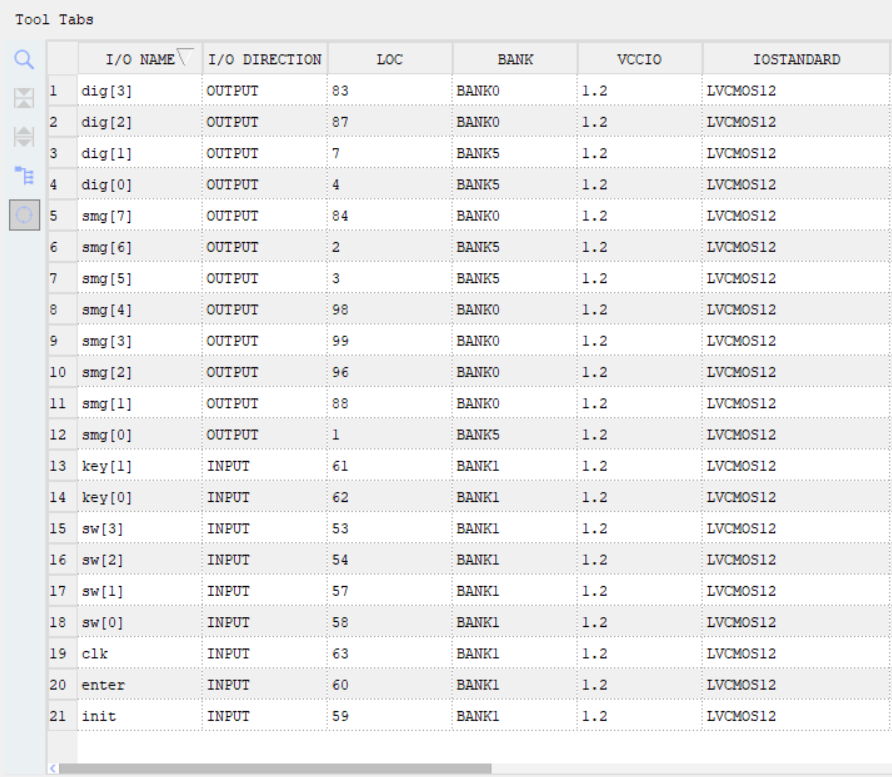

添加引脚约束如下

实验的显示效果如下