|

RISC-V 发展

2015年成立了RISC-V基金会,这是个非营利性组织,主要为了维护和发展RISC-V。

目前RISC-V的IP供应商大部分是国内的厂商,例如sifive、阿里平头哥、Andes等等。而基于RISC-V架构设计的芯片厂商也基本是国内的。

可见,基于RISC-V架构设计的芯片,没有了像ARM需要授权等多方面的限制,可以做到自主可控。但由于RISC-V还处于发展的阶段,还有许多不完善的地方,有传言未来可能会形成x86、ARM、RISC-V三足鼎立的天下,但能够形成这个局面,还需要大家的共同努力。

RISC-V指令集

RISC-V指令集由“基本指令集 + 扩展指令集”组成。基本指令集是必选的,扩展指令集是可选的。意思就是可以根据你的实际需求,选择需要使用的指令。例如在一个项目中,如果不需要用到压缩指令,那么就不需要把压缩指令添加进来,从而做到定制化,这也是RISC-V的一大特点。

RISC-V指令集有RV32I、RV32E、RV64I、RV64E、RV64I等等,RV代表RISC-V,32/64代表32位或64位,I和E都是基本指令集,在I和E的基础上,可以添加D(双精度浮点扩展)、M(整数乘除法)、A(原子扩展)、C(压缩扩展)等扩展指令。例如,在RV64I基础上,添加原子、整数乘除法、双精度浮点、压缩指令,则该指令集称为RV64IMADC。

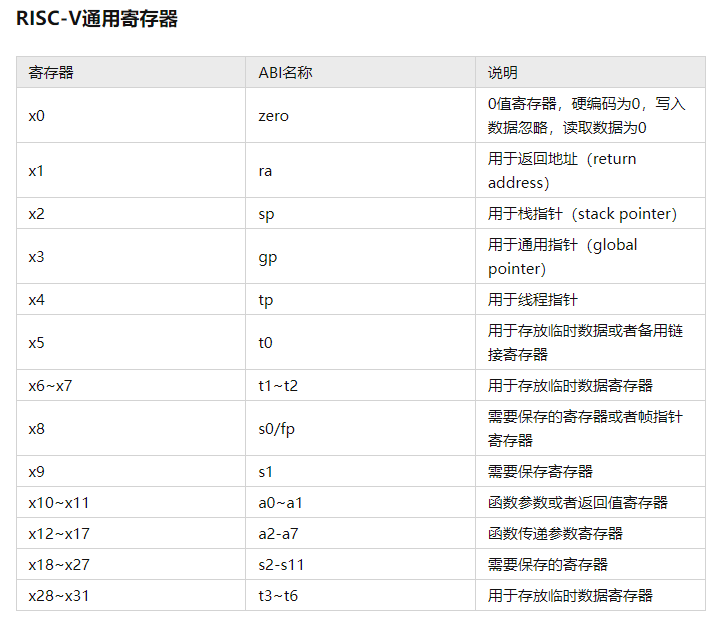

RISC-V有x0-x31共32个通用寄存器,每个通用寄存器都有各自的用途。例如x2是作为sp栈指针、a0-a1用来保存函数参数或返回值。x0寄存器被硬编码为了0,就是个0值寄存器。

ABI名称相当于这些通用寄存器的别名,在RISC-V汇编当中,都使用ABI名称来代表这些寄存器。

RISC-V CSR寄存器

CSR是控制状态寄存器,RISC-V中CSR寄存器,需要使用csrr、csrw、csrrw等特定指令进行访问。

RISC-V的CSR寄存器,M模式和S模式都有自己的寄存器,但是大体上相同。

|