A-Prolifile构架中的Performance Monitoring Unit(PMU)和Activity Monitoring Unit(AMU)都具有性能计数器。AMU和PMU可以计数的事件类似,那么AMU和PMU有什么不同呢?

AMU和PMU的区别在于:

AMU和PMU用作不同用途

AMU和PMU有不同的编程模式

不同的用途

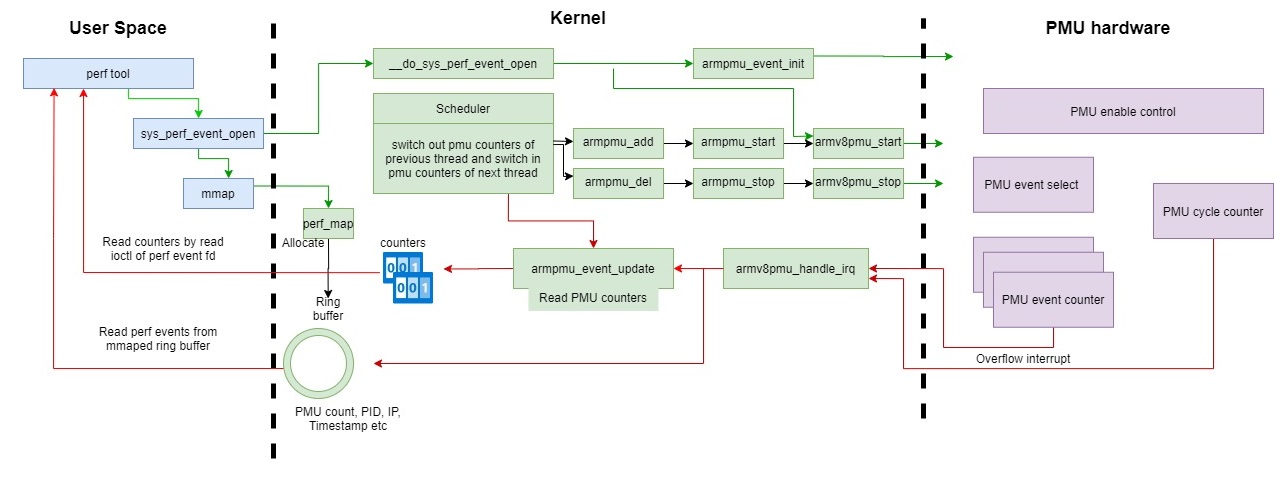

PMU的用途是性能分析和调试。PMU提供了一序列的事件计数,如cache miss, TLB miss,CPU cycle,已经执行的指令数,用来做性能分析和调试。PMU可以被如Linux perf tool, arm DS-5/arm DS等性能分析工具利用。

虽然构架上定义了一系列的通用事件,每个CPU实现可以定义它特用的事件。可以参考Arm Architecture Reference Manual Armv8, for Armv8-A architecture profile和CPU处理器手册的PMU事件和事件号码章节获得更多PMU事件的信息。

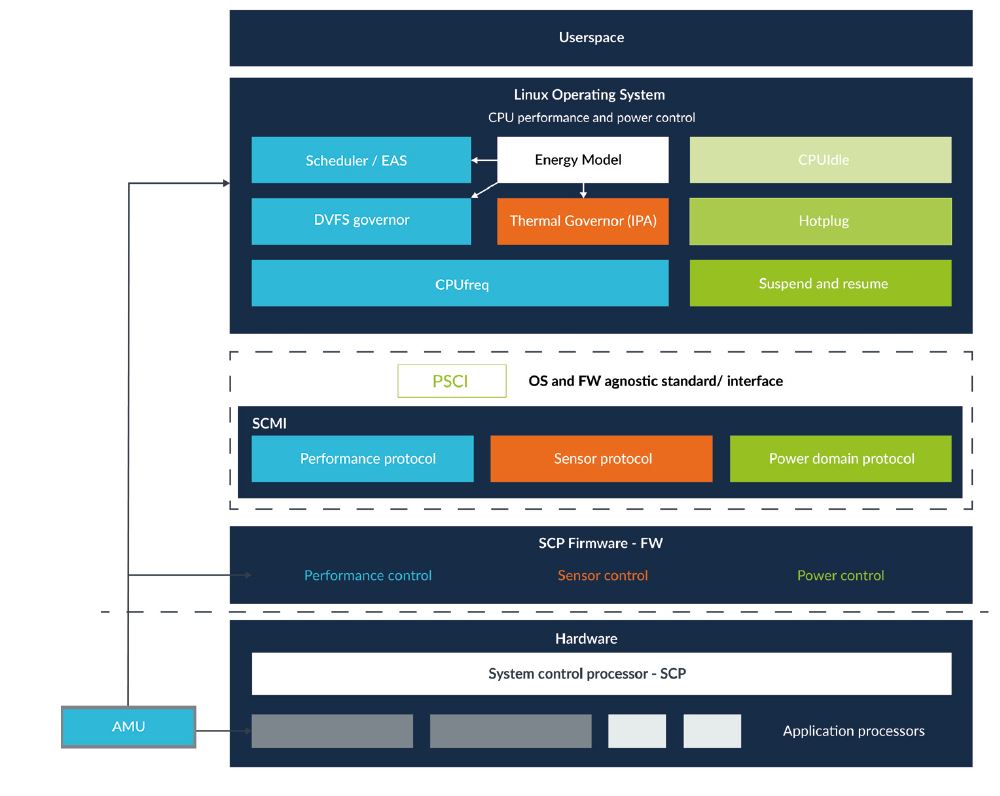

AMU的用途是系统管理和监控,特别是功耗和性能管理。例如,可以使用AMU计数器作为CPU处理器活跃度信息来帮助DVFS的调节。

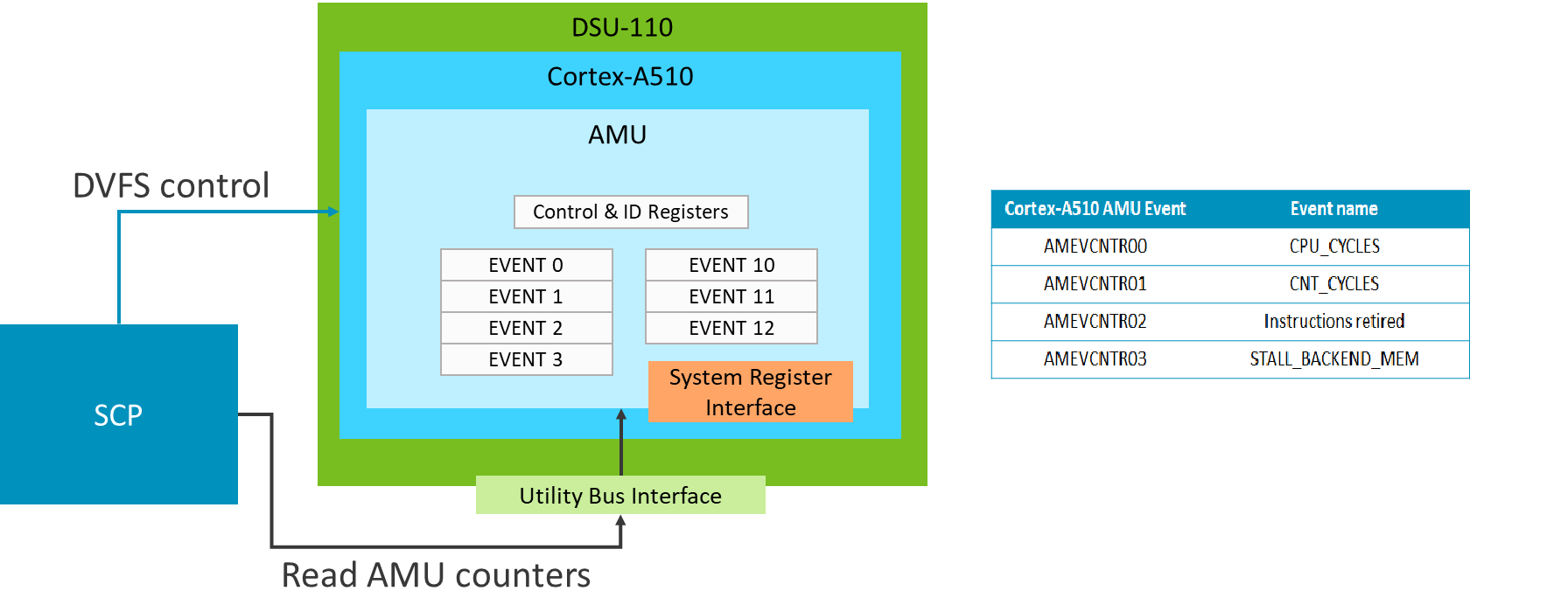

AMU提供了少数的简单,固定的,free-running的计数器。AMUv1包括下列事件计数器:

• 4个构架规定的64-bit事件计数器

CPU cycle计数器,它以CPU的频率递增

常量计数器,它以system counter的固定频率递增

退役指令(Instructions retired), 它计数每条构架意义上执行过的指令(non speculative)

内存暂停周期数(Memory stall cycles),它计数由于在同一clock domain中的最后一级cache中miss导致的指令分发暂停周期数(instruction dispatch stall cycles)

• 多至16个的附加64-bit事件计数器

这些计数器计数一个附加的事件。取决于CPU处理器的实现,计数的事件可以是固定的,或是可编程的。

Cortex-A510的例子:

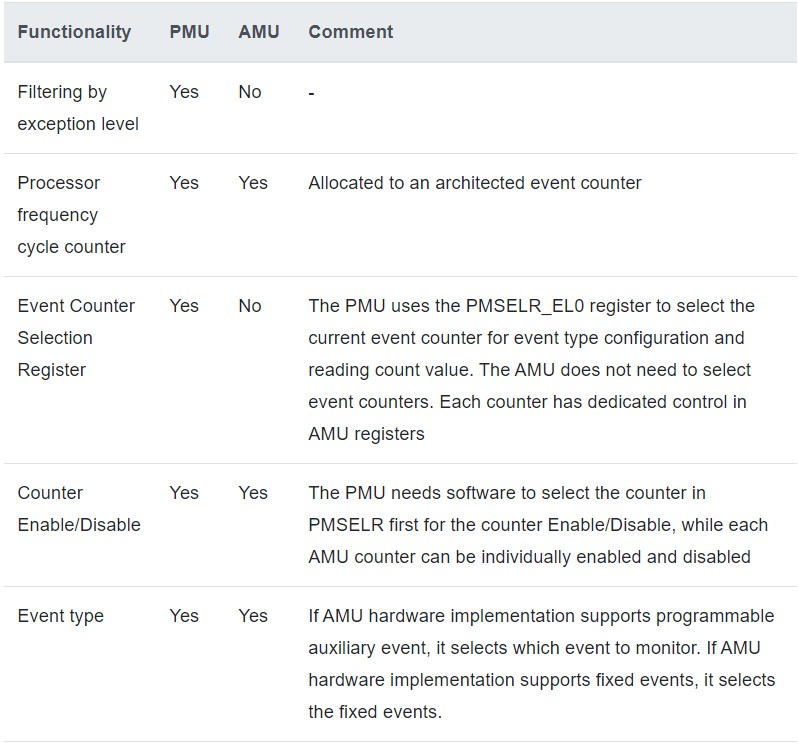

不同的编程模式

相较于PMU,AMU缩减了功能集,并降低了事件选择的自由度。

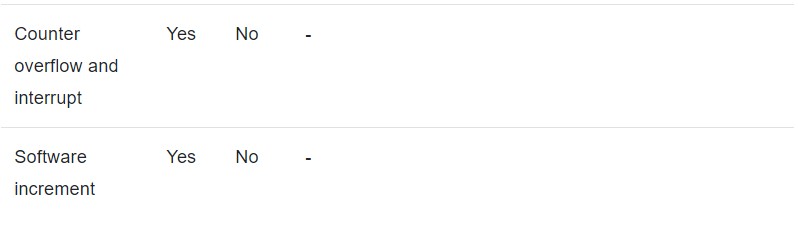

以下表格比较了PMU和AMU支持的功能

PMU的编程

软件通过以下步骤来编程PMU事件计数器

1 在Performance Monitors Control Register (PMCR)中使能PMU

2 配置一个事件计数器

将你想使用的事件计数器号码设置到Performance Monitors Event Counter Selection Register (PMSELR) PMSELR.SEL bit

将你想计数的事件的号码设置到Performance Monitors Event Type Select Register (PMXEVTYPER) PMXEVTYPER.evtCount, 来设置上面的事件计数器观测的事件

3 在Performance Monitors Count Enable Set Register (PMCNTENSET)中使能配置好的事件计数器

AMU的编程

相较于PMU,AMU因为有更少的事件而具有更简单的编程模式。

计数构架定义事件的计数器是固定的,因而event type registers, AMEVTYPER0_EL0是只读的。

附加的64-bit事件计数器是通过AMEVCNTR1_EL0来访问的。每个计数器计数那种事件,这些事件是固定的还是可以通过event type registers编程的由CPU硬件实现决定。因而AMEVTYPER1_EL0可能是只读的或是可读写的。

AMU不采用PMU PMSELR寄存器选择要观测事件的方式。

采用以下方式编程一个AMU事件计数器:

1 使能和禁止计数器

每个计数器可以单独使能或禁止

构架定义的计数器通过设置AMCNTENSET0_EL0相应bit使能,通过设置AMCNTENCLR0_EL0相应bit禁止

附加计数器的使能和禁止通过设置AMCNTENSET1_EL0和AMCNTENCLR1_EL0相应bit实现

2 读计数器值

构架定义事件计数器的计数器值通过读相应的AMEVCNTR0_EL0获取,而附加事件计数器的计数器值通过读相应的AMEVCNTR1_EL0寄存器获取。

原作者:修志龙_ZenonXiu

/7

/7