GD32F427 ENET以太网外设介绍

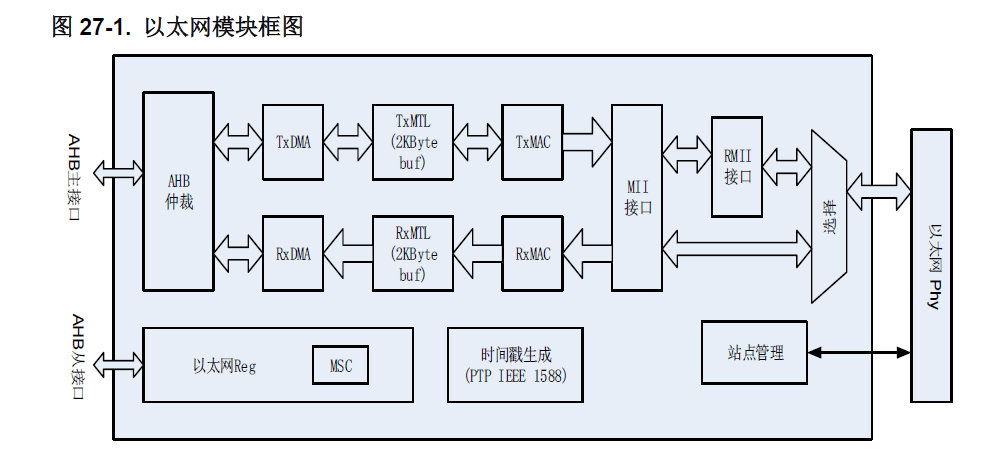

GD32F427芯片内自带了一个10/100M以太网控制器ENET,采用DMA优化数据帧的发送与接受提升性能,即MAC控制器通过DMA与CPU的内存SRAM可以直接进行数据传输。与串口或SPI接口的以太网模块相比,这可以极大的提升数据传输带宽。

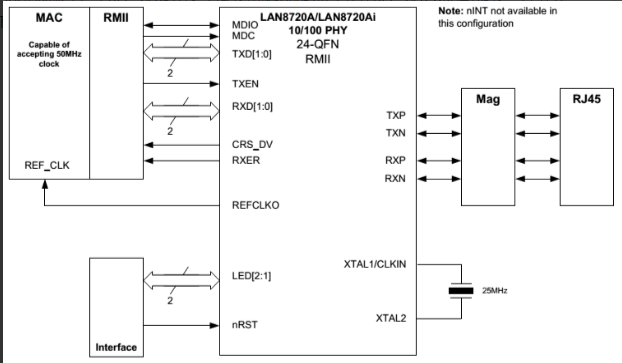

MAC控制器通过MII或RMII接口与外部PHY芯片连接,然后转换成RJ45可以连接到主机或路由器。

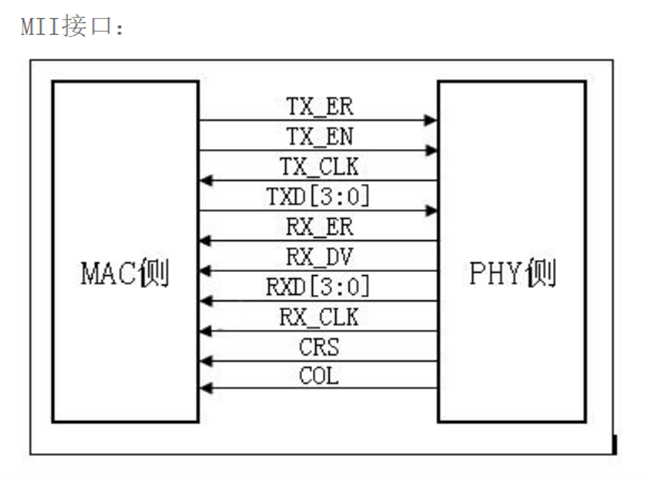

MII接口模式

当ENT工作在MII接口时,根据IEEE 802.3协议,Tx MAC和Rx MAC的时钟都是来自外部PHY,此时钟配置寄存器SYSCFG_CFG1为0,表示时钟遵从MII接口模式配置。

MII接口走线比较多,一般用的比较少。数据路径时钟频率分别是2.5MHz/25MHz。数据上升沿驱动。

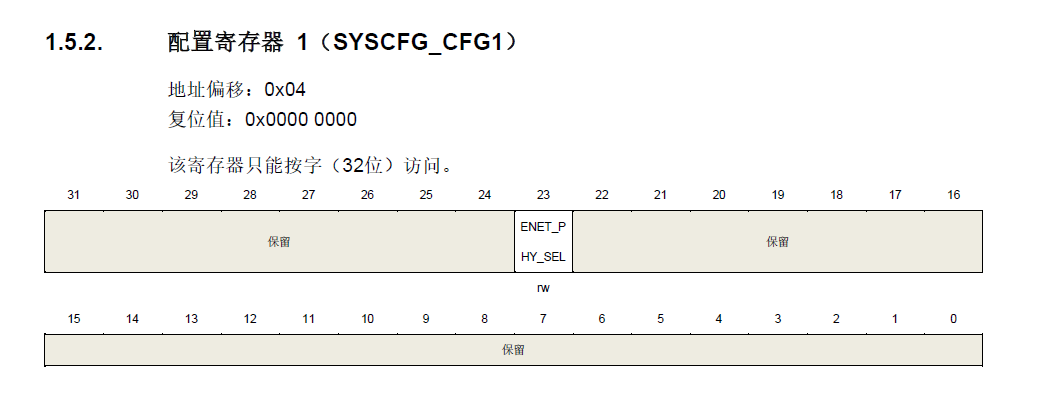

RMII接口模式

当ENET工作在RMII接口是,因为把数据bus从原来4bit减少到了2bit,所以总线上的时钟频率提升至50MHz,数据还是上升沿驱动;此时需要配置SYSCFG_CFG1对应的时钟选择配置ENET_PHY_SEL为1,此时时钟是由内部PLL的200MHZ进行分频得到50MHz和MAC控制器的25MHz,如果工作在10M,则MAC控制器的时钟为2.5MHz。

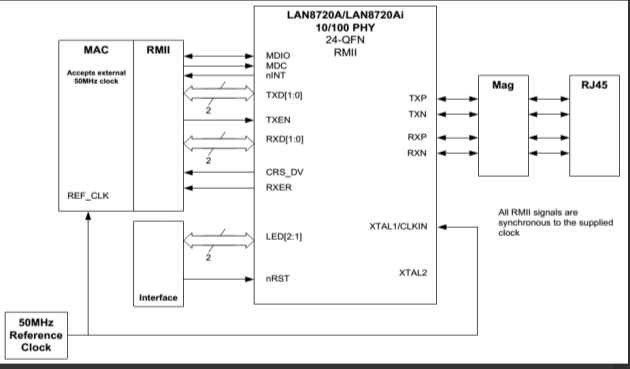

LAN8720 PHY芯片介绍

LAN8720是低功耗的10/100M以太网PHY层芯片,LAN8720支持通过RMII接口与以太网MAC层通信,内置10-BASE-T/100BASE-TX全双工传输模块,以下是其特点:

1、支持RMII接口以减少引脚数

2、支持全双工和半双工模式

3、可以使用25M晶振以降低成本

4、支持SMI串行管理接口( 遵从IEEE 802.3 Clause22 MDIO protocol )

5、支持MAC接口

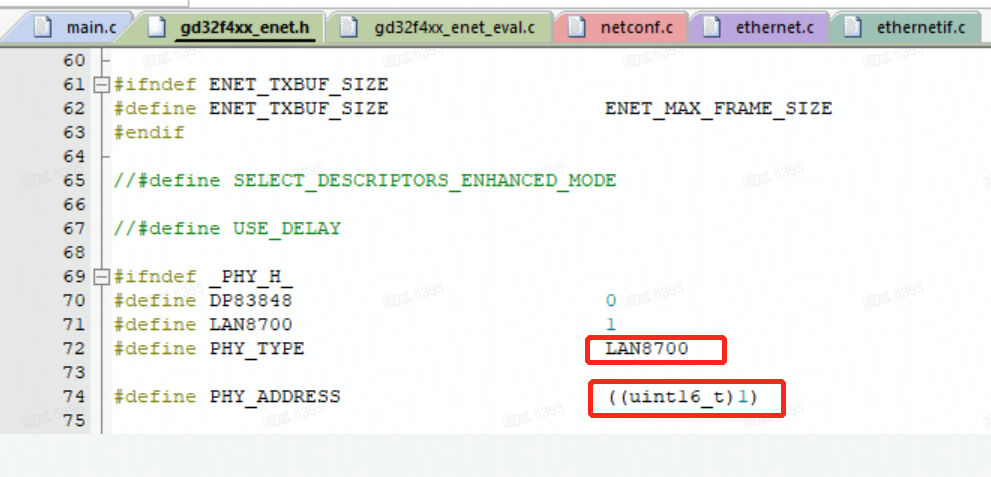

ENET可以通过SMI接口来读写PHY(LAN8720)的寄存器,SMI最多可以控制32个PHY芯片,通过不同的PHY芯片地址来对不同的PHY操作。LAN8720通过设置RXER/PHYAD0引脚来设置其PHY地址,默认情况下为0,也可以设置为1。

个人环境PHY地址为1,后面在固件种需要修改对应值。

nINT/REFCLKO配置

nINTSEL引脚(2号引脚)用于设置nINT/REFCLKO引脚(14号引脚)的功能。

nINTSEL为0表示REF_CLK Out模式,为1表示REF_CLK In模式。

REF_CLK In模式

当工作在REF_CLK In模式时,50MHz的外部时钟信号应接到LAN8720的XTAL1/CKIN引脚(5号引脚)和STM32F407的RMII_REF_CLK(PA1)引脚上,如下图所示。

REF_CLK Out模式

为了降低成本,LAN8720可以从外部的25MHz的晶振中产生REF_CLK时钟。到要使用此功能时应工作在REF_CLK Out模式时。当工作在REF_CLO Out模式时REF_CLK的时钟源如下图所示。

这里GD32F427的固件库已经提供了LAN8720的驱动,我们只需要修改头文件即可。

移植流程

1、硬件环境准备

首先,LAN8720与GD32F427开发板连接起来。需要连接TXD0 TXD1 TXEN RXD0 RXD1 RXD_DV REF_CLK和MDC/MDIO,一共9个接口,分别表示数据总线和管理通道。

然后,为了便于串口查看执行情况,使用usb转串口小板模块,将GD32F427的UART0接到PC机。

2、软件环境准备

使用了官方提供的ENET参考样例。

GD32F4xx_Firmware_Library_V3.0.2\GD32F4xx_Firmware_Library\Examples\ENET

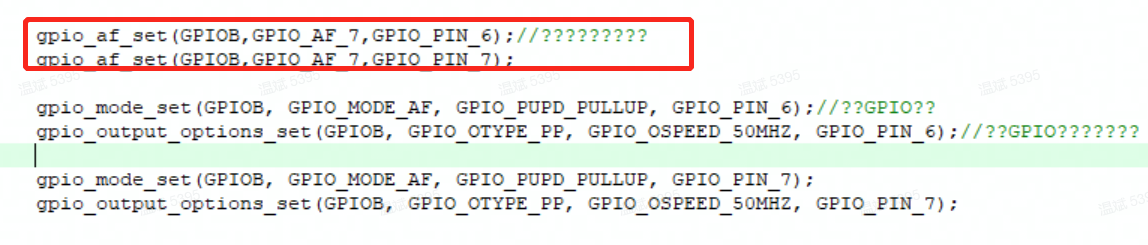

修改映射GD32F427开发板的UART0到PB6/PB7。

修改固件库头文件的PHY类型和PHY地址。

3、测试步骤

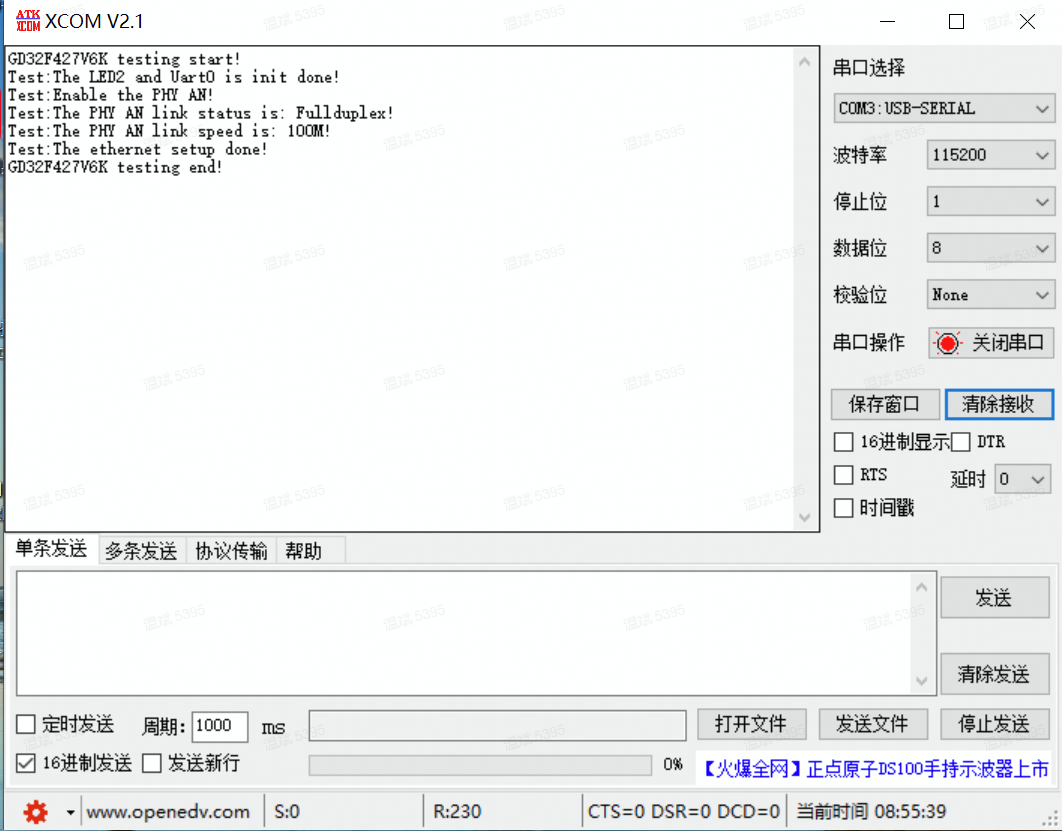

将LAN8720通过网线与路由器连接,启动AN自协商,固件去polling PHY的link状态,然后通过串口打印。

原作者:eillt

/7

/7