介绍

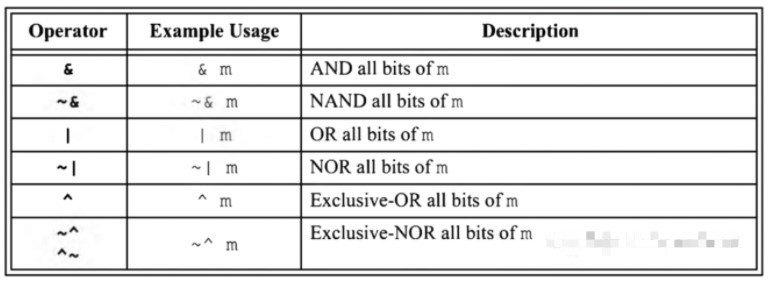

归约运算符对单个操作数的所有位执行运算,并返回标量(1位)结果。表5-9列出了归约运算符。

表5-9:RTL建模的归约运算符

归约运算符包括一个NAND和一个NOR运算符,这是按位运算符所没有的。归约AND OR 和 XOR 运算符一次执行一位操作,从最右边的位(最低有效位)向最左边的位(最高有效位)移动。归约NAND、NOR和XNOR运算符首先分别执行归约AND、OR或XOR运算,然后反转1位结果。

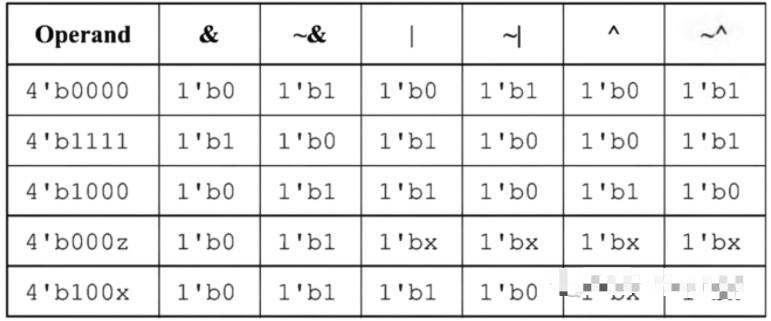

AND、NAND或NOR运算符是X-optimistic。对于归约运算符,如果操作数中的任何位为0,结果将为1’b0。对于归约NAND,如果操作数中的任何位为0,结果将为1’b1。类似地,对于归约运算符,或者如果操作数中的任何位为l,结果将为1’b1。对于归约NOR,如果操作数中的任何位为l,结果将是1’b0.归约XOR和XNOR运算符是X-pessimistic。如果操作数的任何一位是X或Z,结果将是1’bx。表5-10显示了几个示例值的每个归约运算符的结果。

表5-10:归约操作的示例结果

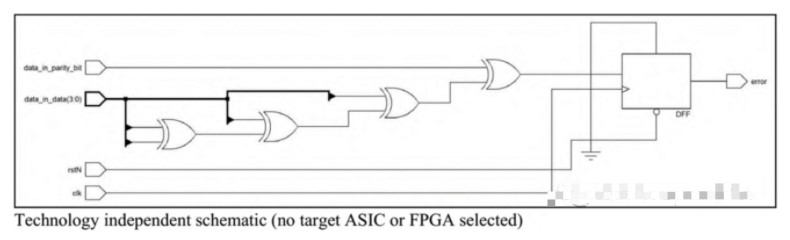

示例5-6说明了一个小型RTL模型,该模型利用归约运算符检查数据值的正确奇偶性,图5-6显示了该RTL模型综合结果。

示例5-6:使用归约运算符:使用异或的奇偶校验

`begin_keywords "1800-2012"

package definitions_pkg;

typedef struct {

logic [7:0] data;

logic parity_bit;

} data_t;

endpackage: definitions_pkg

`end_keywords

`begin_keywords "1800-2012"

module parity_checker

import definitions_pkg::*;

(input data_t data_in,

input clk,

input rstN,

output logic error

);

timeunit 1ns/1ns;

always_ff @(posedge clk, negedge rstN)

if (!rstN) error <= 0;

else error <= ^{data_in.parity_bit, data_in.data};

endmodule: parity_checker

`end_keywords

该文件的仿真文件如下:

`begin_keywords "1800-2012"

module test

import definitions_pkg::*;

(output logic rstN,

output data_t data_in,

input logic error,

input logic clk

);

timeunit 1ns/1ns;

initial begin

$timeformat(-9, 0, "ns", 6);

rstN <= 0;

repeat(2) @(negedge clk) ;

rstN = 1;

repeat (10) begin

@(negedge clk) ;

data_in.data = $urandom();

data_in.parity_bit = $urandom()%2;

@(negedge clk) check_results;

end

@(negedge clk) $finish;

end

task check_results;

$write("At %t: data=%b parity_bit=%b: ", $time, data_in.data, data_in.parity_bit);

if (^data_in.data === data_in.parity_bit) begin: good_data_in

$write("Good data_in. EXPECT: error = 0, ACTUAL: %b ", error);

if (error === 1'b0) $display(" OK");

else $display(" ERROR!");

end: good_data_in

else begin: bad_data_in

$write("Bad data_in. EXPECT: error = 1, ACTUAL: %b ", error);

if (error === 1'b1) $display(" OK");

else $display(" ERROR!");

end: bad_data_in

endtask

endmodule: test

`end_keywords

`begin_keywords "1800-2012"

module top;

timeunit 1ns/1ns;

import definitions_pkg::*;

parameter WIDTH = 8;

logic clk, rstN;

data_t data_in;

logic error;

test test (.*);

parity_checker dut (.*);

initial begin

clk <= 0;

forever #5 clk = ~clk;

end

endmodule: top

`end_keywords

图5-6:示例5-6的综合结果:归约异或(奇偶校验)

原作者:碎碎思

|  /6

/6