Arm与arm构架授权公司及生态伙伴一起,持续进行构架演化,开发满足现有和新市场产品需求的新构架特性。

这篇博客阐述了2021年A-Profile构架的新加关键特性。

完整的指令集和系统寄存器信息可以在arm开发网站developer.arm.com 上找到。

memcpy()函数家族的优化

memcpy()/memset()库函数家族在软件中被广泛使用。这些函数的高效实现是系统性能的一个关键因素。

在传统的RISC构架上实现这些memcpy操作的方式是使用标准指令,如load和store指令。这个方式的问题是优化过的指令系列的性能和很多因素有关,比如和微构架实现(注:不同的微构架可能需要使用不同的load/store指令来获得最佳的memcpy/memset性能,比如LDP/STP, 或是LDR/STR指令),操作的内存开始地址是不是对齐的,操作内存的大小有关。这意味着在众多memcpy这类库函数实现里挑选最优的一个很普遍。这增加了软件长期维护的代价(注:软件需要为不同的CPU微构架实现和不同大小,对齐或是非对齐内存地址,编写、挑选最优是memcpy()函数家族实现)。

针对这个问题,2021构架扩展引入了专门针对memcpy/memset家族函数的新指令

这使得软件开发者可以跨微构架,对齐和内存大小编写可移植的标准优化memcpy/memset函数实现(注:让CPU硬件自己来按最优的方式处理不同大小,对齐的内存操作)。对于硬件设计者来说,这些新指令是的检测memcpy/memset操作更加容易,并针对性地优化它们。

Non-Maskable Interrupts

以往的一些arm处理器,比如Cortex-R4,支持non-maskable interrupts (NMI),但是这不是标准的构架功能。在2021构架扩展中出现了变化,它在CPU和GIC构架中增加了NMI的支持。

GICv3.3构架增加了一个软件可以给中断分配的NMI属性。带NMI属性的中断会被当成当前安全状态下具有最高优先级的中断,具有不同的屏蔽(mask)和抢占规则:

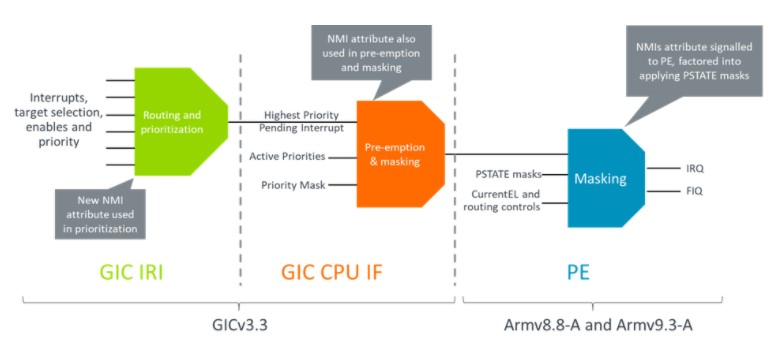

图1:在GIC和CPU中处理NMI

在CPU里面,NMI不受现有的PSTATE.I和PSTEAT.F屏蔽的控制。这使得NMI在大多数中断被屏蔽的情况下还可以产生中断异常。但是有些NMI的屏蔽还是有必要的,比如在中断进入和退出时阻止返回状态的破坏。因此,引入了一个新的屏蔽, PSTATE.AllInt,它可以用来屏蔽包括NMI的所有中断。软件也可以使用PSTATE.SP作为隐性的屏蔽。

Performance Monitoring Unit (PMU,性能观测单元)更新

PMU是帮助开发者理解他们跑在arm处理器上的代码性能的重要工具。

2021构架扩展增加了新的对cache line状态追踪的PMU events. 这些event可以用来观测cache预期的准确性。还有一些PMU event用来汇报cache命中时数据来自哪个cache level和类型。

有些PMU event可以每个cycle被增加多于1次,比如每个cycle的FP操作数量。2021构架扩展引入了一个新的threshold控制,允许软件通过创建直方图来分析这些值的分布。

其他功能

2021构架其他功能包括:

Hinted Conditional Branches 指令 (注:新指令将条件跳转方向作为hint,提高分支预测的命中率)

指针鉴权(Pointer Authentication)采用QARMA3算法 (注:降低QARMA算法难度,从而减少PAC指令的cycle数)

EL0 Implementation Defined的功能可以trap到EL1, EL2

控制EL0的cache maintenance操作

BRBE支持扩展到EL3

总结

这篇博客简要介绍了包含在armv8.8-A和armv9.3-A中的最新功能。

下一步是,我们将和包括Linaro在内我们的生态伙伴,一起使能开源软件,确保当硬件可用时这些功能可以被使用。

原作者:Martin Weidmann

/7

/7